## FEATURES

- SMBus, version 1.0, compliant

- Intel PAS Protected Storage support

- Support Pentium and x86-based designs

- Support SMBus Q-Buffering via PWRGD

- Support SMBus selector for dual/triple DIMMs

- 32KHZ input clock or Crystal input

- Support 2 different power planes

- 10 bytes scratch pad registers

- 20 possible edge-sensitive programmable GPIOs per device

- 8 possible Open Drain, Open Collector outputs

- Programmable addresses for cascaded OZ998s

- Supports 3.3V or 5V operation

- Supports 5V tolerant LVTTL inputs (OZ998B)

- LOW power hardware-driven speaker alarm outputs

- SMBALERT# and SMI event outputs

- 8 programmable interrupt inputs for SMI event or SMBALERT#

- 8 Auto LED Flash (ALF) programmable outputs with 10% or 50% duty cycles

### **ORDERING INFORMATION**

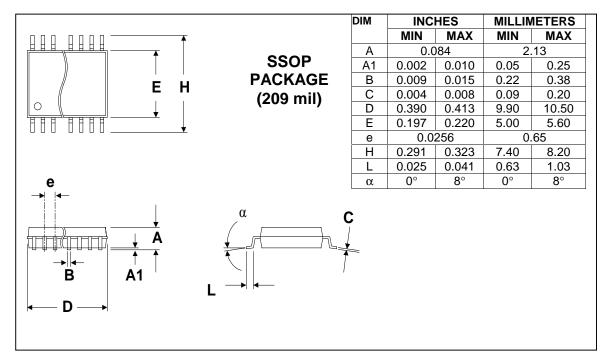

029988 - 28 pin SSOP

# Intelligent Manager Smart Multi-DIMM Selector

### **GENERAL DESCRIPTION**

O<sub>2</sub>Micro's OZ998 Multi-DIMM Selector supports the switching between a primary SMBus and 3 other secondary SMBus. This function is particularly useful for DIMM devices and the support of Intel's PAS (Preboot Authentication Service).

In addition, the OZ998 can be configured to support two different power planes with different sets of General Purpose Input/Output (GPIO) signals, which supplements and enhances the power management capability of the chipsets, commonly found in an ACPI (Advanced Configuration of Power Interface) subsystem.

Up to 20 possible GPIOs are available per device, and among those, GPIO[15:8] are programmable to be either positive or negative-edged triggers to generate an SMIEVENT/SMBALERT# to the system. GPIO[7:0] are programmable to be either a regular TTL level output, open drain or open collector output. To support over 20 GPIOs through cascading multiple OZ998 devices, configure each individual OZ998 device ID. Up to 8 Auto LED Flash (ALF) are available to drive an LED or speaker at a programmable frequency.

The OZ998 is packaged in a low profile, small 28 pin SSOP.

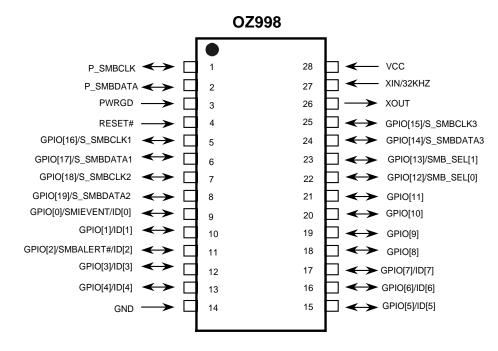

## **PIN DIAGRAM**

# PIN DESCRIPTION

| Name                        | Pin<br>No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Туре                            | Input                | Drive                    | · · · · · · · · · · · · · · · · · · · | Definition                                                                                                                                     |  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|--------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| P_SMBCLK                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                 | 3.3V/5V Ext-PU       | -                        |                                       | Primary SMBus Clock Input                                                                                                                      |  |

| _                           | Primar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | y SMBus Cloc                    | k Input for SMBus pr | otocol con               | nmunicati                             |                                                                                                                                                |  |

| P_SMBDATA                   | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                             | 3.3V/5V Ext-PU       | 12mA                     |                                       | Primary SMBus Data I/O                                                                                                                         |  |

|                             | Primar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | y SMBus Data                    | Input/Output for SM  | Bus proto                | col comm                              | unication.                                                                                                                                     |  |

| PWRGD                       | 3 I TTL - Host System Power Good                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                 |                      |                          |                                       |                                                                                                                                                |  |

|                             | This pin indicates that the host system's power, including the Core Logic chipsets, is stable. Before the host system's power is stable, this input pin will tri-state the output pins, GPO[19:8], from OZ998 while GPO[7:0] will maintain its original value. Upon PWRGD going Low, the Secondary SMBus will be                                                                                                                                                                                                                                                                                                                                                                                   |                                 |                      |                          |                                       |                                                                                                                                                |  |

|                             | discon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nected from th                  | e Primary SMBus.     | -                        |                                       |                                                                                                                                                |  |

| RESET#                      | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I                               | TTL                  | -                        |                                       | Reset                                                                                                                                          |  |

|                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 | ill reset the OZ998. |                          |                                       |                                                                                                                                                |  |

| GPIO[16]/<br>S_SMBCLK1      | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                             | TTL                  | 4mA                      |                                       | General Purpose I/O/<br>Secondary SMBus-1 Clock I/O                                                                                            |  |

|                             | default<br>SMBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ed as an inp<br>s-1 Clock Inp   | ut. It is programmab | le to fund<br>GPIO[19:1  | ction as (<br>6] Config               | edicated or specific functions. Pin GPIO[16] is<br>GPI[16] input, GPO[16] output or secondary<br>g.1&2 Registers for more details and GPIO     |  |

| GPIO[17]/                   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O`                            | TTL '                | 4mA                      |                                       | General Purpose I/O/                                                                                                                           |  |

| S_SMBDATA1                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                 |                      |                          |                                       | Secondary SMBus-1 Data I/O                                                                                                                     |  |

|                             | default<br>SMBus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ed as an inp<br>s-1 Data Input/ | ut. It is programmab | le to fund<br>O[19:16] ( | tion as (                             | edicated or specific functions. Pin GPIO[17] is<br>GPI[17] input, GPO[17] output or secondary<br>2 Registers for more details and GPIO Config. |  |

| GPIO[18]/<br>S_SMBCLK2      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                             | TTL                  | 4mA                      |                                       | General Purpose I/O/<br>Secondary SMBus-2 Clock I/O                                                                                            |  |

|                             | Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[18] is defaulted as an input. It is programmable to function as GPI[18] input, GPO[18] output or secondary SMBus-2 Clock Input/Output. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO Config. Tables (section 8) for input/output selections. Note: OZ998A GPIO [19:18] need 47kΩ pull-up for normal operation, OZ998B doesn't.                                                                                                                                                                                                                                           |                                 |                      |                          |                                       |                                                                                                                                                |  |

| GPIO[19]/<br>S_SMBDATA2     | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                             | TTL                  | 4mA                      |                                       | General Purpose I/O /<br>Secondary SMBus-2 Data I/O                                                                                            |  |

|                             | Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[19] is defaulted as an input. It is programmable to function as GPI[19] input, GPO[19] output or secondary SMBus-2 Data Input/Output. Refer to GPIO[19:16] Config.1&2 Registers for more details and GPIO Config. Tables (section 8) for input/output selections. Note: OZ998A GPIO [19:18] need 47kΩ pull-up for normal operation, OZ998B doesn't.                                                                                                                                                                                                                                            |                                 |                      |                          |                                       |                                                                                                                                                |  |

| GPIO[0]/<br>SMIEVENT/ID[0]  | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I/O                             | TTL                  | 12mA                     |                                       | General Purpose I/O /<br>SMIEVENT                                                                                                              |  |

|                             | Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[0] has<br>an SMIEVENT output as an alternate function. GPIO[0] is set as default. It is also programmable to<br>function as GPI[0] input, GPO[0] output, ALF[0] output, or ID[0] input. In addition, if this pin is configured as<br>output, TTL output, Open Drain or Open collector output can be selected. Refer to GPIO Config.1&2<br>Registers for more details and GPIO Config. Tables (section 8) for input/output selections.                                                                                                                                                          |                                 |                      |                          |                                       |                                                                                                                                                |  |

| GPIO[1]/ID[1]               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                             | TTL                  | 12mA                     |                                       | General Purpose I/O                                                                                                                            |  |

|                             | Fully programmable GPIO that can be used for a variety of dedicated or specific functions. GPIO[1] pin defaults as input. It is also programmable to function as GPI[1] input, GPO[1] output, ALF[1] output, or ID[1] input. In addition, if this pin is configured as output, TTL output, Open Drain or Open collector output can be selected. Refer to GPIO Config. 1&2 Registers for more details and GPIO Config. Tables (section 8) for input/output selections.                                                                                                                                                                                                                              |                                 |                      |                          |                                       |                                                                                                                                                |  |

| GPIO[2]/<br>SMBALERT#/ID[2] | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I/O                             | TTL                  | 12mA                     |                                       | General Purpose I/O/<br>SMBALERT#                                                                                                              |  |

|                             | Fully programmable GPIO that can be used for a variety of dedicated or specific functions. Pin GPIO[2] defaults as input. This pin, when programmed as an alternate function, can generate the SMBALERT# interrupt. SMBALERT# is an interrupt service request signal to the SMBus Host which can be generated by all devices connected to the OZ998. Pin GPIO[2]/SMBALERT# is also programmable to function as GPI[2] input, GPO[2] output, ALF[2] output, or ID[2] input. In addition, if this pin is configured as output, TTL output, Open Drain or Open collector can be selected. Refer to GPIO Config.1&2 Registers for more details and GPIO Config. Tables (section 8) for I/O selections. |                                 |                      |                          |                                       |                                                                                                                                                |  |

| Name                    | Pin No.                                                                                                                                                                                                          | Туре         | Input                              | Drive            |              | Definition                                                         |  |  |  |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------|------------------|--------------|--------------------------------------------------------------------|--|--|--|

| GPIO[7:3]/ID[7:3]       | [17:15],                                                                                                                                                                                                         | Type<br>I/O  | Input<br>TTL                       | 12mA             |              | General Purpose I/Os                                               |  |  |  |

|                         | [13:12]                                                                                                                                                                                                          |              |                                    |                  |              |                                                                    |  |  |  |

|                         | Fully programmable GPIOs that can be used for a variety of dedicated or specific functions. GPIO[7:3] pins                                                                                                       |              |                                    |                  |              |                                                                    |  |  |  |

|                         | default as inputs. They are programmable to function as GPI[7:3] inputs, GPO[7:3] outputs, ALF[7:3] outputs, or ID[7:3] inputs. In addition, if this pin is configured as output, TTL output, Open Drain or Open |              |                                    |                  |              |                                                                    |  |  |  |

|                         | collector can be selected. Refer to GPIO Config.1&2 Registers for more details and GPIO Config. Tables                                                                                                           |              |                                    |                  |              |                                                                    |  |  |  |

|                         | (section 8) for input/output selections.                                                                                                                                                                         |              |                                    |                  |              |                                                                    |  |  |  |

| GPIO[10:8]              | [20:18]                                                                                                                                                                                                          | I/O          |                                    | 4mA              |              | General Purpose I/Os                                               |  |  |  |

|                         |                                                                                                                                                                                                                  | rammable     | GPIOs that ca                      |                  | or a varie   | ty of dedicated or specific functions. Pins                        |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              | are programmable to generate SMI/SMB                               |  |  |  |

|                         | interrupts. They are also programmable to function as GPI[10:8] inputs, GPO[10:8] outputs. Refer to GPIO                                                                                                         |              |                                    |                  |              |                                                                    |  |  |  |

| CDIO[44]                | Config.1&2                                                                                                                                                                                                       |              |                                    |                  | onfig. Tabl  | es (section 8) for input/output selections.<br>General Purpose I/O |  |  |  |

| GPIO[11]                |                                                                                                                                                                                                                  | I/O          | PIO that can h                     | 4mA              | ariety of de | edicated or specific functions. Pin GPIO[11] is                    |  |  |  |

|                         | default as                                                                                                                                                                                                       | input. Pin   | GPIO[11] as in                     | put is program   | imable to    | generate SMI/SMB interrupts. They are also                         |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              | Refer to GPIO Config.1&2 Registers for more                        |  |  |  |

|                         |                                                                                                                                                                                                                  |              | fig. Tables (see                   |                  |              |                                                                    |  |  |  |

| GPIO[12]/<br>SMB_SEL[0] | 22                                                                                                                                                                                                               | I/O          | TTL                                | 4mA              |              | General Purpose I/O /<br>Secondary SMBus Select 0                  |  |  |  |

|                         | Fully prog                                                                                                                                                                                                       | rammable (   | GPIO that can                      | be used for a    | variety o    | f dedicated or specific functions. By default,                     |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              | Secondary SMBus. Pin GPIO[12] default as                           |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              | MI/SMB interrupts. It is also programmable to                      |  |  |  |

|                         |                                                                                                                                                                                                                  |              | put, GPO[12] o<br>n 8) for input/o |                  |              | nfig.1&2 Registers for more details and GPIO                       |  |  |  |

|                         | Coning. Ta                                                                                                                                                                                                       |              |                                    | utput selection: | 5.           |                                                                    |  |  |  |

|                         | SMB_SEL                                                                                                                                                                                                          | .[1:0] S     | Selected Secor                     | ndary SMBus      |              |                                                                    |  |  |  |

|                         | 00<br>01                                                                                                                                                                                                         |              | None<br>Secondary SM               |                  |              |                                                                    |  |  |  |

|                         | 10                                                                                                                                                                                                               |              |                                    |                  |              |                                                                    |  |  |  |

|                         | 10 Secondary SMBus-2   11 Secondary SMBus-3                                                                                                                                                                      |              |                                    |                  |              |                                                                    |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    | 1                |              |                                                                    |  |  |  |

| GPIO[13]/<br>SMB_SEL[1] | 23                                                                                                                                                                                                               | I/O          | TTL                                | 4mA              |              | General Purpose I/O /<br>Secondary SMBus Select 1                  |  |  |  |

|                         | Fully programmable GPIO that can be used for a variety of dedicated or specific functions. On default,                                                                                                           |              |                                    |                  |              |                                                                    |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              | Secondary SMBus. Pin GPIO[13] default as                           |  |  |  |

|                         | input. Pin                                                                                                                                                                                                       | GPIO[13], a  | as input is prog                   | rammable to g    | enerate S    | MI/SMB interrupts. It is also programmable to                      |  |  |  |

|                         | function as GPI[13] input, GPO[13] output. Refer to GPIO Config.1&2 Registers for more details and GPIO Config. Tables (section 8) for input/output selections.                                                  |              |                                    |                  |              |                                                                    |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  | S.           | Conorol Durnoso I/O /                                              |  |  |  |

| GPIO[14]/<br>S_SMBDATA3 | 24                                                                                                                                                                                                               | I/O          | TTL                                | 4mA              | · ·          | General Purpose I/O /<br>Secondary SMBus-3 Data I/O                |  |  |  |

|                         | Fully prog                                                                                                                                                                                                       | rammable (   | GPIO that can I                    | be used for a v  | variety of   | dedicated or specific functions. Pin GPIO[14]                      |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              | to generate SMI/SMB interrupts. It is also                         |  |  |  |

|                         | programm                                                                                                                                                                                                         | able to fund | ction as GPI[14                    | 4] input, GPO[   | 14] output   | s or secondary SMBus-3 Data Input/Output.                          |  |  |  |

|                         |                                                                                                                                                                                                                  |              | .1&2 Registers                     | for more detail  | ils and GF   | PIO Config. Tables (section 8) for input/output                    |  |  |  |

| CPIO(45)/               | selections                                                                                                                                                                                                       |              | <b>T</b> TI                        | 4~^              |              | General Burnass 1/0 /                                              |  |  |  |

| GPIO[15]/<br>S_SMBCLK3  | 25                                                                                                                                                                                                               | I/O          | TTL                                | 4mA              |              | General Purpose I/O /<br>Secondary SMBus-3 Clock I/O               |  |  |  |

| 0_0                     | Fully prog                                                                                                                                                                                                       | rammable (   | SPIO that can I                    | be used for a v  | varietv of   | dedicated or specific functions. Pin GPIO[15]                      |  |  |  |

|                         | default as                                                                                                                                                                                                       | input. Pin   | GPIO[15], as                       | input is progr   | rammable     | to generate SMI/SMB interrupts. It is also                         |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              | t or secondary SMBus-3 Clock Input/Output.                         |  |  |  |

|                         |                                                                                                                                                                                                                  |              | .1&2 Registers                     | for more detai   | ils and GF   | PIO Config. Tables (section 8) for input/output                    |  |  |  |

| XOUT                    | selections                                                                                                                                                                                                       | 0            |                                    |                  |              | XOUT Output                                                        |  |  |  |

| 7001                    | 26<br>Crystal ou                                                                                                                                                                                                 |              | e application di                   |                  |              |                                                                    |  |  |  |

| XIN/32KHZ               | 27                                                                                                                                                                                                               |              | TTL                                |                  |              | XIN Input/32KHZ                                                    |  |  |  |

|                         |                                                                                                                                                                                                                  | out clock so |                                    | put pin as alter | nate. See    | application diagram on p.18.                                       |  |  |  |

| GND                     | 14                                                                                                                                                                                                               | GND          | -                                  | -                |              | Ground                                                             |  |  |  |

|                         | Ground.                                                                                                                                                                                                          |              | 1                                  |                  |              |                                                                    |  |  |  |

| VCC                     | 28                                                                                                                                                                                                               | PWR          | -                                  | -                |              | 3.3V/5V Power Supply                                               |  |  |  |

|                         | 3.3V or 5V                                                                                                                                                                                                       | Power Sup    | oply.                              | •                |              |                                                                    |  |  |  |

|                         |                                                                                                                                                                                                                  |              |                                    |                  |              |                                                                    |  |  |  |

# DC CHARACTERISTICS

### DC TABLE FOR VCC = 5.0V $\pm$ 10%

| Symbol          | Parameter                     | Min | Max | Units |

|-----------------|-------------------------------|-----|-----|-------|

| Vcc             | Power Supply Voltage          | 4.5 | 5.5 | V     |

| VIH             | Input HIGH Voltage            | 2.0 | -   | V     |

| VII             | Input LOW Voltage             | -   | 0.8 | V     |

| V <sub>OH</sub> | Output HIGH Voltage           | 2.4 | -   | V     |

| Vol             | Output LOW Voltage            | -   | 0.4 | V     |

| II.             | Maximum Input Leakage Current | -10 | 10  | μA    |

| I <sub>OL</sub> | Maximum Output Leakage        | -10 | 10  | μA    |

#### DC TABLE FOR VCC = $3.3V \pm 10\%$

| Symbol          | Parameter                     | Min | Max | Units |

|-----------------|-------------------------------|-----|-----|-------|

| Vcc             | Power Supply Voltage          | 3.0 | 3.6 | V     |

| VIH             | Input HIGH Voltage            | 2.0 | -   | V     |

| VII             | Input LOW Voltage             | -   | 0.8 | V     |

| V <sub>он</sub> | Output HIGH Voltage           | 2.4 | -   | V     |

| V <sub>oL</sub> | Output LOW Voltage            | -   | 0.4 | V     |

| IL              | Maximum Input Leakage Current | -10 | 10  | μΑ    |

| I <sub>o∟</sub> | Maximum Output Leakage        | -10 | 10  | μΑ    |

#### CAPACITANCE

| Symbol          | Parameter                  | 0 °C to 70°C | Units |

|-----------------|----------------------------|--------------|-------|

| CIN             | Maximum Input Capacitance  | 10           | pF    |

| Cout            | Maximum Output Capacitance | 10           | pF    |

| C <sub>IO</sub> | Maximum I/O Capacitance    | 10           | pF    |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                                   | Value                         | Units |

|------------------|---------------------------------------------|-------------------------------|-------|

| V <sub>cc</sub>  | DC Power Supply Voltage                     | -0.3 to 5.5                   | V     |

| VIN, VOUT        | DC Input, Output Voltage                    | -0.3 to V <sub>CC</sub> + 0.3 | V     |

| I <sub>IN</sub>  | DC Current Drain $V_{CC}$ and $V_{CC}$ Pins | ±25                           | mA    |

| T <sub>STG</sub> | Storage Temperature                         | -40 to +125                   | °C    |

|                  | Operation Temperature                       | 0 to 70                       | °C    |

#### I<sub>CC</sub> SPECIFICATIONS

| Symbol            | Parameter                                                                                        | Тур | Max | Units |

|-------------------|--------------------------------------------------------------------------------------------------|-----|-----|-------|

| Icc5v             | Supply Current, $V_{CC} = 5V$ (when 32KHZ input clock source is used)                            | 8   | 15  | μA    |

| I <sub>CC3V</sub> | Supply Current, $V_{CC} = 3.3V$<br>(when 32KHZ input clock source<br>is used)                    | 5   | 10  | μA    |

| I <sub>CC5V</sub> | Supply Current, $V_{CC} = 5V$ (when<br>external OSC is used based on<br>configuration on p.18)   | 150 | 200 | μA    |

| I <sub>CC3V</sub> | Supply Current, $V_{CC} = 3.3V$<br>(when external OSC is used<br>based on configuration on p.18) | 50  | 80  | μA    |

### **13. OZ998 PACKAGE INFORMATION**