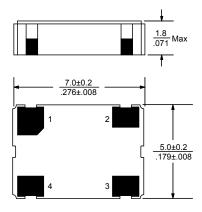

#### Actual Size $= 5 \times 7$ mm

#### **Product Features**

- Less than 1 ps RMS jitter with advanced non-PLL, patent-pending design

- 2.5V CMOS/TTL compatible logic levels

- Pin-compatible with standard 5x7mm packages

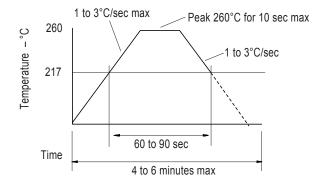

- Designed for standard reflow and washing techniques

- Pb-free and RoHS/Green compliant

# **Product Description**

The \$1614XP Series is an enhanced high-frequency version of the popular \$1614 series, a 2.5V crystal clock oscillator that achieves superb jitter and stability over a broad range of operating conditions and frequencies. The output clock signal, generated internally with a non-PLL oscillator design, is compatible with LVCMOS/LVTTL logic levels. The device, available on tape and reel, is contained in a 5x7mm surface-mount ceramic package.

# **Applications**

The \$1614XP Series is an ideal reference clock for highspeed applications requiring low jitter, including:

- 1/10 Gigabit Ethernet

- FibreChannel

- Serial Attached SCSI (SAS)

- Server & Storage platforms

- SONET/SDH linecards

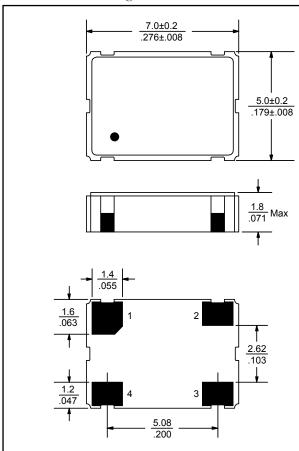

### **Packaging Outline**

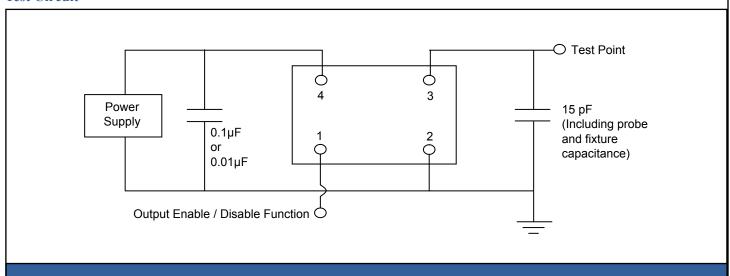

#### **Pin Functions**

| Pin | Function     |

|-----|--------------|

| 1   | OE Function  |

| 2   | Ground       |

| 3   | Clock Output |

| 4   | $V_{DD}$     |

# **Common Frequencies**

Contact SaRonix for additional frequencies

| 100.0000 MHz | 150.0000 MHz |

|--------------|--------------|

| 106.2500 MHz | 155.5200 MHz |

| 125.0000 MHz | 156.2500 MHz |

| 127.0000 MHz | 159.3750 MHz |

| 133.0000 MHz |              |

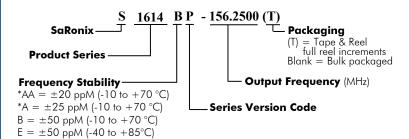

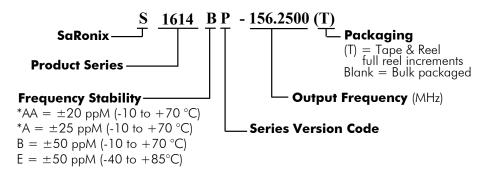

#### **Ordering Information**

<sup>\*</sup> Availability varies by frequency. Please consult SaRonix.

#### **Electrical Performance**

| Parameter             | Min.                   | Тур.                    | Max.                   | Units           | Notes                         |

|-----------------------|------------------------|-------------------------|------------------------|-----------------|-------------------------------|

| Output frequency      | 100                    |                         | 160                    | MHz             | As specified                  |

| Supply voltage        | +2.38                  | +2.5                    | +2.62                  | V               |                               |

| Supply current        |                        |                         | 25                     | mA              | Output enabled                |

| Supply current        |                        |                         | 10                     | mA              | Output Hi-Z                   |

| Frequency stability   | ±20                    |                         | ±100                   | ppM             | See Note 1 below              |

| Operating temperature | -40                    |                         | +85                    | °C              | As specified                  |

| Output logic 0, VOL   |                        |                         | 10%<br>V <sub>DD</sub> | V               |                               |

| Output logic 1, VOH   | 90%<br>V <sub>DD</sub> |                         |                        | v               |                               |

| Output load           | 15                     | 15 pF (max) or 10 LSTTL |                        | TL              |                               |

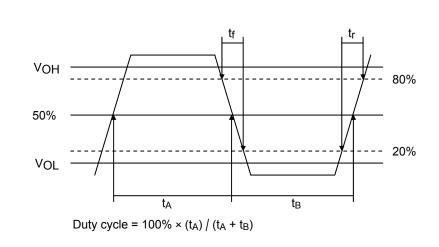

| Duty cycle            | 45                     |                         | 55                     | %               | -10 to +70°C measured 50%VDD  |

| Duty cycle            | 40                     |                         | 60                     | %               | -40 to +85°C measured 50%VDD  |

| Rise and fall time    |                        |                         | 2                      | ns              | measured 20/80% of waveform   |

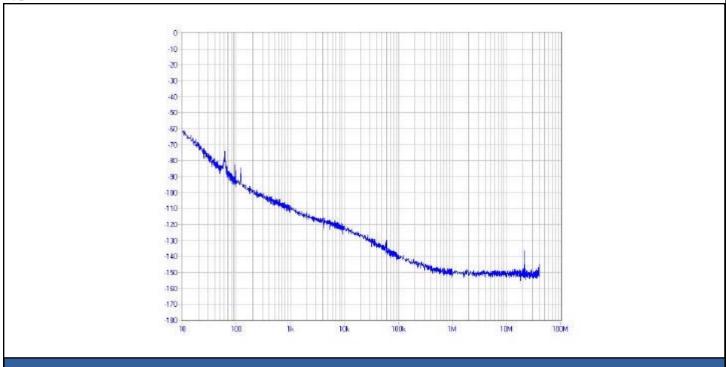

| Jitter, phase         |                        |                         | 1                      | ps RMS<br>(1-σ) | 10kHz to 20MHz frequency band |

| Jitter, accumulated   |                        |                         | 7                      | ps RMS<br>(1-σ) | 20,000 adjacent periods       |

| Jitter, total         |                        |                         | 40                     | ps<br>pk-pk     | 100,000 random periods        |

| Subharmonic Level     |                        |                         | -40                    | dBc             |                               |

#### **Notes:**

### **Output Enable / Disable Function**

| Parameter                                | Min. | Тур. | Max. | Units | Notes          |

|------------------------------------------|------|------|------|-------|----------------|

| Input Voltage (pin 1), Output<br>Enable  | 2.2  |      |      | V     |                |

| Input voltage (pin 1), Output<br>Disable |      |      | 0.8  | V     | Output is Hi-Z |

| Internal pullup resistance               | 50   |      |      | kΩ    |                |

| Output disable delay                     |      |      | 100  | ns    |                |

| Output enable delay                      |      |      | 1    | ms    |                |

<sup>1.</sup> As specified. Stability includes all combinations of operating temperature, load changes, rated input (supply) voltage changes, initial calibration tolerance (25°C), aging (1 year at 25°C average effective ambient temperature), shock and vibration.

# **Typical Phase Noise**

# **Absolute Maximum Ratings**

| Parameter           | Min. | Тур. | Max. | Units | Notes |

|---------------------|------|------|------|-------|-------|

| Storage temperature | -55  |      | +125 | °C    |       |

#### **Test Circuit**

### **Reliability Test Ratings**

This product is rated to meet the following test conditions:

| Туре          | Parameter                    | Test Condition                                                       |

|---------------|------------------------------|----------------------------------------------------------------------|

| Mechanical    | Shock                        | MIL-STD-883, Method 2002, Condition B                                |

| Mechanical    | Solderability                | MIL-STD-883, Method 2003                                             |

| Mechanical    | Terminal strength            | MIL-STD-883, Method 2004, Condition D                                |

| Mechanical    | Gross leak                   | MIL-STD-883, Method 1014, Condition C                                |

| Mechanical    | Fine leak                    | MIL-STD-883, Method 1014, Condition A2 ( $R_1 = 2x10^{-8}$ atm cc/s) |

| Mechanical    | Solvent resistance           | MIL-STD-202, Method 215                                              |

| Environmental | Thermal shock                | MIL-STD-883, Method 1011, Condition A                                |

| Environmental | Moisture resistance          | MIL-STD-883, Method 1004                                             |

| Environmental | Vibration                    | MIL-STD-883, Method 2007, Condition A                                |

| Environmental | Resistance to soldering heat | MIL-STD-202, Method 210, Condition I or J                            |

# **Output Waveform**

# **Reflow Soldering Profile**

### As per IPC/JEDEC J-STD-020C

5

#### **Mechanical Drawings**

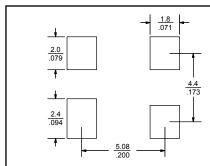

# **Recommended Land Pattern\***

\*External high-frequency power decoupling is recommended.(see test circuit for minimum recommendation). To ensure optimal performance, do not route traces beneath the package.

Scale: None. Dimensions are in mm/inches.

Marking LINE 1: S P X P (SaRonix, Model, Stability code, Version)

Marking LINE 2: Frequency (Frequency code)

Marking LINE 3: ● YY WW X (Pin 1, Year, Week, Origin)

\*\*Exact location of markings may vary.

### **Ordering Information**

<sup>\*</sup> Availability varies by frequency. Please consult SaRonix.