# 1/6-Inch VGA CMOS Digital Image Sensor

# PART NUMBER: MT9V012

## Features

- DigitalClarity<sup>™</sup> CMOS Imaging Technology

- High frame rate

- Superior low-light performance

- Low dark current

- Simple two-wire serial interface

- Auto black level calibration

- Operating Modes: Snapshot and flash control, high frame rate preview, electronic panning

- Programmable Controls: Gain, frame size/rate, exposure, left-right and top-bottom image reversal, window size, and panning

- Data Interfaces: parallel and low-voltage differential signaling (LVDS)

- Applications

- Cellular Phones

- PC Cameras

- PDAs

- Toys and other battery-powered products

## **General Description**

The Micron<sup>®</sup> Imaging MT9V012 is an oversize VGAformat CMOS active-pixel digital image sensor with a pixel array of 649H x 489V. It incorporates sophisticated on-chip camera functions such as windowing, mirroring, column and row skip modes, and snapshot mode. It is programmable through a simple two-wire serial interface and has very low power consumption.

The VGA CMOS image sensor features DigitalClarity— Micron's breakthrough low-noise CMOS imaging technology that achieves CCD image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, and integration advantages of CMOS.

## Table 1: Key Performance Parameters

| Parameter          |              | Typical Value                    |  |

|--------------------|--------------|----------------------------------|--|

| Optical Format     |              | 1/6-inch VGA (4:3)               |  |

| Active In          | nager Size   | 2.30mm(H) x 1.77mm(V),           |  |

|                    |              | 2.88mm Diagonal                  |  |

| Active Pi          | xels         | 640H x 480V                      |  |

| Pixel Size         | <del>Ĵ</del> | 3.6µm x 3.6µm                    |  |

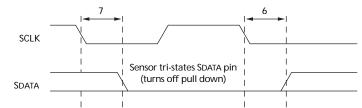

| Color Fil          | ter Array    | RGB Bayer Pattern                |  |

| Shutter -          | Гуре         | Electronic Rolling Shutter (ERS) |  |

| Maximu             | m Data Rate/ | 13.5 MPS/27 MHz                  |  |

| Master C           | lock         |                                  |  |

| Frame              | VGA          | Programmable up to 30 fps        |  |

| Rate               | (640 x 480)  |                                  |  |

|                    | CIF          | Programmable up to 60 fps        |  |

|                    | (352 x 288)  |                                  |  |

| ADC Res            | olution      | 10-bit, on-chip                  |  |

| Respons            | ivity        | 1.0 V/lux-sec (550nm)            |  |

| Dynamic            | Range        | >71dB                            |  |

| SNR <sub>MAX</sub> |              | 44dB                             |  |

| Supply             | Analog       | 2.50V-3.10V (2.80V nominal)      |  |

| Voltage            | I/O and      | 1.70V–1.90V (1.80V nominal) or   |  |

|                    | Digital      | 2.50V-3.10V (2.80V nominal)      |  |

| Power Consumption  |              | <55mW at 2.8V, 27 MHz,           |  |

|                    |              | 30 fps and VGA resolution        |  |

| Operating          |              | -30°C to +70°C                   |  |

| Temperature        |              |                                  |  |

When operated in its default mode, the sensor generates a VGA image at 30 frames per second (fps). An onchip analog-to-digital converter (ADC) generates a 10bit value for each pixel. The pixel data is output on a 10-bit output bus and qualified by an output data clock (PIXCLK), together with LINE\_VALID and FRAME\_VALID signals. A FLASH output strobe is provided to allow an external Xenon or LED light source to synchronize with the sensor exposure time. The sensor can be programmed by the user to control the frame size, exposure, gain setting and other parameters.

PDF: 814eb99f/Source: 8175e929 MT9V012\_1.fm - Rev. B 2/05 EN 1

Micron Technology, Inc., reserves the right to change products or specifications without notice. ©2004 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by Micron without notice. Products are only warranted by Micron to meet Micron's production data sheet specifications.

# MT9V012 - 1/6-Inch VGA CMOS Digital Image Sensor Table of Contents

## **Table of Contents**

| Features                                                  |     |

|-----------------------------------------------------------|-----|

| General Description                                       |     |

| Functional Overview                                       |     |

| Operating Modes                                           |     |

| Default Mode                                              | 7   |

| Serial Mode                                               |     |

| Pixel Array Structure                                     | 9   |

| Default Readout Order                                     |     |

| Output Data Format (Default Mode)                         | .10 |

| Output Data Timing (Default Mode)                         | .11 |

| Output Data Format (Serial Mode)                          | .13 |

| Output Data Timing (Serial Mode)                          | .13 |

| Two-Wire Serial Interface                                 |     |

| Protocol                                                  | .15 |

| Sequence                                                  |     |

| Bus Idle State                                            |     |

| Start Bit                                                 |     |

| Stop Bit                                                  |     |

| Slave Address.                                            |     |

| Data Bit Transfer.                                        |     |

| Acknowledge Bit                                           |     |

| No-Acknowledge Bit                                        |     |

| Page Register                                             |     |

| Two-Wire Serial Interface Sample Write and Read Sequences |     |

| 16-Bit Write Sequence.                                    |     |

| 16-Bit Read Sequence                                      |     |

| 8-Bit Write Sequence                                      |     |

|                                                           |     |

| 8-Bit Read Sequence                                       |     |

| Registers                                                 |     |

| Register Description                                      |     |

| Double-Buffered Registers                                 |     |

| Bad Frames.                                               |     |

| Changes to Integration Time                               |     |

| Changes to Gain Settings                                  |     |

| Feature Description                                       |     |

| Window Control                                            |     |

| Window Start                                              |     |

| Window Size                                               |     |

| Pixel Border                                              |     |

| Context Switching                                         |     |

| Readout Modes                                             |     |

| Column Mirror Image                                       |     |

| Row Mirror Image                                          | .33 |

| Column and Row Skip                                       | .33 |

| Digital Zoom                                              | .34 |

| Frame Rate Control                                        | .35 |

| Minimum Horizontal Blanking                               | .35 |

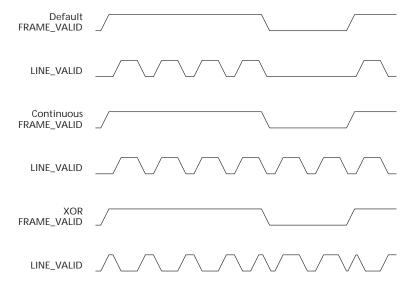

| Valid Data Signals Options.                               | .36 |

| LINE_VALID Signal                                         |     |

| Integration Time.                                         |     |

| Maximum Shutter Delay                                     |     |

| •                                                         |     |

# MT9V012 - 1/6-Inch VGA CMOS Digital Image Sensor Table of Contents

|                                                  | 07 |

|--------------------------------------------------|----|

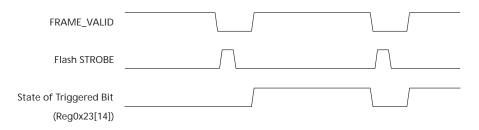

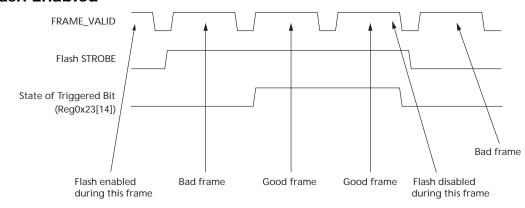

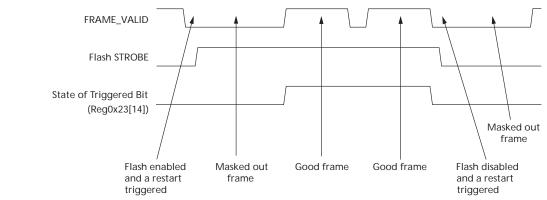

| Flash Strobe                                     |    |

| Analog Signal Path                               |    |

| Stage-by-Stage Transfer Functions                | 39 |

| VREFD                                            | 39 |

| Gain Settings: G1, G2, G3                        | 39 |

| Offset Voltage: VOFFSET                          |    |

| Recommended Gain Settings                        |    |

| Black Level Calibration                          |    |

| Row-Wise Noise Cancellation                      |    |

| Digital Signal Path                              | 41 |

| Output Enable Control                            |    |

| Power Saving Modes                               |    |

| Floating Inputs                                  | 42 |

| Dark Row/Column Display                          | 43 |

| Clock Control                                    |    |

| Electrical Specifications                        | 45 |

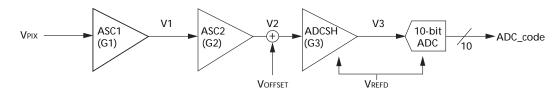

| Propagation Delay for FRAME_VALID and LINE_VALID |    |

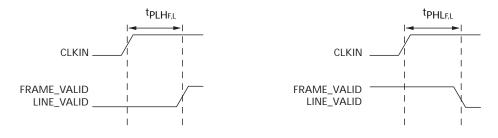

| Propagation Delay for PIXCLK and DOUT            |    |

| Two-wire Serial Bus Timing                       |    |

| Mechanical Specifications                        |    |

| Data Sheet Designation                           | 52 |

| Revision History.                                | 53 |

|                                                  |    |

## **List of Figures**

| Block Diagram                                                      |               |

|--------------------------------------------------------------------|---------------|

| Typical Configuration: Default Mode                                | 7             |

| Typical Configuration: Serial Mode                                 | 8             |

| Pixel Array                                                        | 9             |

| Pixel Color Pattern Detail (Top Right Corner)                      | 9             |

| Imaging a Scene                                                    | 0             |

| Spatial Illustration of Image Readout1                             | 0             |

| Pixel Data Timing Example1                                         | 1             |

| Row Timing and FRAME_VALID/LINE_VALID Signals1                     | 1             |

| Start of Frame: Serial Mode                                        | 3             |

|                                                                    |               |

| Timing Diagram Showing a Write to Reg0x09, Value 0x02841           | 7             |

| Timing Diagram Showing a Read from Reg0x09; Returned Value 0x02841 | 7             |

| Timing Diagram Showing a Write to Reg0x09, Value 0x0284            | 8             |

| Timing Diagram Showing a Read from Reg0x09; Returned Value 0x0284  | 8             |

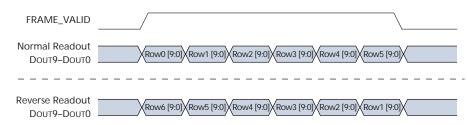

| Six Pixels in Normal and Column Mirror Readout Modes               | 3             |

|                                                                    |               |

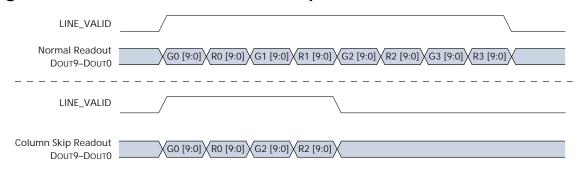

| Eight Pixels in Normal and Column Skip 2X Readout Modes            | 4             |

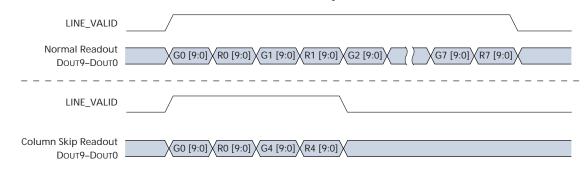

| Sixteen Pixels in Normal and Column Skip 4X Readout Modes          | 4             |

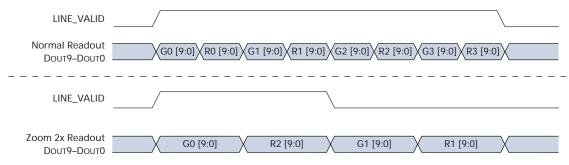

| Eight Pixels in Normal and Zoom 2X Readout Modes                   | 4             |

|                                                                    |               |

| Xenon Flash Enabled                                                | 7             |

| LED Flash Enabled                                                  | 8             |

| LED Flash Enabled Following Forced Restart                         | 8             |

| Analog Signal Path                                                 | 8             |

|                                                                    |               |

| Propagation Delays for PIXCLK and DOUT Signals4                    | 9             |

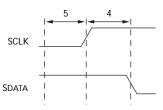

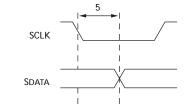

| Serial Host Interface Start Condition Timing                       | 0             |

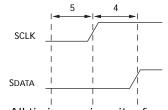

| Serial Host Interface Stop Condition Timing                        | 0             |

| Serial Host Interface Data Timing for Write                        | 0             |

| Serial Host Interface Data Timing for Read                         | 0             |

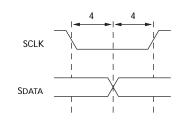

| Acknowledge Signal Timing After an 8-Bit Write to the Sensor       | 1             |

| Acknowledge Signal Timing After an 8-Bit Read from the Sensor      | 1             |

|                                                                    |               |

| Image Center Offset                                                | 2             |

|                                                                    | Block Diagram |

## **List of Tables**

| Table 1:  | Key Performance Parameters                 | .1 |

|-----------|--------------------------------------------|----|

| Table 2:  | Functional Mode Selection.                 |    |

| Table 3:  | Frame Time                                 | 12 |

| Table 4:  | Frame—Long Integration Time                | 12 |

| Table 5:  | Register List and Default Value            |    |

| Table 6:  | Register Description                       | 23 |

| Table 7:  | Offset Gain                                | 40 |

| Table 8:  | Recommended Gain Settings                  | 40 |

| Table 9:  | Output Enable Control                      | 41 |

| Table 10: | Signal State During Standby                | 42 |

| Table 11: | On-chip Pull-ups/Pull-downs                | 43 |

| Table 12: | DC Electrical Characteristics: 2.50V-3.10V | 45 |

| Table 13: | DC Electrical Characteristics: 1.70V-1.90V | 46 |

| Table 14: | AC Electrical Characteristics: 2.50V-3.10V | 47 |

| Table 15: | AC Electrical Characteristics: 1.70V-1.90V | 48 |

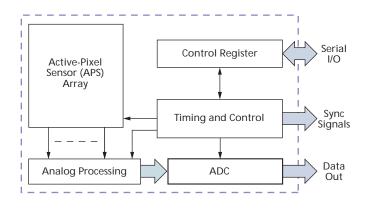

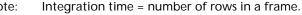

#### Figure 1: Block Diagram

## **Functional Overview**

The MT9V012 is a progressive-scan sensor that generates a stream of pixel data qualified by LINE\_VALID and FRAME\_VALID signals. It uses an input master clock of 27 MHz (nominal). The data rate (pixel clock) is one half of the master clock frequency, which means that one pixel is generated every two master clock cycles. Figure 1 shows the sensor block diagram.

The core of the sensor is an active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in that row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an ADC. The output from the ADC is a 10-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further offset correction, applies digital gain, and may perform pixel defect correction).

The pixel array contains optically active and light shielded ("black") pixels. The black pixels are used to provide data for on-chip offset correction algorithms ("black level" control).

The sensor contains a set of 16-bit control and status registers that can be used to control many aspects of the sensor behavior. These registers can be accessed through a twowire serial interface. In this document, registers are specified either by name (e.g., column start) or by register address (e.g., Reg0x04). Fields within a register are specified by bit or by bit range (e.g., Reg0x20[0] or Reg0x0B[13:0]). Table 6, Register Description, on page 23, describes the control and status registers.

The output from the sensor is a Bayer pattern: alternate rows are a sequence of either green/red pixels or blue/green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

The MT9V012 supports two different functional modes of operation:

- Default mode: the sensor generates a VGA-sized image by default, with 10 parallel data outputs per pixel, and separate LINE\_VALID, FRAME\_VALID, and PIXCLK outputs. All timing control is performed on-chip.

- Serial mode: the sensor generates a VGA-sized image by default. Pixel data, LINE\_VALID, and FRAME\_VALID are encoded into a single serial data stream that uses a two-signal low-voltage differential signalling (LVDS) interface. All timing control is performed on-chip.

# **Operating Modes**

The functional operating mode of the MT9V012 is controlled by the MODE1 and MODE0 inputs (Table 2). These inputs should be driven to a static logic 1 or static logic 0 level during normal operation.

## Table 2: Functional Mode Selection

| Mode1 | Mode0 | Description          |  |

|-------|-------|----------------------|--|

| 0     | 0     | Selects default mode |  |

| 0     | 1     | Selects serial mode  |  |

| 1     | 0     | Not used             |  |

| 1     | 1     | Not used             |  |

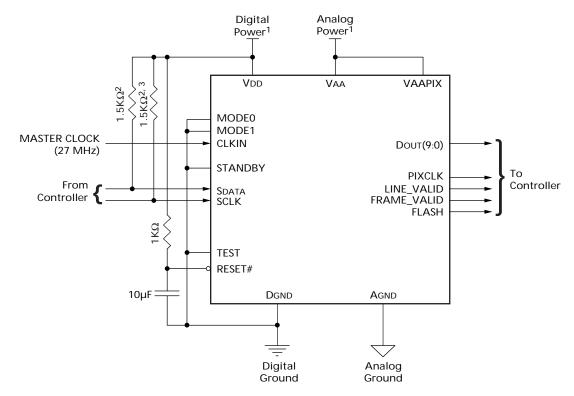

#### **Default Mode**

This section shows a typical configuration schematic for the MT9V012 operating in default mode.

#### Figure 2: Typical Configuration: Default Mode

Notes: 1. All power supplies should be adequately decoupled.

- 2. Resistor value  $1.5K\Omega$  is recommended, but may be greater for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

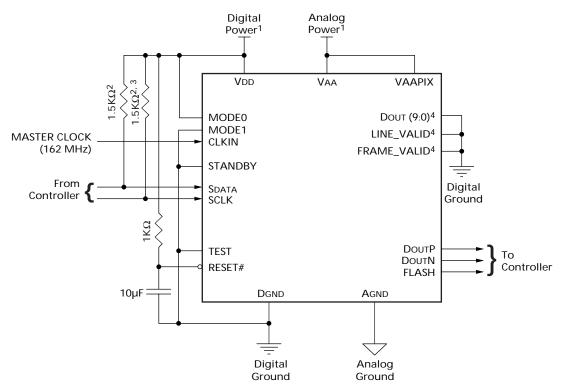

#### Serial Mode

This section shows a typical configuration schematic, including the ball diagram and ball description, for the MT9V012 operating in serial mode. This mode operates only at 2.5V to 3.1V VDD range.

- Notes: 1. All power supplies should be adequately decoupled.

- 2. Resistor value  $1.5K\Omega$  is recommended, but may be greater for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 4. Connect to digital ground directly or through a 10K resistor. Some of these signals have on-die pull-down resistors in this mode and could be left unconnected.

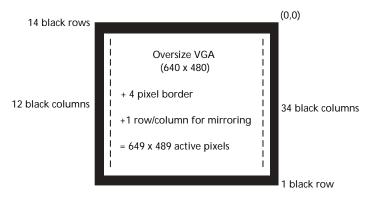

## **Pixel Array Structure**

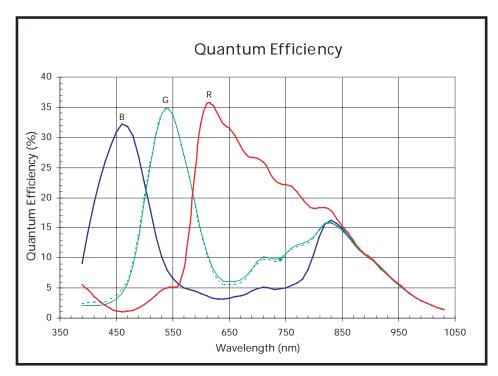

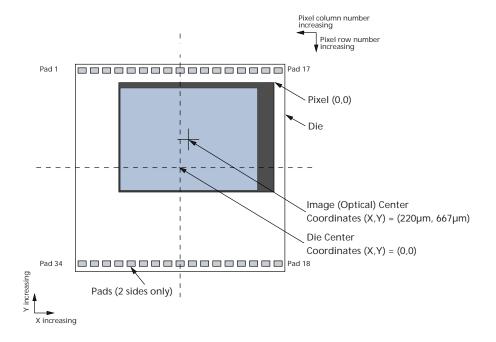

The MT9V012 pixel array is configured as 695 columns by 504 rows (shown in Figure 4). The first 34 columns and the first 14 rows of pixels are optically black, and are used for the automatic black level adjustment ("Black Level Calibration" on page 40). The last 12 columns and the last row of pixels are also optically black. The optically active pixels are used as follows:

A VGA image (640 columns by 480 rows) is generated, starting at row 18, column 38. A four-pixel boundary of active pixels can be enabled around the image to avoid boundary effects during color interpolation and correction. An additional row and column of active pixels is also provided for use during horizontally- and/or vertically mirrored readout. During mirrored readout, the region of active pixels that is used to generate the image is offset by one pixel in each mirrored direction so that the readout always starts on the same color pixel.

## Figure 4: Pixel Array

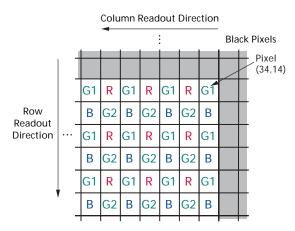

The MT9V012 uses a Bayer color pattern, as shown in Figure 5. The even-numbered rows contain green and red color pixels; odd-numbered rows contain blue and green color pixels. Even-numbered columns contain green and blue color pixels; odd-numbered columns contain red and green color pixels.

## Figure 5: Pixel Color Pattern Detail (Top Right Corner)

#### **Default Readout Order**

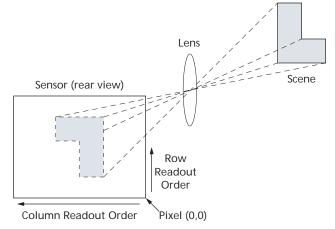

By convention, the MT9V012 pixel array is shown with pixel (0,0) in the top right-hand corner (see Figure 5). This reflects the actual layout of the array on the die. When the sensor is imaging, the active surface of the sensor faces the scene, as shown in Figure 6. When the image is read out of the sensor, it is read one row at a time, with the rows and columns sequenced as shown in Figure 5. By convention, data from the sensor is shown with the first pixel read out—pixel (34,14) in the case of the MT9V012—in the top left-hand corner (Figure 7).

#### Figure 6: Imaging a Scene

# **Output Data Format (Default Mode)**

The MT9V012 image data is read out in a progressive scan. In default mode, valid image data is surrounded by horizontal blanking and vertical blanking, as shown in Figure 7. The amount of horizontal blanking and vertical blanking is programmable; LINE\_VALID is HIGH during the shaded region of the figure. FRAME\_VALID timing is described in the next section.

#### Figure 7: Spatial Illustration of Image Readout

| $\begin{array}{c} P_{0,0} \ P_{0,1} \ P_{0,2}P_{0,n-1} \ P_{0,n} \\ P_{1,0} \ P_{1,1} \ P_{1,2}P_{1,n-1} \ P_{1,n} \end{array}$                        | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| VALID IMAGE                                                                                                                                            | HORIZONTAL<br>BLANKING                 |

| P <sub>m-1,0</sub> P <sub>m-1,1</sub> P <sub>m-1,n-1</sub> P <sub>m-1,n</sub><br>P <sub>m,0</sub> P <sub>m,1</sub> P <sub>m,n-1</sub> P <sub>m,n</sub> | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

| 00 00 00 00 00 00 00 00 00 00 00 0                                                                                                                     | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

| VERTICAL BLANKING                                                                                                                                      | VERTICAL/HORIZONTAL<br>BLANKING        |

| 00 00 0000 00 00<br>00 00 0000 00 00                                                                                                                   | 00 00 00 00 00 00<br>00 00 00 00 00 00 |

#### MT9V012 - 1/6-Inch VGA CMOS Digital Image Sensor Output Data Format (Default Mode)

#### Output Data Timing (Default Mode)

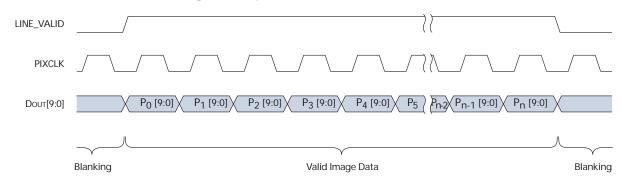

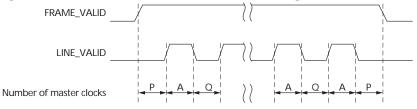

The MT9V012 output data is synchronized with the PIXCLK output. When LINE\_VALID is HIGH, one pixel datum is output on the 10-bit DOUT output every PIXCLK period. By default, the PIXCLK signal runs at one-half the frequency of the master clock, CLKIN, and its rising edges occur one-half of a master clock period after transitions on LINE\_VALID, FRAME\_VALID, and DOUT (see Figure 8). This allows PIXCLK to be used as a clock to sample the data. PIXCLK is continuously enabled, even during the blanking period. The MT9V012 can be programmed to delay the PIXCLK edge relative to the DOUT transitions from 0 to 3.5 master clocks, in steps of one-half of a master clock. This can be achieved by programming the corresponding bits in Reg0x0A. The parameters P, A, and Q in Figure 9 are defined in Table 3 on page 12.

Figure 8: Pixel Data Timing Example

#### Figure 9: Row Timing and FRAME\_VALID/LINE\_VALID Signals

Preliminary<sup>‡</sup>

#### Table 3: Frame Time

| Parameter     | Name                         | Equation                                                               | Default Timing<br>at 27 MHz                           |

|---------------|------------------------------|------------------------------------------------------------------------|-------------------------------------------------------|

| HBLANK_REG    | Horizontal Blanking Register | Reg0x07 if Reg0xC8[0] = 0<br>Reg0x05 if Reg0xC8[0] = 1                 | 0xF4 = 244 pixels                                     |

| VBLANK_REG    | Vertical Blanking Register   | Reg0x8 if Reg0xC8[1] = 0<br>Reg0x6 if Reg0xC8[1] = 1                   | 0x1D = 29 rows                                        |

| PIXCLK_PERIOD | Pixel Clock Period           | Reg0x0A[2:0] * 2                                                       | 1 pixel clock<br>= 2 master<br>= 37.04ns              |

| S             | Skip Factor                  | For skip 2x mode: S = 2<br>For skip 4x mode: S = 4<br>otherwise, S = 1 | 1                                                     |

| A             | Active Data Time             | (Reg0x04/S) * PIXCLK_PERIOD                                            | 640 pixel clocks<br>= 1,280 master<br>= 47.41µs       |

| Ρ             | Frame Start/End Blanking     | 6 * PIXCLK_PERIOD                                                      | 6 pixel clocks<br>= 12 master<br>= 0.44µs             |

| Q             | Horizontal Blanking          | HBLANK_REG * PIXCLK_PERIOD                                             | 244 pixel clocks<br>= 488 master<br>= 18.07µs         |

| A + Q         | Row Time                     | ((Reg0x04/S) + HBLANK_REG) * PIXCLK_PERIOD                             | 884 pixel clocks<br>= 1,768 master<br>= 65.48µs       |

| V             | Vertical Blanking            | VBLANK_REG * (A + Q) + (Q - 2*P)                                       | 25,868 pixel clocks<br>= 51,736 master<br>= 1.91ms    |

| Nrows * (A+Q) | Frame Valid Time             | (Reg0x03/S) * (A + Q) - (Q - 2*P)                                      | 424,088 pixel clocks<br>= 848,176 master<br>= 31.41ms |

| F             | Total Frame Time             | ((Reg0x03/S) + VBLANK_REG) * (A + Q)                                   | 449,956 pixel clocks<br>= 899,912 master<br>= 33.33ms |

The sensor timing (Table 3) is shown in terms of pixel clock and master clock cycles (see Figure 8 on page 11). The recommended master clock frequency is 27 MHz. The vertical blanking and total frame time equations assume that the number of integration rows (Reg0x09) is less than the number of active rows, plus blanking rows (Reg0x03 + VBLANK\_REG). If this is not the case, the number of integration rows must be used instead, to determine the frame time, as shown in Table 4.

#### Table 4: Frame—Long Integration Time

| Parameter | Name                                      | Equation (master clock)                        | Default Timing                                        |

|-----------|-------------------------------------------|------------------------------------------------|-------------------------------------------------------|

| V′        | Vertical Blanking (long integration time) | (Reg0x09 – (Reg0x03)/S)) * (A + Q) + (Q - 2*P) | 25,868 pixel clocks<br>= 51,736 master<br>= 1.91ms    |

| F'        | Total Frame Time (long integration time)  | (Reg0x09) * (A + Q)                            | 449,956 pixel clocks<br>= 899,912 master<br>= 33.33ms |

## **Output Data Format (Serial Mode)**

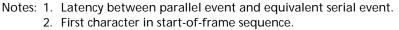

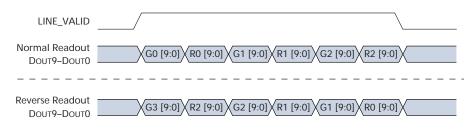

The MT9V012 image data is read out in a progressive scan. In serial mode, valid image data is surrounded by horizontal blanking and vertical blanking, as shown in Figure 7 on page 10. However, unlike default mode, serial mode provides pixel data and timing strobes combined into a single serial bit stream. Electrically, this bit stream uses LVDS on the DOUTP and DOUTN output signals.

In serial mode, each pixel is encoded as a 12-bit value by adding a start bit and a stop bit. The sensor CLKIN input runs at the serial bit-rate and is used within the sensor to clock a data serializer circuit; it is divided within the sensor so that most of the circuitry runs at the same rate as in default mode. In serial mode, the pixel rate is fixed at one-half the input frequency; therefore, CLKIN runs at  $6 \times 27$  MHz = 162 MHz.

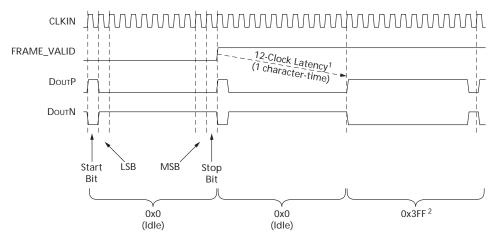

#### **Output Data Timing (Serial Mode)**

The default frame timing in serial mode is identical to the frame timing in default mode. A special three-character "start-of-frame" sequence—0x3FF, 0x0, and 0x3FF—is transmitted to indicate the assertion of FRAME\_VALID. Pixel data, LINE\_VALID, and FRAME\_VALID can be reconstructed externally by detecting the start-of-frame sequence, and using a state machine and counters to identify the active regions of the frame.

Figure 10 on page 13 shows the beginning of a start-of-frame sequence. It shows the latency introduced in the parallel-to-serial conversion, and the way in which start and stop bits are used to frame 10-bit pixel data. Figure 11 on page 14 shows the serial data stream at the start of a line. In this figure, each 12-bit serial character is represented by its 10-bit payload. In both figures, the LINE\_VALID and FRAME\_VALID signals are shown for reference only; these signals are not available in serial mode.

The most effective method for detecting the start-of-frame sequence is to look for a continuous sequence of idle (0x0) characters before looking for the 0x3FF, 0x0, 0x3FF sequence. The start-of-frame sequence indicates the start of a frame without ambiguity, as it can never occur as part of a pixel data stream.

In addition, correct operation in serial mode requires that various register settings are left at their default values. For example, Reg0x0A and Reg0x20[15:14].

The sensor timing in serial mode is calculated in exactly the same way as for default mode. See "Output Data Timing (Default Mode)" on page 11.

#### Figure 10: Start of Frame: Serial Mode

#### MT9V012 - 1/6-Inch VGA CMOS Digital Image Sensor Output Data Format (Serial Mode)

## Figure 11: Start of Line: Serial Mode

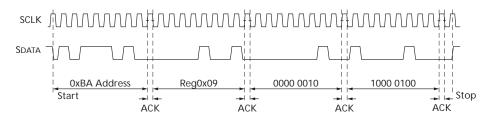

# **Two-Wire Serial Interface**

|                | The two-wire serial register interface enables read/write access to control and status registers within the MT9V012.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | The interface protocol uses a master/slave model in which a master controls one or more slave devices. The sensor acts as a slave device. The master generates a clock (SCLK) that is an input to the sensor and used to synchronize transfers. Data is transferred between the master and the slave on a bidirectional signal (SDATA). The SDATA signal is pulled up to VDD off-chip by a $1.5$ K $\Omega$ resistor. Either the slave or master device can drive the SDATA line LOW—the interface protocol determines which device is allowed to drive the SDATA line at any given time.                                                                               |

| Protocol       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | The two-wire serial interface defines several different transmission codes, as follows:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | a start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                | the slave device 8-bit address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | <ul> <li>a(an) (no) acknowledge bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | • an 8-bit message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                | a stop bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Sequence       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | A typical read or write sequence begins by the master sending a start bit. After the start bit, the master sends the 8-bit slave-device address. The last bit of the address determines if the request will be a read or a write, where a "0" indicates a write and a "1" indicates a read. The slave device acknowledges receipt of the address by sending an acknowledge bit back to the master.                                                                                                                                                                                                                                                                      |

|                | If the request was a write, the master then transfers the 8-bit register address to which a write should take place. The slave sends an acknowledge bit to indicate that the register address has been received. The master then transfers the data, 8 bits at a time, with the slave sending an acknowledge bit after each 8 bits. The MT9V012 uses 16-bit data for its internal registers, thus requiring two 8-bit transfers to write to one register. After 16 bits are transferred, the register address is automatically incremented, so that the next 16 bits are written to the next register address. The master stops writing by sending a start or stop bit. |

|                | A typical read sequence is executed as follows. The master sends the write mode slave<br>address and 8-bit register address, just as in the write request. The master then sends a<br>start bit and the read mode slave address, and clocks out the register data, 8 bits at a<br>time. The master sends an acknowledge bit after each 8-bit transfer. The register address<br>is auto-incremented after every 16 bits is transferred. The data transfer is stopped when<br>the master sends a no-acknowledge bit.                                                                                                                                                      |

| Bus Idle State |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | The bus is idle when both the data and clock lines are HIGH. Control of the bus is initi-<br>ated with a start bit, and the bus is released with a stop bit. Only the master can generate<br>the start and stop bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Start Bit      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | The start bit is defined as a HIGH-to-LOW data line transition while the clock line is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Stop Bit       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                | The stop bit is defined as a LOW-to-HIGH data line transition while the clock line is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Slave Address     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | The 8-bit address of a two-wire serial interface device consists of 7 bits of address and 1 bit of direction. A "0" in the LSB of the address indicates write mode, and a "1" indicates read mode. The default slave addresses used by the MT9V012 are 0xBA (write address) and 0xBB (read address). Reg0x0D[10] can be used to select the alternate slave addresses 0x90 (write address) and 0x91 (read address).                 |

|                   | Writes to Reg0x0D[10] are inhibited when STANDBY is asserted (all other writes proceed normally). This allows two sensors to co-exist as slaves on this interface, but they must be addressed independently. Enable this capability as follows:                                                                                                                                                                                    |

|                   | • After RESET# is negated, both sensors will use the default slave address. Reads or writes on the serial register interface to the default slave address will be decoded by both sensors simultaneously.                                                                                                                                                                                                                          |

|                   | • After reset, assert STANDBY to one sensor and negate STANDBY to the other sensor.<br>Perform a write to Reg0x0D with bit 10 set. The sensor with STANDBY asserted will<br>ignore the write to bit 10 and will continue to decode at the default slave address. The<br>sensor with STANDBY negated will have its Reg0x0D[10] set and will respond to the<br>alternate slave address for all subsequent READ and WRITE operations. |

| Data Bit Transfer |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | One data bit is transferred during each clock pulse. The serial interface clock pulse is provided by the master. The data must be stable during the high period of the two-wire serial interface clock—it can only change when the serial clock is LOW. Data is transferred 8 bits at a time, followed by an acknowledge bit.                                                                                                      |

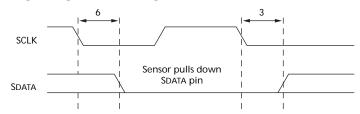

| Acknowledge Bit   |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | The master generates the acknowledge clock pulse. The transmitter (which is the master when writing, or the slave when reading) releases the data line, and the receiver indicates an acknowledge bit by driving the data line LOW during the acknowledge clock pulse.                                                                                                                                                             |

| No-Acknowledge B  | lit                                                                                                                                                                                                                                                                                                                                                                                                                                |

| -                 | The no-acknowledge bit is generated when the data line is not driven LOW by the receiver during the acknowledge clock pulse. A no-acknowledge bit is used to terminate a read sequence.                                                                                                                                                                                                                                            |

| Page Register     |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | The MT9V012 two-wire serial interface and its associated protocols support an address space of 256 16-bit locations. This address space can be extended by a 3-bit page prefix, and controlled through accesses to Reg0xF0.                                                                                                                                                                                                        |

|                   | The paging mechanism is intended to allow access to other sets of registers when the sensor is embedded as part of a more complex integrated sub-system (for example, in an SOC). All of the registers within the MT9V012 are accessible on page 0 (the default page).                                                                                                                                                             |

# **Two-Wire Serial Interface Sample Write and Read Sequences**

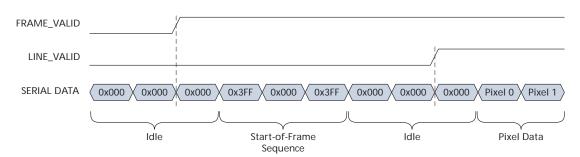

#### **16-Bit Write Sequence**

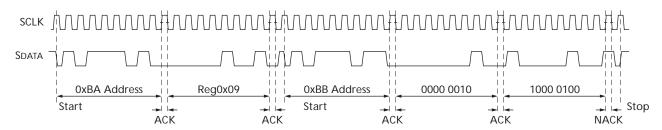

A typical write sequence for writing 16 bits to a register is shown in Figure 12. A start bit given by the master starts the sequence, followed by the write address. The image sensor then sends an acknowledge bit and expects the register address to come first, followed by the 16-bit data. After each 8-bit transfer, the image sensor sends an acknowledge bit. All 16 bits must be written before the register is updated. After 16 bits are transferred, the register address is automatically incremented so that the next 16 bits are written to the next register. The master stops writing by sending a start or stop bit.

## Figure 12: Timing Diagram Showing a Write to Reg0x09, Value 0x0284

#### **16-Bit Read Sequence**

A typical read sequence is shown in Figure 13. First the master writes the register address, as in a write sequence. Then a start bit and the read address specify that a read is about to happen from the register. The master clocks out the register data 8 bits at a time. The master sends an acknowledge bit after each 8-bit transfer. The register address should be incremented after every 16 bits is transferred. The data transfer is stopped when the master sends a no-acknowledge bit.

## Figure 13: Timing Diagram Showing a Read from Reg0x09; Returned Value 0x0284

#### 8-Bit Write Sequence

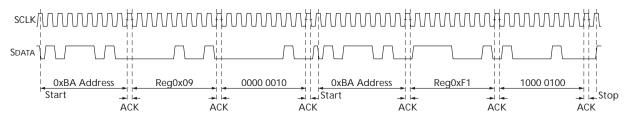

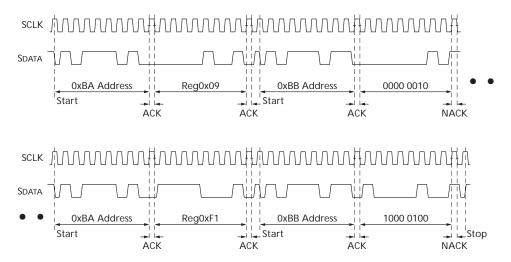

To be able to write one byte at a time to the register, a special register address is added. The 8-bit write is done by writing the upper 8 bits to the desired register, then writing the lower 8 bits to the special register address (Reg0xF1). The register is not updated until all 16 bits have been written. It is not possible to update just half of a register. Figure 14 shows a typical sequence for 8-bit writes. The second byte is written to the special register (Reg0xF1).

#### Figure 14: Timing Diagram Showing a Write to Reg0x09, Value 0x0284

#### 8-Bit Read Sequence

To read one byte at a time, the same special register address is used for the lower byte. The upper 8 bits are read from the desired register. By following this with a read from the special register (Reg0xF1), the lower 8 bits are accessed (Figure 15). The master sets the no-acknowledge bits.

#### Figure 15: Timing Diagram Showing a Read from Reg0x09; Returned Value 0x0284

# Registers

The MT9V012 provides a register address space of 256 locations.

#### **Register Map**

Table 5 shows the locations used within the address space. Locations that are not shown in the table are reserved for future use; they should not be read from or written to. The effect of reading from or writing to "Reserved" registers is UNDEFINED and may include the possibility of causing permanent electrical damage to the sensor.

## Table 5: Register List and Default Value

| Register Number<br>(Hex) | Description           | Data Format (Binary)      | Default Value<br>(Hex) |  |

|--------------------------|-----------------------|---------------------------|------------------------|--|

| 0x00                     | Chip Version          | 0001 0010 0010 0010 (LSB) | 0x1222                 |  |

| 0x01                     | Row Start             | 0000 000d dddd dddd       | 0x000E                 |  |

| 0x02                     | Column Start          | 0000 00dd dddd dddd       | 0x0026                 |  |

| 0x03                     | Row Width             | 0000 000d dddd dddd       | 0x01E0                 |  |

| 0x04                     | Column Width          | 0000 00dd dddd dddd       | 0x0280                 |  |

| 0x05                     | Horizontal Blanking B | 00dd dddd dddd dddd       | 0x00F4                 |  |

| 0x06                     | Vertical Blanking B   | 0ddd dddd dddd            | 0x001D                 |  |

| 0x07                     | Horizontal Blanking A | 00dd dddd dddd dddd       | 0x0234                 |  |

| 0x08                     | Vertical Blanking A   | 0ddd dddd dddd            | 0x010D                 |  |

| 0x09                     | Shutter Width         | dddd dddd dddd            | 0x01FD                 |  |

| 0x0A                     | Row Speed             | ddd0 000d dddd 0ddd       | 0x0011                 |  |

| 0x0B                     | Extra Delay           | 00dd dddd dddd dddd       | 0x0000                 |  |

| 0x0C                     | Shutter Delay         | 00dd dddd dddd dddd       | 0x0000                 |  |

| 0x0D                     | Reset                 | d000 0ddd dddd dd0d       | 0x0008                 |  |

| 0x20                     | Read Mode B           | dd00 00dd dddd dddd       | 0x0400                 |  |

| 0x21                     | Read Mode A           | 0000 0000 0000 dd00       | 0x040C                 |  |

| 0x22                     | Dark Col/Rows         | 0000 00dd dddd dddd       | 0x012B                 |  |

| 0x23                     | Flash                 | 00dd dddd dddd dddd       | 0x0608                 |  |

| 0x24                     | Extra Reset           | 0d00 0000 0000 0000       | 0x4000                 |  |

| 0x2B                     | Green1 Gain           | 0000 dddd dddd dddd       | 0x0020                 |  |

| 0x2C                     | Blue Gain             | 0000 dddd dddd dddd       | 0x0040                 |  |

| 0x2D                     | Red Gain              | 0000 dddd dddd dddd       | 0x0020                 |  |

| 0x2E                     | Green2 Gain           | 0000 dddd dddd dddd       | 0x0020                 |  |

| 0x2F                     | Global Gain           | 0000 dddd dddd dddd       | 0x0020                 |  |

| 0x30                     | Row Noise             | dddd dddd dddd            | 0x042A                 |  |

| 0x31                     | Reserved              |                           | 0x1C00                 |  |

| 0x32                     | Reserved              | _                         | 0x002A                 |  |

| 0x33                     | Reserved              | _                         | 0x0341                 |  |

| 0x34                     | Reserved              |                           | 0xC009                 |  |

| 0x35                     | Reserved              | _                         | 0x2022                 |  |

| 0x36                     | Reserved              | _                         | 0xF0F0                 |  |

| 0x37                     | Reserved              | —                         | 0x0000                 |  |

| 0x3B                     | Reserved              | _                         | 0x0021                 |  |

| 0x3C                     | Reserved              | _                         | 0x1A20                 |  |

| 0x3D                     | Reserved              | _                         | 0x201E                 |  |

| 0x3E                     | Reserved              | _                         | 0x2020                 |  |

## Table 5: Register List and Default Value (continued)

| Register Number<br>(Hex) | Description      | Data Format (Binary) | Default Value<br>(Hex) |

|--------------------------|------------------|----------------------|------------------------|

| 0x3F                     | Reserved         | _                    | 0x1020                 |

| 0x40                     | Reserved         | _                    | 0x2000                 |

| 0x41                     | Reserved         |                      | 0x00D7                 |

| 0x42                     | Reserved         | _                    | 0x0777                 |

| 0x58                     | Reserved         |                      | 0x0000                 |

| 0x59                     | Black Rows       | 0000 0000 dddd dddd  | 0x000C                 |

| 0x5A                     | Reserved         |                      | 0xE00A                 |

| 0x5B                     | Dark G1 Average  | 0000 0000 0??? ????  |                        |

| 0x5C                     | Dark B Average   | 0000 0000 0??? ????  |                        |

| 0x5D                     | Dark R Average   | 0000 0000 0??? ????  |                        |

| 0x5E                     | Dark G2 Average  | 0000 0000 0??? ????  |                        |

| 0x5F                     | Calib Threshold  | 0ddd dddd 0ddd dddd  | 0x231D                 |

| 0x60                     | Calib Control    | d000 000d dddd dddd  | 0x0080                 |

| 0x61                     | Calib Green1     | 0000 000d dddd dddd  | 0x0000                 |

| 0x62                     | Calib Blue       | 0000 000d dddd dddd  | 0x0000                 |

| 0x63                     | Calib Red        | 0000 000d dddd dddd  | 0x0000                 |

| 0x64                     | Calib Green2     | 0000 000d dddd dddd  | 0x0000                 |

| 0x65                     | Reserved         |                      | 0x0000                 |

| 0x70                     | Reserved         |                      | 0x7B0A                 |

| 0x71                     | Reserved         | _                    | 0x7B0A                 |

| 0x72                     | Reserved         |                      | 0x190E                 |

| 0x73                     | Reserved         | _                    | 0x750F                 |

| 0x74                     | Reserved         |                      | 0x5732                 |

| 0x75                     | Reserved         |                      | 0x5634                 |

| 0x76                     | Reserved         |                      | 0x7335                 |

| 0x77                     | Reserved         |                      | 0x3012                 |

| 0x78                     | Reserved         |                      | 0x3012                 |

| 0x79                     | Reserved         |                      | 0x7506                 |

| 0x7A                     | Reserved         |                      | 0x770A                 |

| 0x7B                     | Reserved         | _                    | 0x7809                 |

| 0x7C                     | Reserved         |                      | 0x7D06                 |

| 0x7D                     | Reserved         | _                    | 0x3110                 |

| 0x7E                     | Reserved         | _                    | 0x007E                 |

| 0x7F                     | Reserved         |                      | 0x7C01                 |

| 0x80                     | Reserved         | _                    | 0x5904                 |

| 0x81                     | Reserved         | _                    | 0x5904                 |

| 0x82                     | Reserved         | _                    | 0x570A                 |

| 0x83                     | Reserved         | _                    | 0x2D0B                 |

| 0x84                     | Reserved         | _                    | 0x580B                 |

| 0x85                     | Reserved         | _                    | 0x480E                 |

| 0x86                     | Reserved         |                      | 0x5B02                 |

| 0x87                     | Reserved         |                      | 0x005C                 |

| 0xC8                     | Context Control  | 0000 0000 d000 dddd  | 0x000B                 |

| 0xF0                     | Page Map         | 0000 0000 0000 0ddd  | 0x0000                 |

| OxF1                     | Bytewise Address | 0000 0000 0000 0000  | 0x0000                 |

| Table 5: | Register | List and Default Valu | e (continued) |

|----------|----------|-----------------------|---------------|

|----------|----------|-----------------------|---------------|

| Register Number<br>(Hex) | Description  | Data Format (Binary) | Default Value<br>(Hex) |

|--------------------------|--------------|----------------------|------------------------|

| 0xF5                     | Reserved     | —                    | 0x03FF                 |

| 0xF6                     | Reserved     | —                    | 0x01FF                 |

| 0xF7                     | Reserved     |                      | 0x0000                 |

| 0xF8                     | Reserved     | —                    | 0x0000                 |

| 0xF9                     | Reserved     | —                    | 0x0000                 |

| 0xFA                     | Reserved     |                      | 0x0000                 |

| 0xFB                     | Reserved     | —                    | 0x0000                 |

| 0xFC                     | Reserved     | —                    | 0x0000                 |

| 0xFD                     | Reserved     | —                    | 0x0000                 |

| OxFF                     | Chip Version | 0001 0010 0010 0010  | 0x1222                 |

Note: 1 = always 1

0 = always 0

d = programmable

? = read-only

## **Register Description**

Table 6 provides a detailed description of the registers. Bit fields that are not identified in the table are read-only "0."

#### **Double-Buffered Registers**

|            | Some sensor settings cannot be changed during frame readout. For example, changing Reg0x03 (row width) partway through frame readout would result in inconsistent LINE_VALID behavior. To avoid this, the MT9V012 double buffers many registers by implementing a "pending" and a "live" version. Reads and writes access the pending register. The live register controls the sensor operation.                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | The values in the pending registers are transferred to the live registers at a fixed point in the frame timing, called "frame start." Frame start is defined as the point at which the first dark row is read out. By default, this occurs 6 row times before FRAME_VALID goes HIGH. Reg0x22 enables the dark rows to be shown in the image, but this has no effect on the position of frame start.                             |

|            | In Table 6, the "Sync'd" column shows which registers or register fields are double-buff-<br>ered in this way.                                                                                                                                                                                                                                                                                                                  |

|            | Reg0x0D[15] can be used to inhibit transfers from the pending to the live registers. This control bit should be used when the user wants to make many register changes and have them all take effect simultaneously.                                                                                                                                                                                                            |

| Bad Frames |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | A bad frame is a frame where all rows do not have the same integration time, or where offsets to the pixel values have changed during the frame.                                                                                                                                                                                                                                                                                |

|            | Many changes to the sensor register settings can cause a bad frame. For example, when Reg0x03 (row width) is changed, the new register value does not affect sensor behavior until the next frame start. However, the frame that would be read out at that frame start will have been integrated using the old row width, so reading it out using the new row width would result in a frame with an incorrect integration time. |

|            | By default, most bad frames are masked: LINE_VALID and FRAME_VALID are inhibited for these frames so that the vertical blanking time between frames is extended by the frame time.                                                                                                                                                                                                                                              |

|            |                                                                                                                                                                                                                                                                                                                                                                                                                                 |

In Table 6, the "Bad Frame" column shows where changing a register or register field will cause a bad frame. The following notation is used:

- N—No. Changing the register value will not produce a bad frame.

- Y—Yes. Changing the register value might produce a bad frame.

- YM—Yes; but the bad frame will be masked out unless the "show bad frames" feature (Reg0x0D[8])is enabled.

#### **Changes to Integration Time**

If the integration time (Reg0x09) is changed while FRAME\_VALID is asserted for frame N, the first frame output using the new integration time is frame (N + 2). The sequence is as follows:

- 1. During frame *N*, the new integration time is held in the Reg0x09 pending register.

- 2. At the start of frame (N + 1), the new integration time is transferred to the Reg0x09 live register. Integration for each row of frame (N + 1) has been completed using the old integration time.

- 3. The earliest time that a row can start integrating using the new integration time is immediately after that row has been read for frame (N + 1). The actual time that rows start integrating using the new integration time is dependent upon the new value of the integration time.

- 4. When frame (N + 1) is read out, it will have been integrated using the new integration time.

If the integration time is changed (Reg0x09 written) on successive frames, each value written will be applied for a single frame; the latency between writing a value and it affecting the frame readout remains at two frames.

#### **Changes to Gain Settings**

Usually, when the gain settings (Reg0x2B, Reg0x2C, Reg0x2D, Reg0x2E, and Reg0x2F) are changed, the gain is updated on the next frame start. When the integration time and the gain are changed at the same time, the gain update is held off by one frame so that the first frame output with the new integration time also has the new gain applied.

## Table 6: Register Description

| Bit     |                          | Bit Description                                                                                                                                                                                                                                                                | Default<br>(hex) | Sync'd<br>toFrame<br>Start | Bad<br>Frame |

|---------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------|--------------|

| 0x00/0  | xFF (0/255) Chip         | Version                                                                                                                                                                                                                                                                        |                  |                            |              |

| 15:0    | Chip Version             | Chip version. Read-only.                                                                                                                                                                                                                                                       | 1222             | N                          | Ν            |

| 0x01 (* | 1) Row Start             |                                                                                                                                                                                                                                                                                |                  |                            |              |

| 8:0     | Row Start                | The first row to be read out (not counting any dark rows that may be read). To move the image window, set this register to the starting "Y" value. Setting a value less than eight is not recommended, as the dark rows should be read using Reg0x22.                          | 12               | Y                          | ΥM           |

| 0x02 (2 | 2) Column Start          |                                                                                                                                                                                                                                                                                |                  |                            |              |

| 9:0     | Column Start             | The first column to be read out (not counting dark columns<br>that may be read). To move the image window, set this<br>register to the starting "X" value. Setting a value below<br>Reg0x18 is not recommended, as readout of dark columns<br>should be controlled by Reg0x22. | 26               | Y                          | ΥM           |

| 0x03 (3 | 3) Row Width             |                                                                                                                                                                                                                                                                                |                  |                            |              |

| 8:0     | Row Width                | Number of rows in the image to be read out (not counting<br>any dark rows or border rows that may be read). The<br>minimum supported value is 2.                                                                                                                               | 1E0              | Y                          | ΥM           |

| •       | 4) Column Width          |                                                                                                                                                                                                                                                                                |                  |                            |              |

| 9:0     | Column Width             | Number of columns in the image to be read out (not counting any dark columns or border columns that may be read). The minimum supported value is 9.                                                                                                                            | 280              | Y                          | ΥM           |

| 0x05 (! | 5) Horizontal Bla        | nking B                                                                                                                                                                                                                                                                        |                  |                            |              |

| 10:0    | Horizontal<br>Blanking B | Number of blank columns in a row when context B is<br>selected (Reg0xC8[0] = 1). The extra columns are added at<br>the beginning of a row. See "Minimum Horizontal<br>Blanking" on page 35.                                                                                    | F4               | Y                          | ΥM           |

| 0x06 (  | 6) Vertical Blanki       | ng B                                                                                                                                                                                                                                                                           |                  |                            |              |

| 14:0    | Vertical<br>Blanking B   | Number of blank rows in a frame when context B is selected (Reg0xC8[1] = 1). The minimum supported value is (6 + Reg0x22[2:0]). The actual vertical blanking time can be controlled by the shutter width (Reg0x9). See "Output Data Timing (Default Mode)" on page 11.         | 1D               | Y                          | N            |

| 0x07 (7 | 7) Horizontal Bla        | nking A                                                                                                                                                                                                                                                                        |                  |                            |              |

| 10:0    | Horizontal<br>Blanking A | Number of blank columns in a row when context A is<br>selected (Reg0xC8[0] = 0). The extra columns are added at<br>the beginning of a row. See "Minimum Horizontal<br>Blanking" on page 35.                                                                                    | 234              | Y                          | ΥM           |

| 0x08 (8 | 8) Vertical Blanki       | ng A                                                                                                                                                                                                                                                                           |                  |                            |              |

| 14:0    | Vertical<br>Blanking A   | Number of blank rows in a frame when context A is chosen (Reg0xC8[1] = 1). The minimum supported value is (6 + Reg0x22[2:0]). The actual vertical blanking time can be controlled by the shutter width (Reg0x9). See "Output Data Timing (Default Mode)" on page 11.           | 10D              | Y                          | Ν            |

| 0x09 (9 | 9) Shutter Width         |                                                                                                                                                                                                                                                                                |                  |                            |              |

| 15:0    | Shutter Width            | Integration time in number of rows. The integration time is also influenced by the shutter delay (Reg0x0C) and the overhead time.                                                                                                                                              | 1FD              | Y                          | N            |

|         |                          |                                                                                                                                                                                                                                                                                |                  |                            | -            |