## **VBSD1-SIP Series Dc-Dc Converter**

Rev. 11-2005

## **Description**

Designed to convert fixed voltages into an isolated voltage, the VBSD1-SIP series is well suited for providing board-mount local supplies in a wide range of applications, including mixed analog/digital circuits, test & measurement equip., process/machine controls, datacom/telecom fields, etc...

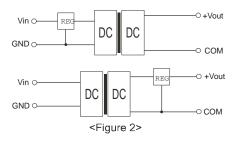

The semi-regulated output can be followed by 3-terminal regulators to provide output protection, in addition to output regulation.

## **Features**

- ·Isolated 1 W output

- •Temperature range: -40°C~+85°C available in -55°C~+125°C

- ·Unregulated

- ·High efficiency to 80%

- ·Single voltage output

- Small footprint

- ·SIP package style

- Industry standard pinout

- -UL94-V0 package

- ·No heatsink required

- -1K Vdc isolation

- ·Power density 0.85 W/cm<sup>3</sup>

- ·No external component required

- ·Low cost

| Model               | Input   | Voltage         | Output  | Output ( | Current |            | Package |

|---------------------|---------|-----------------|---------|----------|---------|------------|---------|

| Number              | Nominal | Range           | Voltage | Max.     | Min.    | Efficiency | Style   |

| VBSD1-S3.3-S3.3-SIP | 3.3 Vdc | 3.00~3.60 Vdc   | 3.3 Vdc | 300 mA   | 30 mA   | 72%        | SIP     |

| VBSD1-S3.3-S5-SIP   | 3.3 Vdc | 3.00~3.60 Vdc   | 5 Vdc   | 200 mA   | 20 mA   | 73%        | SIP     |

| VBSD1-S5-S3.3-SIP   | 5 Vdc   | 4.5~5.5 Vdc     | 3.3 Vdc | 300 mA   | 30 mA   | 72%        | SIP     |

| VBSD1-S5-S5-SIP     | 5 Vdc   | 4.5~5.5 Vdc     | 5 Vdc   | 200 mA   | 20 mA   | 78%        | SIP     |

| VBSD1-S5-S9-SIP     | 5 Vdc   | 4.5~5.5 Vdc     | 9 Vdc   | 111 mA   | 12 mA   | 79%        | SIP     |

| VBSD1-S5-S12-SIP    | 5 Vdc   | 4.5~5.5 Vdc     | 12 Vdc  | 83 mA    | 9 mA    | 80%        | SIP     |

| VBSD1-S5-S15-SIP    | 5 Vdc   | 4.5~5.5 Vdc     | 15 Vdc  | 67 mA    | 7 mA    | 78%        | SIP     |

| VBSD1-S5-S24-SIP    | 5 Vdc   | 4.5~5.5 Vdc     | 24 Vdc  | 42 mA    | 5 mA    | 78%        | SIP     |

| VBSD1-S12-S3.3-SIP  | 12 Vdc  | 10.8~13.2 Vdc   | 3.3 Vdc | 300 mA   | 30 mA   | 73%        | SIP     |

| VBSD1-S12-S5-SIP    | 12 Vdc  | 10.8~13.2 Vdc   | 5 Vdc   | 200 mA   | 20 mA   | 78%        | SIP     |

| VBSD1-S12-S9-SIP    | 12 Vdc  | 10.8~13.2 Vdc   | 9 Vdc   | 111 mA   | 12 mA   | 80%        | SIP     |

| VBSD1-S12-S12-SIP   | 12 Vdc  | 10.8~13.2 Vdc   | 12 Vdc  | 83 mA    | 9 mA    | 81%        | SIP     |

| VBSD1-S12-S15-SIP   | 12 Vdc  | 10.8~13.2 Vdc   | 15 Vdc  | 67 mA    | 7 mA    | 79%        | SIP     |

| VBSD1-S12-S24-SIP   | 12 Vdc  | 10.8~13.2 Vdc   | 24 Vdc  | 42 mA    | 5 mA    | 79%        | SIP     |

| VBSD1-S15-S3.3-SIP  | 15 Vdc  | 14.25~15.75 Vdc | 3.3 Vdc | 300 mA   | 30mA    | 73%        | SIP     |

| VBSD1-S15-S5-SIP    | 15 Vdc  | 14.25~15.75 Vdc | 5 Vdc   | 200 mA   | 20 mA   | 74%        | SIP     |

| VBSD1-S15-S9-SIP    | 15 Vdc  | 14.25~15.75 Vdc | 9 Vdc   | 111 mA   | 12 mA   | 75%        | SIP     |

| VBSD1-S15-S12-SIP   | 15 Vdc  | 14.25~15.75 Vdc | 12 Vdc  | 83 mA    | 9 mA    | 79%        | SIP     |

| VBSD1-S15-S15-SIP   | 15 Vdc  | 14.25~15.75 Vdc | 15 Vdc  | 67 mA    | 7 mA    | 79%        | SIP     |

| VBSD1-S15-S24-SIP   | 15 Vdc  | 14.25~15.75 Vdc | 24 Vdc  | 42 mA    | 5 mA    | 79%        | SIP     |

| VBSD1-S24-S3.3-SIP  | 24 Vdc  | 21.6~26.4 Vdc   | 3.3 Vdc | 300 mA   | 30 mA   | 73%        | SIP     |

| VBSD1-S24-S5-SIP    | 24 Vdc  | 21.6~26.4 Vdc   | 5 Vdc   | 200 mA   | 20 mA   | 79%        | SIP     |

| VBSD1-S24-S9-SIP    | 24 Vdc  | 21.6~26.4 Vdc   | 9 Vdc   | 111 mA   | 12 mA   | 80%        | SIP     |

| VBSD1-S24-S12-SIP   | 24 Vdc  | 21.6~26.4 Vdc   | 12 Vdc  | 83 mA    | 9 mA    | 81%        | SIP     |

| VBSD1-S24-S15-SIP   | 24 Vdc  | 21.6~26.4 Vdc   | 15 Vdc  | 67 mA    | 7 mA    | 79%        | SIP     |

| VBSD1-S24-S24-SIP   | 24Vdc   | 21.6~26.4 Vdc   | 24 Vdc  | 42 mA    | 5 mA    | 80%        | SIP     |

**Output Specifications**

| Item                    | Test conditions          | Min.  | Тур. | Max. | Units |

|-------------------------|--------------------------|-------|------|------|-------|

| Output power            |                          | 0.1   |      | 1    | W     |

| Line Regulation         | For Vin change of 1%     |       |      | 1.2% |       |

| Load Regulation         | 10% to 100% full load    |       | 10%  | 15%  |       |

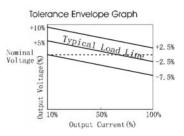

| Output voltage accuracy | See tolerance envelope   | graph |      |      |       |

| Temperature drift       | @ 100% load              |       |      | 0.03 | %/°C  |

| Output ripple           | 20 MHz Bandwidth         |       | 50   | 75   | mVp-p |

| Switching frequency     | Full load, nominal input | 100K  | 150K | 200K | Hz    |

# **VBSD1-SIP Series Dc-Dc Converter**

Rev. 11-2005

# **General Specifications**

| Short circuit protection      |                                                                      | <1 second                           |  |

|-------------------------------|----------------------------------------------------------------------|-------------------------------------|--|

| Temperature rise at full load |                                                                      | 25°C Max, 15°C Typ.                 |  |

| Cooling                       |                                                                      | Free air convection                 |  |

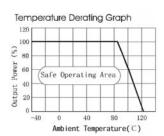

| Operating temperature range   | for regular version                                                  | -40°C to +85°C                      |  |

|                               | for extended temp. version                                           | -55°C to +125°C                     |  |

| Storage temperature range     |                                                                      | -55°C to +125°C                     |  |

| Soldering temperature         |                                                                      | 300°C (1.5mm from case for 10 sec.) |  |

| Storage humidity range        |                                                                      | <95%                                |  |

| Case material                 |                                                                      | Plastic (UL94-V0)                   |  |

| MTBF                          |                                                                      | >1,000,000 hrs.                     |  |

| Burn-in Full load at          | Full load at +85°C, for 4 hours at no-load and 4 hours at full load. |                                     |  |

# **Isolation Specifications**

| Item                  | Test Conditions   | Min. | Тур. | Max. | Units |

|-----------------------|-------------------|------|------|------|-------|

| Isolation Voltage     | Tested for 1 min. | 1000 |      |      | Vdc   |

| Insulation Resistance | Test at 500 Vdc   | 1000 |      |      | ΜΩ    |

### Notes:

- 1. All specifications measured at TA=25°C, humidity <75%, nominal input voltage and rated output load unless otherwise specified.

- 2. For extended temperature version, add -M to the model #, e.g. VBSD1-S5-S5-SIP-M.

# **Typical Characteristics**

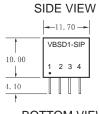

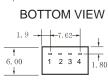

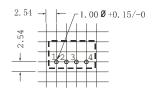

# Outline Dimensions & Recommended Layout Pattern

| Pin | Function |

|-----|----------|

| 1   | GND      |

| 2   | Vin      |

| 3   | COM      |

| 4   | +V       |

Note: All Pins on a 2.54mm pitch; All Pin diameters are 0.50 mm; all dimensions in mm.

## **VBSD1-SIP Series Dc-Dc Converter**

Rev. 11-2005

## **Application Notes:**

#### - Input filtering

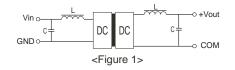

To reduce the reflected ripple current and minimize EMI, especially when the converter input is more than 2" away from the DC source, it is recommended to connect a low ESR electrolytic capacitor between Vin and Gnd. The values suggested are as shown in Table 1. If additional filtering is required, the capacitance may be increased, or expanded to an LC network as shown in Figure 1.

Table 1

| Input Voltage | External Input Capacitance |

|---------------|----------------------------|

| 3.3, 5 V      | 4.7 µF                     |

| 12 V          | 2.2 µF                     |

| 15 V          | 2.2 µF                     |

| 24 V          | 1.0 µF                     |

## - Output filtering

An output capacitor is needed to meet output ripple requirements as shown in Table 2.

Output capacitance may be increased for additional filtering, but should not exeed  $10\mu F$  or expanded to an LC network as in Figure 1.

Table 2

| Vout     | External Ouput Capacitance |  |  |

|----------|----------------------------|--|--|

| 3.3, 5 V | 4.7 µF                     |  |  |

| 9 V      | 2.2 μF                     |  |  |

| 12 V     | 1.0 μF                     |  |  |

| 15 V     | 0.47 μF                    |  |  |

| 24 V     | 0.33 μF                    |  |  |

#### Minimum loading

The converter needs a minimum of 10% loading to maintain output regulation. Operation under no-load conditions will not cause immediate damages but may reduce reliability, and cause performance not to meet specifications.

## - Regulation

With a semi-regulated design, the converter's output voltage varies with load current and will change proportionally to the input voltage. If regulated output is needed, an external regulator can be used as shown in Figure 2.

#### - Protection

The converter has minimal protection against input over-voltage or output over-load, and may be permanently damaged if exposed to these conditions. An input clamping device can be used for input voltage limiting. An input fuse or an output fuse can also be used to protect against over-loading.

## - External Regulator

An external 3-terminal regulator can be connected to the output of the converter to achieve full regulation. Make sure the converter's output voltage provides sufficient head room for the regulator. An additional benefit is that the built-in protection features in the regulator, such as OCP, OTP, etc, will protect the converter also. In a complimentory supply, a negative output regulator must be used to achieve the negative regulated output.