# 4.0 CompactFlash Memory Card Interface Description

#### 4.1 Physical Description

The host is connected to the CompactFlash Memory Card using a standard 50 pin connector consisting of two rows of 25 female contacts each on 50 mil (1.27 mm) centers.

#### 4.1.1 Pin Assignments and Pin Type

The signal/pin assignments are listed in Table 4-1. Low active signals have a "-" prefix. Pin types are Input, Output or Input/Output. Table 4-2 defines the DC characteristics for all input and output type structures.

#### 4.2 Electrical Description

The CompactFlash Memory Card Series is optimized for operation with hosts which support the PCMCIA I/O interface standard conforming to the PC Card ATA specification. However, the CompactFlash Card may also be configured to operate in systems that support only the memory interface standard. The configuration of the CompactFlash Card will be controlled using the standard PCMCIA configuration registers starting at address 200h in the Attribute Memory space of the CompactFlash Memory Card.

Table 4-2 describes the I/O signals. Signals whose source is the host are designated as inputs while signals that the CompactFlash Memory Card sources are outputs. The CompactFlash Card logic levels conform to those specified in the PCMCIA Release 2.1 specification.

Table 4-1 Pin Assignments and Pin Type

| Pin<br>Num | Signal<br>Name | Pin<br>Type | In / Out<br>Type | Pin<br>Num | Signal<br>Name | Pin<br>Type | In / Out<br>Type |

|------------|----------------|-------------|------------------|------------|----------------|-------------|------------------|

| 1          | GND            |             | Ground           | 26         | -CD1           | 0           | Ground           |

| 2          | D03            | I/O         | I-1/O-3          | 27         | D11*           | I/O         | I-1/O-3          |

| 3          | D04            | 1/0         | I-1/O-3          | 28         | D12*           | 1/0         | I-1/O-3          |

| 4          | D05            | 1/0         | I-1/O-3          | 29         | D13*           | I/O         | I-1/O-3          |

| 5          | D06            | 1/0         | I-1/O-3          | 30         | D14*           | I/O         | I-1/O-3          |

| 6          | D07            | I/O         | I-1/O-3          | 31         | D15*           | 1/0         | I-1/O-3          |

| 7          | -CE1           | 1           | 1-4              | 32         | -CE2*          | -           | I-4              |

| 8          | A10            | I           | l-1              | 33         | -VS1           | 0           | Ground           |

| 9          | -OE            | +           | 1-4              | 34         | -IORD          | 1           | I-4              |

| 10         | A09            | 1           | I-1              | 35         | -IOWR          |             | 1-4              |

| 11         | A08            | 1           | <b>I-1</b>       | 36         | -WE            | 1           | 1-4              |

| 12         | A07            | 1_          | 1-1              | 37         | RDY/BSY\IREQ   | 0           | O-2              |

| 13         | VCC            |             | Power            | 38         | VCC            |             | Power            |

| 14         | A06            | 1           | l-1              | 39         | -CSEL          | <u> </u>    | 1-2              |

| 15         | A05            | 1           | l-1              | 40         | -VS2           | 0           | Open             |

| 16         | A04            | 1           | l-1              | 41         | RESET          | l           | I-4              |

| 17         | A03            |             | l-1              | 42         | -WAIT          | 0           | O-3              |

| 18         | A02            | -           | l-1              | 43         | -INPACK        | 0           | O-2              |

| 19         | A01            | 1           | l-1              | 44         | -REG           | 1           | 1-4              |

| 20         | A00            | i i         | I-1              | 45         | BVD2           | 1/0         | O-1              |

| 21         | D00            | 1/0         | I-1/O-3          | 46         | BVD1           | 1/0         | I-3/O-1          |

| 22         | D01            | 1/0         | l-1/O-3          | 47         | D08*           | 1/0         | l-1/O-3          |

| 23         | D02            | 1/0         | l-1/O-3          | 48         | D09*           | 1/0         | I-1/O-3          |

| 24         | WP\-iOIS16     | 0           | O-3              | 49         | D10*           | 1/0         | I-1/O-3          |

| 25         | -CD2           | 0           | Ground           | 50         | GND            |             | Ground           |

Note: Signals marked with an asterisk are required only for 16 bit access, not required when installed in 8-bit systems. Signals that are defined differently in the Memory only interface and the I/O interface have the Memory only interface signal shown first, followed by a backslash (\) and then the I/O interface signal interface. The - IORD, -IOWR and -INPACK signals are not used in the memory only interface.

Table 4-2 Signal Description

| Signal Name                  | Dir. | Pin                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------------------------|------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BVD2 (Memory)<br>-SPKR (I/O) | 1/0  | 45                                                      | This output line is always driven to a high state since a battery is not required for this product and no audio is produced.                                                                                                                                                                                                                                                                                                                |

| DASP (IDE)                   |      |                                                         | In the True IDE Mode, this input / output is the Disk Active / Slave Present signal in the Master / Slave handshake protocol.                                                                                                                                                                                                                                                                                                               |

| -CD1, -CD2                   | 0    | 25,26                                                   | These Card Detect pins are connected to ground on the CompactFlash Memory Card. They are used by the host to determine that the CompactFlash Card is fully inserted into its socket.                                                                                                                                                                                                                                                        |

| D15 - D00                    | 1/0  | 31,30,29,28,<br>27,49,48,47,<br>6,5,4,3,2,23,<br>22, 21 | These lines carry the Data, Commands and Status information between the host and the controller. D00 is the LSB of the Even Byte of the Word. D08 is the LSB of the Odd Byte of the Word.                                                                                                                                                                                                                                                   |

|                              |      | 22, 21                                                  | In True IDE Mode, all Task File operations occur in byte mode on the low order bus D00-D07 while all data transfers are 16 bit using D00-D15.                                                                                                                                                                                                                                                                                               |

| -IOWR (I/O)                  | 1    | 35                                                      | The I/O Write strobe pulse is used to clock I/O data on the Card Data bus into the CompactFlash Memory Card controller registers when the CompactFlash Card is configured to use the I/O interface.                                                                                                                                                                                                                                         |

|                              | :    |                                                         | The clocking will occur on the negative to positive edge of the signal (trailing edge).                                                                                                                                                                                                                                                                                                                                                     |

| -IORD (I/O)                  | -    | 34                                                      | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the CompactFlash Memory Card when the card is configured to use the I/O interface.                                                                                                                                                                                                                                                           |

| -WE/-PGM                     |      | 36                                                      | This is a signal driven by the host and used for strobing memory write data to the registers of the CompactFlash Memory Card when the card is configured in the memory interface mode. It is also used for writing the configuration registers in all modes.                                                                                                                                                                                |

|                              |      |                                                         | In True IDE Mode this input signal is not used.                                                                                                                                                                                                                                                                                                                                                                                             |

| -OE                          | _    | 9                                                       | This is an Output Enable strobe generated by the host interface. It is used to read data from the CompactFlash Memory Card in memory mode and to read the CIS and configuration registers in all modes.                                                                                                                                                                                                                                     |

|                              |      |                                                         | To enable True IDE Mode this input should be grounded.                                                                                                                                                                                                                                                                                                                                                                                      |

| RDY/-BSY<br>(Memory)         | 0    | 37                                                      | In memory mode this signal is set high when the CompactFlash Memory Card is ready to accept a new data transfer operation and held low when the card is busy. The Host memory card socket must provide a pull-up resistor. See section 2.3 for power-on or reset to ready timing.                                                                                                                                                           |

|                              |      |                                                         | At power up and at Reset, the RDY/-BSY signal is held low (busy) until the CompactFlash Memory Card has completed its power up or reset function. No access of any type should be made to the CompactFlash Card during this time. The RDY/-BSY signal is held high (disabled from being busy) whenever the following condition is true: The CompactFlash Memory Card has been powered up with +RESET continuously disconnected or asserted. |

| -IREQ (I/O)                  |      |                                                         | I/O Operation - After the CompactFlash Memory Card has been configured for I/O operation, this signal is used as -Interrupt Request. This line is strobed low to generate a pulse mode interrupt or held low for a level mode interrupt.                                                                                                                                                                                                    |

| INTRQ (IDE)                  |      |                                                         | In True IDE Mode signal is the active high Interrupt Request to the host.                                                                                                                                                                                                                                                                                                                                                                   |

Table 4-2 Signal Description (continued)

| Signal Name                        | Dir. | Pin                                   | Description                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------|------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A10 - A0                           |      | 8,10,11,12,14<br>15,16,17,18<br>19,20 | These address lines along with the -REG signal are used to select the following: The I/O port address registers within the CompactFlash Memory Card, the memory mapped port address registers within the CompactFlash Memory Card, a byte in the card's information structure and its configuration control and status registers.                                                               |

|                                    |      |                                       | In True IDE Mode only HA[2:0] are used to select the one of eight registers in the Task File, the remaining address lines should be grounded.                                                                                                                                                                                                                                                   |

| -CE1, -CE2<br>Card Enable          | 1    | 7,32                                  | These signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performedCE2 always accesses the odd byte of the wordCE1 accesses the even byte or the Odd byte of the word depending on A0 and -CE2. A multiplexing scheme based on A0, -CE1, -CE2 allows 8 bit hosts to access all data on D0-D7. See Tables 4-9, 4-10, 4-13 and 4-14. |

| CE1, CE2<br>(True IDE Mode)        |      |                                       | In the True IDE Mode CE1 is the chip select for the task file registers while CE2 is used to select the Alternate Status Register and the Device Control Register.                                                                                                                                                                                                                              |

| -CSEL                              | _    | 39                                    | This internally pulled up signal is used to configure this device as a Master or a Slave when configured in the True IDE Mode. When this pin is grounded, this device is configured as a Master. When the pin is open, this device is configured as a Slave.                                                                                                                                    |

| -REG<br>Attribute Memory<br>Select | I    | 44                                    | This signal is used during Memory Cycles to distinguish between Common Memory and Register (Attribute) Memory accesses. High for Common Memory, Low for Attribute Memory.                                                                                                                                                                                                                       |

|                                    |      |                                       | The signal must also be active (low) during I/O Cycles when the I/O address is on the Bus.                                                                                                                                                                                                                                                                                                      |

|                                    |      |                                       | In True IDE Mode this input signal is not used.                                                                                                                                                                                                                                                                                                                                                 |

| WP (Memory)<br>Write Protect       | 0    | 24                                    | Memory Mode - The CompactFlash Memory Card does not have a write protect switch. This signal is held low after the completion of the reset initialization sequence.                                                                                                                                                                                                                             |

| -IOIS16 (I/O)<br>IO is 16 Bits     |      |                                       | I/O Operation - When the CompactFlash Memory Card is configured for I/O Operation Pin 24 is used for the -I/O Selected is 16 Bit Port (-IOIS16) function. A Low signal indicates that a 16 bit or odd byte only operation can be performed at the addressed port.                                                                                                                               |

|                                    |      |                                       | In True IDE Mode this output signal is asserted low when this device is expecting a word data transfer cycle.                                                                                                                                                                                                                                                                                   |

| -INPACK (I/O)<br>Input Acknowledge | 0    | 43                                    | The Input Acknowledge signal is asserted by the CompactFlash Memory Card when the card is selected and responding to an I/O read cycle at the address that is on the address bus. This signal is used by the host to control the enable of any input data buffers between the CompactFlash Memory Card and the CPU.                                                                             |

|                                    |      |                                       | In True IDE Mode this output signal is not used.                                                                                                                                                                                                                                                                                                                                                |

Table 4-2 Signal Description (continued)

| Signal Name                     | Dir. | Pin      | Description                                                                                                                                                                                                                                                                          |

|---------------------------------|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BVD1 (Memory)                   | I/O  | 46       | Memory Mode - This signal is asserted high as the BVD1 signal since a battery is not used with this product.                                                                                                                                                                         |

| -STSCHG (I/O)<br>Status Changed |      |          | I/O Operation - This signal is asserted low to alert the host to changes in the RDY/-BSY and Write Protect states, while the I/O interface is configured. Its use is controlled by the Card Config and Status Register.                                                              |

| PDIAG<br>(True IDE Mode)        |      |          | In the True IDE Mode, this input / output is the Pass Diagnostic signal in the Master / Slave handshake protocol.                                                                                                                                                                    |

| -WAIT (PCMCIA)                  | 0    | 42       | The -WAIT signal is driven low by the CompactFlash Memory Card to signal the host to delay completion of a memory or I/O cycle that is in progress.                                                                                                                                  |

| IORDY (IDE)                     |      |          | In True IDE Mode this output signal may be used as IORDY.                                                                                                                                                                                                                            |

| GND                             |      | 1,50     | Ground.                                                                                                                                                                                                                                                                              |

| VCC                             |      | 13,38    | +5 V, +3.3 V power.                                                                                                                                                                                                                                                                  |

| RESET (PCMCIA)                  | 1    | 41       | When the pin is high, this signal Resets the CompactFlash Memory Card. The CompactFlash Card is Reset only at power up if this pin is left high or open from power-up. The CompactFlash Card is also Reset when the Soft Reset bit in the Card Configuration Option Register is set. |

| -RESET (IDE)                    |      |          | In the True IDE Mode this input pin is the active low hardware reset from the host.                                                                                                                                                                                                  |

| -VS1<br>-VS2                    | 0    | 33<br>40 | Voltage Sense SignalsVS1 is grounded if the CompactFlash Memory Card CIS can be read at 3.3 volts and -VS2 is reserved by PCMCIA for a secondary voltage.                                                                                                                            |

#### 4.2.1 Electrical Specification

The following table defines all D.C. Characteristics for the CompactFlash Memory Card Series.

Unless otherwise stated, conditions are:

SDCFB-XX SDCFBI-XX

$Vcc = 5V \pm 10\%$   $Vcc = 5V \pm 5\%$

$Vcc = 3.3V \pm 5\%$

Ta = 0°C to 60°C Ta = -40°C to 85°C

#### **Absolute Maximum Conditions:**

| Parameter                                          | Symbol | Conditions                    |

|----------------------------------------------------|--------|-------------------------------|

| Input Power                                        | Vcc    | -0.3V min. to 7.0V max.       |

| Voltage on any pin except Vcc with respect to GND. | V      | -0.5V min. to Vcc + 0.5V max. |

#### Input Leakage Current:

| Туре | Parameter             | Symbol | Conditions            | MIN | TYP | MAX  | Units |

|------|-----------------------|--------|-----------------------|-----|-----|------|-------|

| I-1  | Input Leakage Current | IL     | Vih = Vcc / Vil = Gnd | -1  |     | 1    | μΑ    |

| 1-2  | Pull Up Resistor      | RPU1   | Vcc = 5.0V            | 50k |     | 500k | Ohm   |

| 1-3  | Input Leakage Current | IL     | Vih = Vcc / Vil = Gnd | -1  |     | 1    | μА    |

| 1-4  | Pull Up Resistor      | RPU1   | Vcc = 5.0V            | 50k |     | 500k | Ohm   |

#### Input Characteristics:

| Type | Parameter                                | Symbol     | MIN | TYP        | MAX | MIN              | TYP        | MAX | Units |

|------|------------------------------------------|------------|-----|------------|-----|------------------|------------|-----|-------|

|      |                                          |            | VC  | CC = 3.3   | V   | VC               | C = 5.0    | V   | Units |

| I-1  | Input Voltage<br>CMOS                    | Vih<br>Vil | 2.4 |            | 0.6 | 4.0 <sup>1</sup> |            | 0.8 | Volts |

| I-2  | Input Voltage<br>CMOS                    | Vih<br>Vil | 1.5 |            | 0.6 | 2.0              |            | 0.8 | Volts |

| I-3  | Input Voltage<br>CMOS<br>Schmitt Trigger | Vth<br>Vtl |     | 1.8<br>1.0 |     |                  | 2.8<br>2.0 |     | Volts |

Note 1: Per PCMCIA Electrical Specification Signal Interface Table 4-18 note 1, the host must provide a logic output high voltage for a CMOS load of .9 x VCC. For a 5 volt product, this translates to .9 x 4.5 = 4.05 volts minimum Voh.

#### **Output Characteristics:**

| Туре | Parameter                    | Symbol | Conditions             | MIN          | TYP | MAX          | Units |

|------|------------------------------|--------|------------------------|--------------|-----|--------------|-------|

| 0-1  | Output Voltage               | Voh    | loh = -4 mA            | Vcc<br>-0.8V |     |              | Volts |

|      |                              | Vol    | iol = 4 mA             |              |     | Gnd<br>+0.4V |       |

| O-2  | Output Voltage               | Voh    | loh = -8 mA            | Vcc<br>-0.8V |     |              | Volts |

|      |                              | Vol    | lol = 8 mA             | -0.0         |     | Gnd<br>+0.4V |       |

| 0-3  | Output Voltage               | Voh    | loh = -16 mA           | Vcc<br>-0.8V |     |              | Volts |

|      |                              | Vol    | lol = 16 mA            | -0.07        |     | Gnd<br>+0.4V |       |

| O-X  | Tri-State<br>Leakage Current | loz    | Vol = Gnd<br>Voh = Vcc | -10          |     | 10           | μА    |

#### 4.2.2 Interface/Bus Timing

There are two types of bus cycles and timing sequences that occur in the PCMCIA type interface, a direct mapped I/O transfer and a memory access. The two timing sequences are explained in detail in the PCMCIA PC Card Standard Release 2.1. The CompactFlash Memory Card conforms to the timing in that reference document.

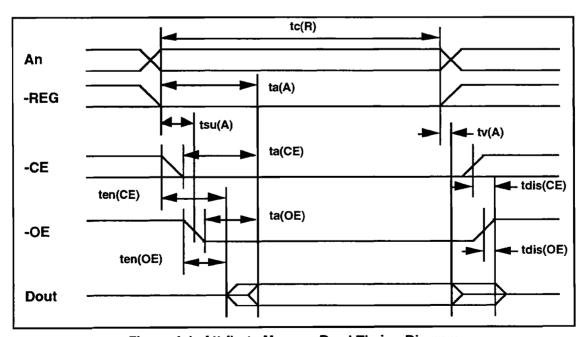

### 4.2.3 Attribute Memory Read Timing Specification

The Attribute Memory access time is defined as 300 ns. Detailed timing specifications are shown in Table 4-3.

Table 4-3 Attribute Memory Read Timing

| Speed Version                  |          |             | 300 ns      |         |  |

|--------------------------------|----------|-------------|-------------|---------|--|

| Item                           | Symbol   | IEEE Symbol | Min ns.     | Max ns. |  |

| Read Cycle Time                | tc(R)    | tAVAV       | 300         |         |  |

| Address Access Time            | ta(A)    | tAVQV       | <del></del> | 300     |  |

| Card Enable Access Time        | ta(CE)   | tELQV       |             | 300     |  |

| Output Enable Access Time      | ta(OE)   | tGLQV       |             | 150     |  |

| Output Disable Time from CE    | tdis(CE) | tEHQZ       |             | 100     |  |

| Output Disable Time from OE    | tdis(OE) | tGHQZ       |             | 100     |  |

| Address Setup Time             | tsu (A)  | tAVWL       | 30          |         |  |

| Output Enable Time from CE     | ten(CE)  | tELQNZ      | 5           |         |  |

| Output Enable Time from OE     | ten(OE)  | tGLQNZ      | 5           |         |  |

| Data Valid from Address Change | tv(A)    | tAXQX       | 0           |         |  |

Figure 4-1 Attribute Memory Read Timing Diagram

Notes: All times are in nanoseconds. Dout signifies data provided by the CompactFlash Memory Card to the system. The -CE signal or both the -OE signal and the -WE signal must be de-asserted between consecutive cycle operations.

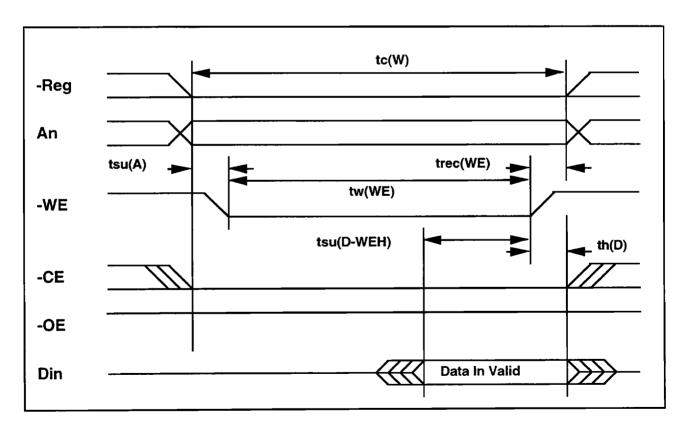

## 4.2.4 Attribute Memory Write Timing Specification

The Card Configuration write access time is Note: defined as 250 ns. Detailed timing specifications are shown in Table 4-4.

SanDisk does not allow writing from the Host to CIS Memory. Only writes to the Configuration register are allowed.

**Table 4-4 Attribute Memory Write Timing**

| Speed Version          |            |             | 250 ns |        |

|------------------------|------------|-------------|--------|--------|

| Item                   | Symbol     | IEEE Symbol | Min ns | Max ns |

| Write Cycle Time       | tc(W)      | tAVAV       | 250    |        |

| Write Pulse Width      | tw(WE)     | tWLWH       | 150    |        |

| Address Setup Time     | tsu(A)     | tAVWL       | 30     |        |

| Write Recovery Time    | trec(WE)   | tWMAX       | 30     |        |

| Data Setup Time for WE | tsu(D-WEH) | tDVWH       | 80     |        |

| Data Hold Time         | th(D)      | tWMDX       | 30     |        |

Figure 4-2 Attribute Memory Write Timing Diagram

Notes: All times are in nanoseconds.

Din signifies data provided by the system to the CompactFlash Memory Card.

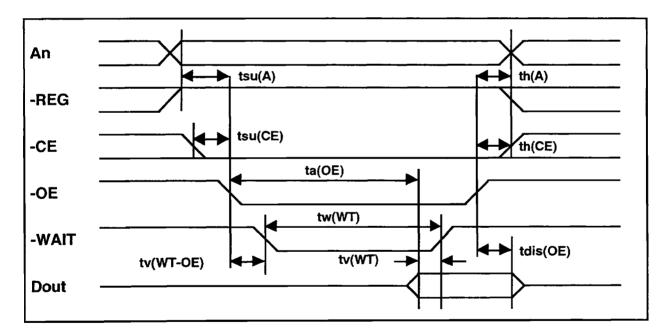

# 4.2.5 Common Memory Read Timing Specification

**Table 4-5 Common Memory Read Timing**

| Item                            | Symbol    | IEEE Symbol | Min ns. | Max ns. |

|---------------------------------|-----------|-------------|---------|---------|

| Output Enable Access Time       | ta(OE)    | tGLQV       |         | 125     |

| Output Disable Time from OE     | tdis(OE)  | tGHQZ       |         | 100     |

| Address Setup Time              | tsu(A)    | tAVGL       | 30      |         |

| Address Hold Time               | th(A)     | tGHAX       | 20      |         |

| CE Setup before OE              | tsu(CE)   | tELGL       | 0       |         |

| CE Hold following OE            | th(CE)    | tGHEH       | 20      |         |

| Wait Delay Falling from OE      | tv(WT-OE) | tGLWTV      |         | 35      |

| Data Setup for Wait Release     | tv(WT)    | tQVWTH      |         | 0       |

| Wait Width Time (Default Speed) | tw(WT)    | tWTLWTH     |         | 350     |

Figure 4-3 Common Memory Read Timing Diagram

Notes: The maximum load on -WAIT is 1 LSTTL with 50pF total load. All times are in nanoseconds.

Dout signifies data provided by the CompactFlash Memory Card to the system.

The -WAIT signal may be ignored if the -OE cycle to cycle time is greater than the Wait Width time.

The Max Wait Width time (in the slowest mode) can be determined from the Card Information Structure.

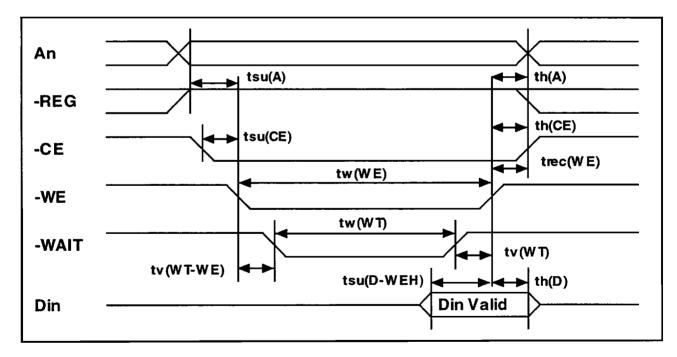

### 4.2.6 Common Memory Write Timing Specification

**Table 4-6 Common Memory Write Timing**

| Item                            | Symbol     | IEEE Symbol | Min ns. | Max ns. |

|---------------------------------|------------|-------------|---------|---------|

| Data Setup before WE            | tsu(D-WEH) | tDVWH       | 80      |         |

| Data Hold following WE          | th(D)      | tiWMDX      | 30      |         |

| WE Pulse Width                  | tw(WE)     | tWLWH       | 150     | -       |

| Address Setup Time              | tsu(A)     | tAVWL       | 30      |         |

| CE Setup before WE              | tsu(CE)    | tELWL       | 0       |         |

| Write Recovery Time             | trec(WE)   | tWMAX       | 30      |         |

| Address Hold Time               | th(A)      | tGHAX       | 20      |         |

| CE Hold following WE            | th(CE)     | tGHEH       | 20      |         |

| Wait Delay Falling from WE      | tv(WT-WE)  | tWLWTV      |         | 35      |

| WE High from Wait Release       | tv(WT)     | tWTHWH      | 0       |         |

| Wait Width Time (Default Speed) | tw (WT)    | tWTLWTH     |         | 350     |

Figure 4-4 Common Memory Write Timing Diagram

Notes: The maximum load on -WAIT is 1 LSTTL with 50pF total load. All times are in nanoseconds. Din signifies data provided by the system to the CompactFlash Memory Card.

The -WAIT signal may be ignored if the -WE cycle to cycle time is greater than the Wait Width time.

The Max Wait Width time (in the slowest mode) can be determined from the Card Information Structure.

#### 4.2.7 I/O Input (Read) Timing Specification

#### Table 4-7 I/O Read Timing

| Item                              | Symbol          | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|-----------------|-------------|---------|---------|

| Data Delay after IORD             | td(IORD)        | tIGLQV      |         | 100     |

| Data Hold following IORD          | th(IORD)        | tIGHQX      | 0       |         |

| IORD Width Time                   | tw(IORD)        | tIGLIGH     | 165     |         |

| Address Setup before IORD         | tsuA(IORD)      | tAVIGL      | 70      |         |

| Address Hold following IORD       | thA(IORD)       | tIGHAX      | 20      |         |

| CE Setup before IORD              | tsuCE(IORD)     | tELIGL      | 5       |         |

| CE Hold following IORD            | thCE(IORD)      | tIGHEH      | 20      |         |

| REG Setup before IORD             | tsuREG(IORD)    | tRGLIGL     | 5       |         |

| REG Hold following IORD           | thREG(IORD)     | tIGHRGH     | 0       |         |

| INPACK Delay Falling from IORD    | tdfINPACK(IORD) | tIGLIAL     | 0       | 45      |

| INPACK Delay Rising from IORD     | tdrlNPACK(IORD) | tIGHIAH     | I       | 45      |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR)  | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrlOlS16(ADR)  | tAVISH      |         | 35      |

| Wait Delay Falling from IORD      | tdWT(IORD)      | tiGLWTL     |         | 35      |

| Data Delay from Wait Rising       | td(WT)          | tWTHQV      |         | 0       |

| Wait Width Time (Default Speed)   | tw(WT)          | tWTLWTH     |         | 350     |

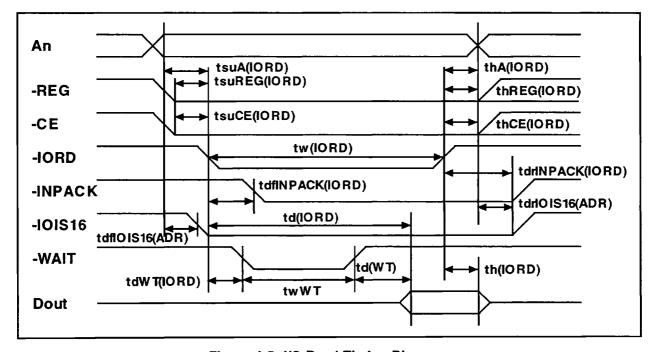

Figure 4-5 VO Read Timing Diagram

Notes: The maximum load on -WAIT, -INPACK and -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds.

Minimum time from -WAIT high to -IORD high is 0 nsec, but minimum -IORD width must still be met.

Dout signifies data provided by the CompactFlash Memory Card to the system.

#### 4.2.8 I/O Output (Write) Timing Specification

Table 4-8 I/O Write Timing

| Item                                                        | Symbol         | IEEE Symbol | Min ns. | Max ns.    |

|-------------------------------------------------------------|----------------|-------------|---------|------------|

| Data Setup before IOWR                                      | tsu(IOWR)      | tDVIWH      | 60      |            |

| Data Hold following IOWR                                    | th(IOWR)       | tfWHDX      | 30      |            |

| IOWR Width Time                                             | twIOWR         | tiWLIWH     | 165     |            |

| Address Setup before IOWR                                   | tsuA(IOWR)     | tAVIWL      | 70      |            |

| Address Hold following IOWR                                 | thA(IOWR)      | tiWHAX      | 20      |            |

| CE Setup before IOWR                                        | tsuCE(IOWR)    | tELIWL      | 5       |            |

| CE Hold following IOWR                                      | thCE(IOWR)     | tIWHEH      | 20      |            |

| REG Setup before IOWR                                       | tsuREG(IOWR)   | tRGLIWL     | 5       |            |

| REG Hold following IOWR                                     | thREG(IOWR)    | tWHRGH      | 0       |            |

| IOIS16 Delay Falling from Address                           | tdflOIS16(ADR) | tAVISL      |         | 35         |

| IOIS16 Delay Rising from Address                            | tdrlOIS16(ADR) | tAVISH      |         | 35         |

| Wait Delay Falling from IOWR                                | tdWT(IOWR)     | tIWLWTL     |         | 35         |

| IOWR high from Wait high                                    | tdrlOWR(WT)    | HWILTW      | 0       |            |

| Wait Width Time (Default Speed) (Set Feature Speed <68 mA.) | tw(WT)         | tWTLWTH     |         | 350<br>700 |

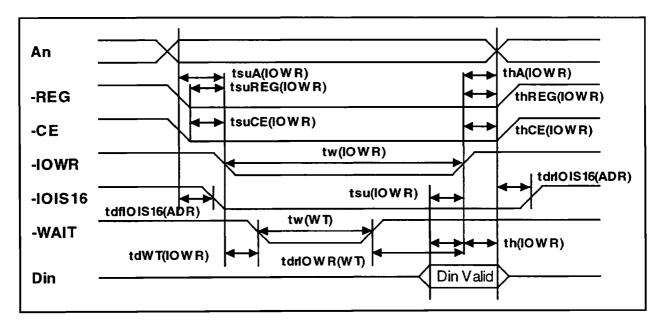

Figure 4-6 I/O Write Timing Diagram

Notes: The maximum load on -WAIT, -INPACK, and -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds.

Minimum time from -WAIT high to -!OWR high is 0 nsec, but minimum -IOWR width must still be met.

Din signifies data provided by the system to the CompactFlash Memory Card.

# 4.2.9 True IDE Mode I/O Input (Read) Timing Specification

Table 4-9 True IDE Mode I/O Read Timing

| ltem                              | Symbol         | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|----------------|-------------|---------|---------|

| Data Delay after IORD             | td(IORD)       | tIGLQV      |         | 100     |

| Data Hold following IORD          | th(IORD)       | tIGHQX      | 0       |         |

| IORD Width Time                   | tw(IORD)       | tIGLIGH     | 165     |         |

| Address Setup before IORD         | tsuA(IORD)     | tAVIGL      | 70      |         |

| Address Hold following IORD       | thA(IORD)      | tiGHAX      | 20      |         |

| CE Setup before IORD              | tsuCE(IORD)    | tELIGL      | 5       |         |

| CE Hold following IORD            | thCE(IORD)     | tIGHEH      | 20      |         |

| IOIS16 Delay Falling from Address | tdflOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrlOIS16(ADR) | tAVISH      |         | 35      |

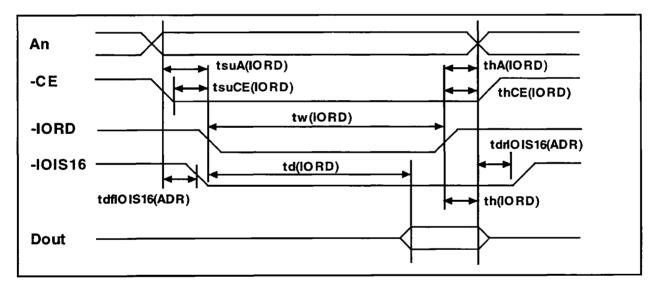

Figure 4-7 True IDE Mode I/O Read Timing Diagram

Notes: The maximum load on -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds.

Minimum time from -WAIT high to -IORD high is 0 nsec, but minimum -IORD width must still be met.

Dout signifies data provided by the CompactFlash Memory Card to the system.

# 4.2.10 True IDE Mode I/O Output (Write) Timing Specification

Table 4-10 True IDE Mode I/O Write Timing

| Item                              | Symbol         | IEEE Symbol | Min ns. | Max ns. |

|-----------------------------------|----------------|-------------|---------|---------|

| Data Setup before IOWR            | tsu(IOWR)      | tDVIWH      | 60      |         |

| Data Hold following IOWR          | th(IOWR)       | tlWHDX      | 30      |         |

| IOWR Width Time                   | tw(IOWR)       | tiWLIWH     | 165     |         |

| Address Setup before IOWR         | tsuA(iOWR)     | tAVIWL      | 70      |         |

| Address Hold following IOWR       | thA(IOWR)      | tiWHAX      | 20      | ···     |

| CE Setup before IOWR              | tsuCE(IOWR)    | tELIWL      | 5       |         |

| CE Hold following IOWR            | thCE(IOWR)     | tWHEH       | 20      |         |

| IOIS16 Delay Falling from Address | tdfIOIS16(ADR) | tAVISL      |         | 35      |

| IOIS16 Delay Rising from Address  | tdrlOIS16(ADR) | tAVISH      |         | 35      |

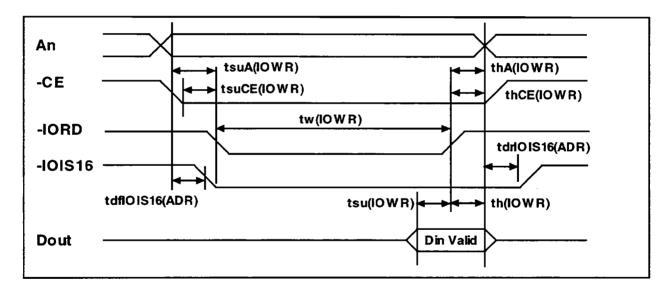

Figure 4-8 True IDE Mode I/O Write Timing Diagram

Notes: The maximum load on -IOIS16 is 1 LSTTL with 50pF total load. All times are in nanoseconds.

Minimum time from -WAIT high to -IOWR high is 0 nsec, but minimum -IOWR width must still be met.

Din signifies data provided by the system to the CompactFlash Memory Card.

#### 4.3 Card Configuration

The CompactFlash Memory Cards are identified by appropriate information in the Card Information Structure (CIS). The following configuration registers are used to coordinate the I/O spaces and the Interrupt level of cards that are located in the system. In addition, these registers provide a method for accessing status

information about the CompactFlash Card that may be used to arbitrate between multiple interrupt sources on the same interrupt level or to replace status information that appears on dedicated pins in memory cards that have alternate use in I/O cards.

Table 4-11 Registers and Memory Space Decoding

| -CE2 | -CE1 | -REG | -OE | -WE | A10 | Α9 | A8-A4 | А3 | A 2 | A1 | Α0 | SELECTED SPACE                       |

|------|------|------|-----|-----|-----|----|-------|----|-----|----|----|--------------------------------------|

| 1    | 1    | Х    | Х   | Х   | Х   | Х  | XX    | Х  | Х   | Х  | Х  | Standby                              |

| Х    | 0    | 0    | 0   | 1   | Х   | 1  | XX    | X  | Х   | Х  | 0  | Configuration Registers Read         |

| 1    | 0    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х   | Х  | Х  | Common Memory Read (8 Bit D7-D0)     |

| 0    | 1    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х   | Х  | Х  | Common Memory Read (8 Bit D15-D8)    |

| 0    | 0    | 1    | 0   | 1   | Х   | Х  | XX    | Х  | Х   | Х  | 0  | Common Memory Read (16 Bit D15-D0)   |

| Х    | 0    | 0    | 1   | 0   | Х   | 1  | XX    | Х  | Х   | Х  | 0  | Configuration Registers Write        |

| 1    | 0    | 1    | 1   | 0   | Х   | Х  | XX    | Х  | Х   | Х  | Х  | Common Memory Write (8 Bit D7-D0)    |

| 0    | 1    | 1    | 1   | 0   | Х   | X  | XX    | Х  | Х   | Х  | Х  | Common Memory Write (8 Bit D15-D8)   |

| 0    | 0    | 1    | 1   | 0   | Х   | Х  | XX    | Х  | Х   | Х  | 0  | Common Memory Write (16 Bit D15-D0)  |

| Х    | 0    | 0    | 0   | 1   | 0   | 0  | XX    | Х  | Х   | Х  | 0  | Card Information Structure Read      |

| 1    | 0    | 0    | 1   | 0   | 0   | 0  | XX    | Х  | Х   | Х  | 0  | Invalid Access (CIS Write)           |

| 1    | 0    | 0    | 0   | 1   | Х   | Х  | XX    | Х  | Х   | Х  | 1  | Invalid Access (Odd Attribute Read)  |

| 1    | 0    | 0    | 1   | 0   | Х   | Х  | XX    | Х  | Х   | Х  | 1  | Invalid Access (Odd Attribute Write) |

| 0    | 1    | 0    | 0   | 1   | Х   | Х  | XX    | Х  | Х   | Х  | Х  | Invalid Access (Odd Attribute Read)  |

| 0    | 1    | 0    | 1   | 0   | х   | Х  | ХХ    | Х  | Х   | х  | Х  | Invalid Access (Odd Attribute Write) |

**Configuration Registers Decoding**

|      | Jarano |      |     |     |     |            |       |    |     | _   | _  |                                |

|------|--------|------|-----|-----|-----|------------|-------|----|-----|-----|----|--------------------------------|

| -CE2 | -CE1   | -REG | -OE | -WE | A10 | <b>A</b> 9 | A8-A4 | А3 | A 2 | A 1 | ΑO | SELECTED REGISTER              |

| Х    | 0      | 0    | 0   | 1   | 0   | 1          | 00    | 0  | 0   | 0   | 0  | Configuration Option Reg Read  |

| Х    | 0      | 0    | 1   | 0   | 0   | 1          | 00    | 0  | 0   | 0   | 0  | Configuration Option Reg Write |

| Х    | 0      | 0    | 0   | 1   | 0   | 1          | 00    | 0  | 0   | 1   | 0  | Card Status Register Read      |

| Х    | 0      | 0    | 1   | 0   | 0   | 1          | 00    | 0  | 0   | 1   | 0  | Card Status Register Write     |

| X    | 0      | 0    | 0   | 1   | 0   | 1          | 00    | 0  | 1   | 0   | 0  | Pin Replacement Register Read  |

| Х    | 0      | 0    | 1   | 0   | 0   | 1          | 00    | 0  | 1   | 0   | 0  | Pin Replacement Register Write |

| Х    | 0      | 0    | 0   | 1   | 0   | 1          | 00    | 0  | 1   | 1   | 0  | Socket and Copy Register Read  |

| Х    | 0      | 0    | 1   | 0   | 0   | 1          | 00    | 0  | 1   | 1   | 0  | Socket and Copy Register Write |

Note: The location of the card configuration registers should always be read from the CIS since these locations may vary in future products. No writes should be performed to the CompactFlash Memory Card attribute memory except to the card configuration register addresses. All other attribute memory locations are reserved.

#### 4.3.1 Attribute Memory Function

Attribute memory is a space where CompactFlash Memory Card identification and configuration information is stored, and is limited to 8-bit wide accesses only at even addresses. The card configuration registers are also located here.

For the Attribute Memory Read function, signals -REG and -OE must be active and -WE inactive

during the cycle. As in the Main Memory Read functions, the signals -CE1 and -CE2 control the even-byte and odd-byte address, but only the even-byte data is valid during the Attribute Memory access. Refer to Table 4-12 below for signal states and bus validity for the Attribute Memory function.

**Table 4-12 Attribute Memory Function**

| Function Mode                                | -REG | -CE2 | -CE1 | A 9 | Α0 | -0E        | -WE | D15-D8     | D7-D0     |

|----------------------------------------------|------|------|------|-----|----|------------|-----|------------|-----------|

| Standby Mode                                 | Х    | Н    | Н    | Х   | Х  | Х          | Х   | High Z     | High Z    |

| Read Byte Access<br>CIS ROM (8 bits)         |      | Ι    | ٦    | لد  | L  | L          | Ι   | High Z     | Even Byte |

| Write Byte Access<br>CIS (8 bits) (Invalid)  | L    | Ι    |      | L   | L  | Н          | L   | Don't Care | Even Byte |

| Read Byte Access<br>Configuration (8 bits)   | L    | Ξ    |      | Ξ   | L  | L          | Н   | High Z     | Even Byte |

| Write Byte Access<br>Configuration (8 bits)  | L    | Н    | L    | Н   | L  | н          | L   | Don't Care | Even Byte |

| Read Word Access<br>CIS (16 bits)            | L    | L    | L    | L   | Х  | <b>L</b> . | Н   | Not Valid  | Even Byte |

| Write Word Access<br>CIS (16 bits) (Invalid) | L    | L    | ٦    | L   | Х  | н          | L   | Don't Care | Even Byte |

| Read Word Access<br>Configuration (16 bits)  | L    | -    | L    | H   | Х  | L          | н   | Not Valid  | Even Byte |

| Write Word Access<br>Configuration (16 bits) | L    | L    | L    | Н   | Х  | Н          | L   | Don't Care | Even Byte |

Note: The -CE signal or both the -OE signal and the -WE signal must be de-asserted between consecutive cycle operations.

### 4.3.2 Configuration Option Register (Address 200h in Attribute Memory)

The Configuration Option Register is used to configure the cards interface, address decoding and interrupt and to issue a soft reset to the CompactFlash Memory Card.

| Operation | <b>D</b> 7 | D6      | D5    | D4    | D3    | D2    | D1    | DO    |

|-----------|------------|---------|-------|-------|-------|-------|-------|-------|

| R/W       | SRESET     | LevIREQ | Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 |

SRESET

Soft Reset - Setting this bit to one (1), waiting the minimum reset width time and returning to zero (0) places the CompactFlash Memory Card in the Reset state. Setting this bit to one (1) is equivalent to assertion of the +RESET signal except that the SRESET bit is not cleared. Returning this bit to zero (0) leaves the CompactFlash Memory Card in the same un-configured, Reset state as following power-up and hardware reset. This bit is set to zero (0) by power-up and hardware reset. Using the PCMCIA Soft Reset is considered a hard Reset by the ATA Commands. Contrast with Soft Reset in the Device Control Register.

LevIREQ

This bit is set to one (1) when Level Mode Interrupt is selected, and zero (0) when Pulse Mode is selected. Set to zero (0) by Reset.

Conf5 - Conf0

Configuration Index. Set to zero (0) by reset. It's used to select operation mode of the CompactFlash Memory Card as shown below.

Note: Conf5 and Conf4 are reserved and must be written as zero (0)

**Table 4-13 Card Configurations**

| Conf5 | Conf4 | Conf3 | Conf2 | Conf1 | Conf0 | Disk Card Mode                                  |

|-------|-------|-------|-------|-------|-------|-------------------------------------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | Memory Mapped                                   |

| 0     | 0     | 0     | 0     | 0     | 1     | I/O Mapped, Any 16 byte system decoded boundary |

| 0     | 0     | 0     | 0     | 1     | 0     | I/O Mapped, 1F0-1F7/3F6-3F7                     |

| 0     | 0     | 0     | 0     | 1     | 1     | I/O Mapped, 170-177/376-377                     |

### 4.3.3 Card Configuration and Status Register (Address 202h in Attribute Memory)

The Card Configuration and Status Register contains information about the Card's condition.

Card Configuration and Status Register Organization:

| Operation | D7      | D6     | D5    | D4 | D3 | D2     | D1  | DO |

|-----------|---------|--------|-------|----|----|--------|-----|----|

| Read      | Changed | SigChg | IOis8 | 0  | 0  | PwrDwn | Int | 0  |

| Write     | 0       | SigChg | lOis8 | 0  | 0  | PwrDwn | 0   | 0  |

Changed

Indicates that one or both of the Pin Replacement register CRdy, or CWProt bits are set to one (1). When the Changed bit is set, -STSCHG Pin 46 is held low if the SigChg bit is a One (1) and the CompactFlash Memory Card is configured for the I/O interface.

SigChg

This bit is set and reset by the host to enable and disable a state-change "signal" from the Status Register, the Changed bit control pin 46 the Changed Status signal. If no state change signal is desired, this bit should be set to zero (0) and pin 46 (-STSCHG) signal will be held high while the CompactFlash Memory Card is configured for I/O.

IOis8

The host sets this bit to a one (1) if the CompactFlash Memory Card is to be configured in an 8 bit I/O mode. The CompactFlash Card is always configured for both 8- and 16-bit I/O, so this bit is ignored.

PwrDwn

This bit indicates whether the host requests the CompactFlash Memory Card to be in the power saving or active mode. When the bit is one (1), the CompactFlash Card enters a power down mode. When zero (0), the host is requesting the CompactFlash Card to enter the active mode. The PCMCIA Rdy/-Bsy value becomes BUSY when this bit is changed. Rdy/-Bsy will not become Ready until the power state requested has been entered. The CompactFlash Card automatically powers down when it is idle and powers back up when it receives a command.

Int

This bit represents the internal state of the interrupt request. This value is available whether or not I/O interface has been configured. This signal remains true until the condition which caused the interrupt request has been serviced. If interrupts are disabled by the -IEN bit in the Device Control Register, this bit is a zero (0).

### 4.3.4 Pin Replacement Register (Address 204h in Attribute Memory)

| Operation | D7 | D6 | <b>D</b> 5 | D4     | D3 | D2 | D1        | D0     |

|-----------|----|----|------------|--------|----|----|-----------|--------|

| Read      | 0  | 0  | CRdy/-Bsy  | CWProt | 1  | 1  | Rdy/-Bsy  | WProt  |

| Write     | 0  | 0  | CRdy/-Bsy  | CWProt | 0  | 0  | MRdy/-Bsy | MWProt |

CRdy/-Bsy

This bit is set to one (1) when the bit RRdy/-Bsy changes state. This bit can also be written by the host.

**CWProt**

This bit is set to one (1) when the RWprot changes state. This bit may also be written by the host.

Rdy/-Bsy

This bit is used to determine the internal state of the Rdy/-Bsy signal. This bit may be used to determine the state of the Ready/-Busy as this pin has been reallocated for use as Interrupt Request on an I/O card. When written, this bit acts as a mask for writing the corresponding bit CRdy/-Bsy.

**WProt**

This bit is always zero (0) since the CompactFlash Memory Card does not have a Write Protect switch. When written, this bit acts as a mask for writing the corresponding bit CWProt.

MRdy/-Bsy

This bit acts as a mask for writing the corresponding bit CRdy/-Bsy.

**MWProt**

This bit when written acts as a mask for writing the corresponding bit CWProt.

Table 4-14 Pin Replacement Changed Bit/Mask Bit Values

| Initial Value | Written by Host |         | Final   | Comments        |

|---------------|-----------------|---------|---------|-----------------|

| of (C) Status | "C" Bit         | "M" Bit | "C" Bit |                 |

| 0             | Х               | 0       | 0       | Unchanged       |

| 1             | X               | 0       | 1       | Unchanged       |

| ×             | 0               | 1       | 0       | Cleared by Host |

| X             | 1               | 1       | 1       | Set by Host     |

## 4.3.5 Socket and Copy Register (Address 206h in Attribute Memory)

This register contains additional configuration the system before writing the card's Configuration information. This register is always written by Index Register.

Socket and Copy Register Organization:

| Operation | <b>D</b> 7 | D6 | D5 | D4          | D3 | D2 | D1 | D0 |

|-----------|------------|----|----|-------------|----|----|----|----|

| Read      | Reserved   | 0  | 0  | Drive #     | 0  | 0  | 0  | 0  |

| Write     | 0          | 0  | 0  | Drive # (0) | Х  | Х  | Х  | Х  |

**Reserved** This bit is reserved for future standardization. This bit must be set to zero (0) by the software when the register is written.

**Drive** # This bit indicates the drive number of the card if twin card configuration is supported.

X The socket number is ignored by the CompactFlash Memory Card.

#### 4.4 I/O Transfer Function

#### 4.4.1 I/O Function

The I/O transfer to or from the CompactFlash Memory Card can be either 8 or 16 bits. When a 16-bit accessible port is addressed, the signal -IOIS16 is asserted by the CompactFlash Card. Otherwise, the -IOIS16 signal is de-asserted. When a 16 bit transfer is attempted, and the -IOIS16 signal is not asserted by the CompactFlash Card, the system must generate a pair of 8-bit references to access the word's even

byte and odd byte. The CompactFlash Card permits both 8 and 16 bit accesses to all of its I/O addresses, so -IOIS16 is asserted for all addresses to which the CompactFlash Card responds.

The CompactFlash Memory Card may request the host to extend the length of an input cycle until data is ready by asserting the -WAIT signal at the start of the cycle.

Table 4-15 VO Function

| Function Code                        | -REG  | -CE2 | -CE1   | A0 | -IORD | -IOWR | D15-D8                   | D7-D0                 |

|--------------------------------------|-------|------|--------|----|-------|-------|--------------------------|-----------------------|

| Standby Mode                         | Х     | Н    | Ι      | Х  | X     | Х     | High Z                   | High Z                |

| Byte Input Access (8 bits)           | اد اد | ΞΞ   | ا۔ ا   | ıπ | ا ا   | ΙI    | High Z<br>High Z         | Even-Byte<br>Odd-Byte |

| Byte Output<br>Access<br>(8 bits)    | L     | II   | ا د اد | Ξ  | ΙΙ    | -J -J | Don't Care<br>Don't Care | Even-Byte<br>Odd-Byte |

| Word Input<br>Access<br>(16 bits)    | L     | L    | L      | L  | L     | H     | Odd-Byte                 | Even-Byte             |

| Word Output<br>Access<br>(16 bits)   | L     | ٠    | اد     |    | Τ     | L     | Odd-Byte                 | Even-Byte             |

| I/O Read Inhibit                     | Н     | Х    | X      | X  | L     | Н     | Don't Care               | Don't Care            |

| I/O Write Inhibit                    | Н     | Х    | Х      | X  | H     | L     | High Z                   | High Z                |

| High Byte Input<br>Only<br>(8 bits)  | L     | L    | Ħ      | Х  | L     | H     | Odd-Byte                 | High Z                |

| High Byte Output<br>Only<br>(8 bits) | Ĺ     | L    | Н      | X  | Н     | L     | Odd-Byte                 | Don't Care            |

#### 4.5 Common Memory Transfer Function

#### 4.5.1 Common Memory Function

The Common Memory transfer to or from the CompactFlash Memory Card can be either 8 or 16 bits.

The CompactFlash Memory Card permits both 8 and 16 bit accesses to all of its Common Memory addresses.

The CompactFlash Memory Card may request the host to extend the length of a memory write cycle or extend the length of a memory read cycle until data is ready by asserting the -WAIT signal at the start of the cycle.

**Table 4-16 Common Memory Function**

| Function Code                   | -REG | -CE2 | -CE1   | A 0    | -OE    | -WE    | D15-D8                   | D7-D0                 |

|---------------------------------|------|------|--------|--------|--------|--------|--------------------------|-----------------------|

| Standby Mode                    | Х    | Н    | Н      | Х      | X      | Х      | High Z                   | High Z                |

| Byte ReadAccess<br>(8 bits)     | H    | H    | L<br>L | L      | L<br>L | H<br>H | High Z<br>High Z         | Even-Byte<br>Odd-Byte |

| Byte Write Access<br>(8 bits)   | H    | H    | L<br>L | L<br>H | H      | L<br>L | Don't Care<br>Don't Care | Even-Byte<br>Odd-Byte |

| Word Read Access<br>(16 bits)   | Н    | L    | L      | Х      | L      | Н      | Odd-Byte                 | Even-Byte             |

| Word Write Access<br>(16 bits)  | Н    | L    | L      | Х      | Н      | L      | Odd-Byte                 | Even-Byte             |

| Odd Byte Read Only<br>(8 bits)  | Н    | L    | Н      | Х      | L      | Н      | Odd-Byte                 | High Z                |

| Odd Byte Write Only<br>(8 bits) | Н    | L    | Н      | ×      | Н      | L      | Odd-Byte                 | Don't Care            |

#### 4.6 True IDE Mode I/O Transfer Function

#### 4.6.1 True IDE Mode I/O Function

The CompactFlash Memory Card can be configured in a True IDE Mode of operation. This CompactFlash Card is configured in this mode only when the -OE input signal is grounded by the host. In this True IDE Mode, the PCMCIA protocol and configuration are disabled and only I/O operations to the Task File and Data Register are allowed. In this mode, no Memory or Attribute Registers are accessible to the host. CompactFlash Cards permit 8 bit data accesses if the user issues a Set Feature Command to put the device in 8 bit Mode.

Note: Removing and reinserting the CompactFlash Memory Card while the host computer's power is on will reconfigure the CompactFlash Card to PC Card ATA mode from the original True IDE Mode. To configure the CompactFlash Card in True IDE Mode, the 68-pin socket must be power cycled with the CompactFlash Card inserted and -OE

The following table defines the function of the operations for the True IDE Mode.

(output enable) grounded by the host.

Table 4-17 IDE Mode I/O Function

| Function Code             | -CE2 | -CE1 | A 0  | -IORD | -IOWR | D15-D8          | D7-D0            |

|---------------------------|------|------|------|-------|-------|-----------------|------------------|

| Invalid Mode              | L    | L    | Х    | Х     | X     | High Z          | High Z           |

| Standby Mode              | Н    | Н    | Х    | Х     | Х     | High Z          | High Z           |

| Task File Write           | Н    | L    | 1-7h | Н     | L     | Don't Care      | Data In          |

| Task File Read            | Н    | L    | 1-7h | L     | Н     | High Z          | Data Out         |

| Data Register<br>Write    | Н    | L    | 0    | н     | L     | Odd-Byte<br>In  | Even-Byte<br>In  |

| Data Register<br>Read     | Н    | L    | 0    | L     | н     | Odd-Byte<br>Out | Even-Byte<br>Out |

| Control Register<br>Write | L    | Н    | 6h   | Н     | L     | Don't Care      | Control In       |

| Alt Status Read           | L    | Н    | 6h   | L     | Н     | High Z          | Status Out       |