# Satellite Channel Decoder

**Design Manual**

Supersedes DS5347 Issue 1.2 November 2001

## **Key Features**

- Conforms to EBU specification for DVB-S and DirecTV specification for DSS.

- On-chip digital filtering supports 1 to 45MBaud Symbol rates.

- On-chip 6-bit 60 or 90MHz dual-ADC.

- High speed scanning mode for blind symbol rate/code rate acquisition.

- Automatic IQ phase resolution.

- No signal indicator.

- Up to ±15MHz LNB frequency tracking.

- Fully digital timing and phase recovery loops.

- High level software interface for minimum development time.

- DiSEqC<sup>™</sup> v2.2: receive/transmit for full control of LNB and dish.

## **Applications**

- DVB 1 to 45MBaud compliant satellite receivers.

- DSS 20MBaud compliant satellite receivers.

- SCPC receivers. (Single Channel Per Carrier)

- SMATV trans-modulators. (Single Master Antenna TV)

- LMDS (Local Multipoint Distribution Service)

- Satellite PC applications.

Ordering Information

MT312C/CG/GP1N

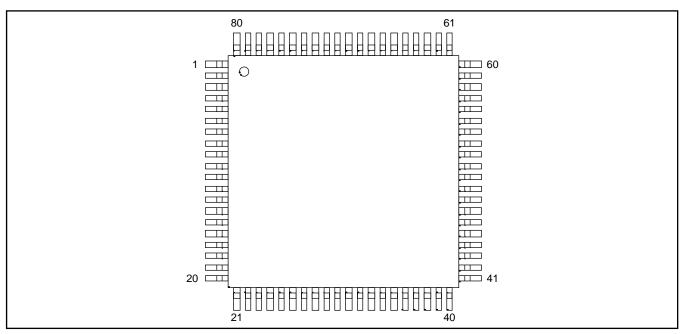

The MT312 is a QPSK/BPSK 1 to 45MBaud demodulator and channel decoder for digital satellite television transmissions to the European Broadcast Union ETS 300 421 specification (ref. 1). It receives analogue I and Q signals from the tuner, digitises demodulates this digitally signal. implements the complete DVB/DSS FEC (Forward Error Correction), and de-scrambling function. The output is in the form of MPEG2 or DSS transport stream data packets. An external MPEG clock input is provided for synchronisation to MPEG decoders and DVB Common Interface Modules. The MT312 also provides automatic gain control to the RF frontend devices.

The MT312 has a serial 2-wire bus interface to the control microprocessor. Minimal software is required to control the MT312 because of the built in automatic search and decode control functions.

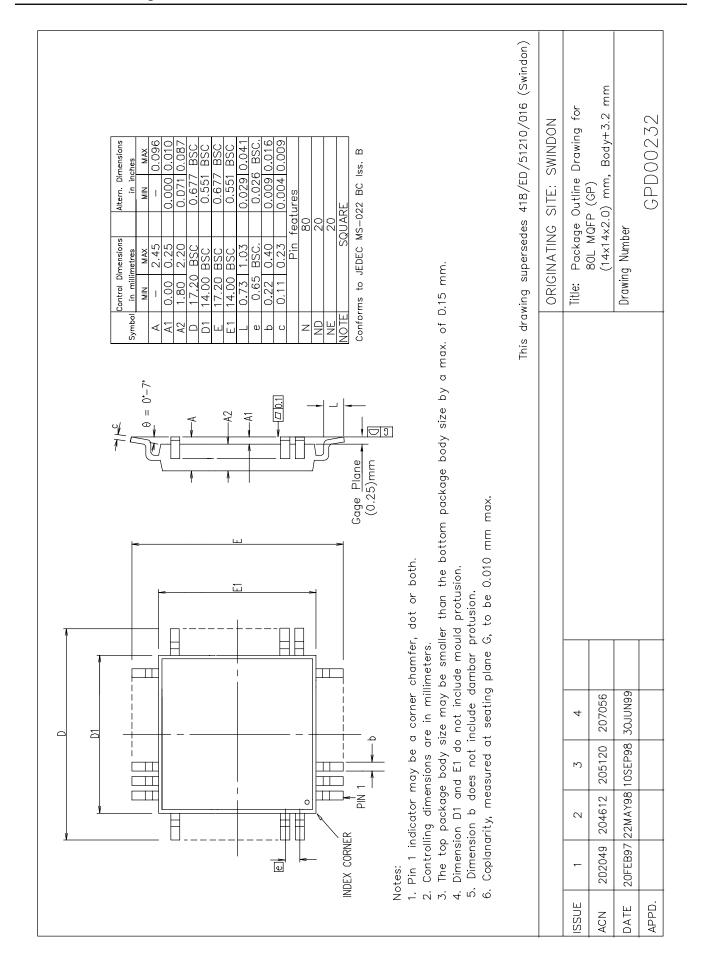

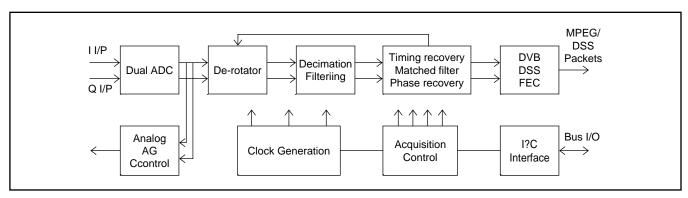

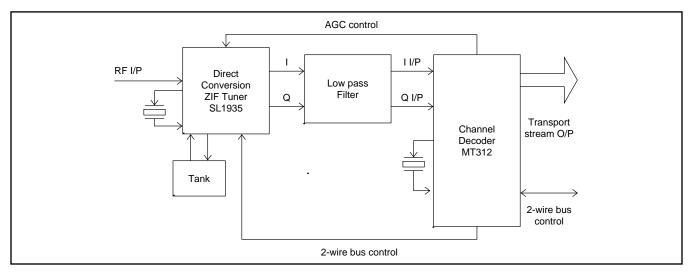

Figure 1 - System Block Diagram - SNIM5

Figure 2 - System Block Diagram - SNIM5

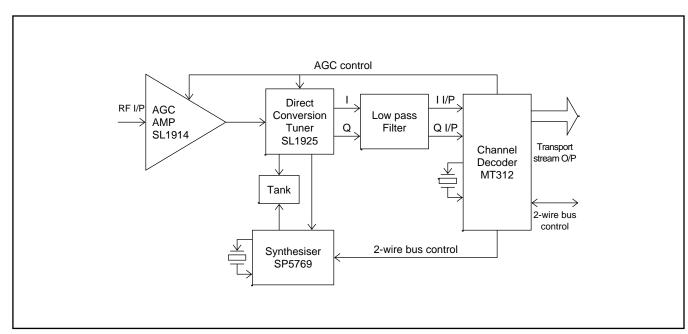

| PIN | FUNCTION | PIN | FUNCTION | PIN | FUNCTION      | PIN | FUNCTION |

|-----|----------|-----|----------|-----|---------------|-----|----------|

| 1   | CVSS     | 21  | PLLVDD   | 41  | CVSS          | 61  | MDO[1]   |

| 2   | CVDD     | 22  | PLLGND   | 42  | CVDD          | 62  | CVDD     |

| 3   | IIN[1]   | 23  | PLL1     | 43  | AGC           | 63  | MDO[2]   |

| 4   | ADDR[7]  | 24  | ADCFGND  | 44  | CLK2/GPP0     | 64  | MDO[3]   |

| 5   | ADDR[6]  | 25  | ADCFVDD  | 45  | DATA2/GPP1    | 65  | MDO[4]   |

| 6   | ADDR[5]  | 26  | VRT      | 46  | DISEQC2/GPP2  | 66  | MDO[5]   |

| 7   | ADDR[4]  | 27  | IREF     | 47  | DISEQC1 HV    | 67  | CVDD     |

| 8   | ADDR[3]  | 28  | ISINGP   | 48  | DISEQC0 22kHz | 68  | MDO[6]   |

| 9   | CVDD     | 29  | NC       | 49  | RESET         | 69  | MDO[7]   |

| 10  | CVSS     | 30  | ADCDVDD  | 50  | CVDD          | 70  | CVSS     |

| 11  | ADDR[2]  | 31  | ADCDGND  | 51  | CVSS          | 71  | MDOEN    |

| 12  | ADDR[1]  | 32  | VRM      | 52  | STATUS        | 72  | MOVAL    |

| 13  | VDD      | 33  | QSINGP   | 53  | CLK1          | 73  | VDD      |

| 14  | MICLK    | 34  | QREF     | 54  | DATA1         | 74  | VSS      |

| 15  | VSS      | 35  | VRB      | 55  | CVDD          | 75  | BKERR    |

| 16  | TESTCLK  | 36  | ADCAGND  | 56  | VSS           | 76  | MOSTRT   |

| 17  | CVDD     | 37  | ADCAVDD  | 57  | ĪRQ           | 77  | IIN[5]   |

| 18  | XTI      | 38  | RREF     | 58  | MOCLK         | 78  | IIN[4]   |

| 19  | XTO      | 39  | TEST1    | 59  | MDO[0]        | 79  | IIN[3]   |

| 20  | CVSS     | 40  | TEST2    | 60  | CVSS          | 80  | IIN[2]   |

Table 1 - MT312 pin-out

#### **Quick start overview**

The MT312 is a QPSK/BPSK 1 to 45MBaud demodulator and channel decoder for digital satellite television transmissions compliant to both DVB-S and DSS standards and other systems, such as LMDS, that use the same architecture.

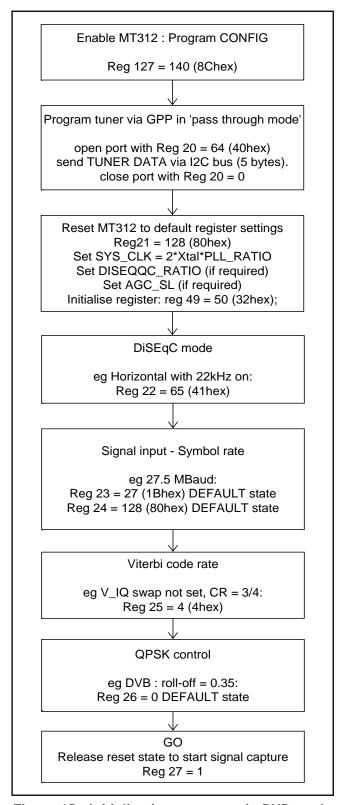

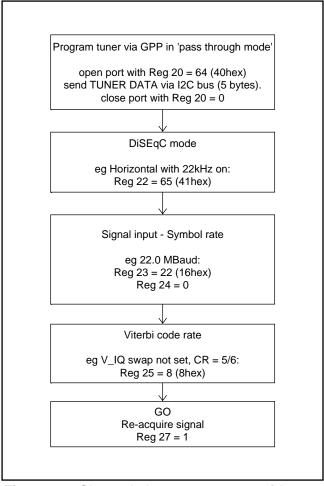

A Command Driven Control (CDC) system is provided making the MT312 very simple to program. After the tuner has been programmed to the required frequency, to acquire a DVB transmission, the MT312 requires a minimum of five registers to be written. Activity flow diagrams for initialisation and basic channel change are included in section 2.

The MT312 provides a monitor of Bit Error Rate after the QPSK module and also after the Viterbi module.

For receiver installation, a high speed scan or 'blind search' mode is available. This allows all signals from a given satellite to be evaluated for frequency, symbol rate and convolutional coding scheme. The phase of the IQ signals can be automatically determined.

Full DiSEqC™ v2.2 is provided for both writing and reading DiSEqC™ messages. Storage in registers for up to eight data bytes sent and eight data bytes received is provided.

Figure 3 - MT312 Functional Block Diagram

#### **Additional Features**

- 2-wire bus microprocessor interface.

- All digital clock and carrier recovery.

- On-chip PLL clock generation using low cost 10 to 15MHz crystal.

- 3.3V operation.

- 80 pin MQFP package.

- Low external component count.

- Commercial temperature range 0 to 70°C.

#### **Demodulator**

- · BPSK or QPSK programmable.

- Optional fast acquisition mode for low symbol rates.

#### Viterbi

- Programmable decoder rates 1/2, 2/3, 3/4, 5/6, 6/7, 7/8.

- Automatic spectrum resolution of IQ phase.

- Constraint length k=7.

- Trace back depth 128.

- · Extensive SNR and BER monitors.

#### De-Interleaver

Compliant with DVB and DSS standards.

#### **Reed Solomon**

- (204, 188) for DVB and (146,130) for DSS.

- Reed Solomon Bit-error-rate monitor to indicate Viterbi performance.

#### De-Scrambler

EBU specification De-scrambler for DVB mode.

#### **Outputs**

- MPEG transport parallel & serial output.

- MPEG clock input for external synchronising of MPEG data output.

- Integrated MPEG2 TEI bit processing for DVB only.

## **Application Support**

- Channel decoder system evaluation board.

- Windows based evaluation software.

- ANSI C generic software.

# MT312 Contents

# Contents

| 1       | Functional Overview                                 | 10 |

|---------|-----------------------------------------------------|----|

| 1.1     | Introduction                                        | 10 |

| 1.2     | Analogue-to-Digital Converter                       | 10 |

| 1.3     | QPSK Demodulator                                    | 10 |

| 1.4     | Forward Error Correction                            | 11 |

| 1.4.1.1 | Viterbi Error Count Measurement                     | 11 |

| 1.4.1.2 | Viterbi Error Count Coarse Indication               | 12 |

| 1.4.2   | The Frame Alignment Block                           | 12 |

| 1.4.3   | The De-interleaver Block                            | 13 |

| 1.4.3.1 | DVB                                                 | 13 |

| 1.4.3.2 | DSS                                                 | 13 |

| 1.4.4   | The Reed Solomon Decoder Block                      | 14 |

| 1.4.5   | The Energy Dispersal (De-Scrambler) Block, DVB only | 14 |

| 1.4.6   | Output Stage                                        | 15 |

| 1.5     | Control                                             |    |

| 1.5.2   | Symbol Rate and Code Rate Search Mode               | 16 |

| 1.6     | Direct Conversion Application                       | 16 |

| 1.7     | DiSEqC™ Transmit and Receive Messages               | 17 |

| 1.7.1   | DiSEqC™ Transmitting Messages                       | 17 |

| 1.7.2   | DiSEqC™ Receiving Messages                          | 17 |

| 2       | MT312 Software Control                              | 18 |

| 2.1     | MT312 Register Map Overview                         |    |

|         |                                                     |    |

| 3       | MT312 Initialisation                                | 19 |

| 3.1     | The Configuration Register (127)                    |    |

| 3.2     | Power Supplies                                      |    |

| 3.3     | Initialisation Sequence                             |    |

| 3.4     | Spectral Inversion                                  |    |

| 3.5     | MT312 Initialisation Read/Write Registers           |    |

| 3.5.1   | Reset. Register 21 (R/W)                            |    |

| 3.5.2   | MT312 Configuration. Register 127 (R/W)             |    |

| 3.5.3   | System Clock Frequency. Register 34 (R/W)           |    |

| 3.6     | MT312 Initialisation Read Register                  |    |

| 3.6.1   | Identification. Register 126 (R)                    |    |

| 4       | Tuner Control                                       | 24 |

| 4.1     | Simple Channel Change Sequence                      |    |

| 4.2     | Channel Change Sequence with a new Symbol Rate      |    |

| 4.3     | Channel Change Sequence with Search Mode            |    |

| 4.4     | Tuner Control Read/Write Registers                  |    |

| 4.4.1   | General Purpose Port Control. Register 20 (R/W)     |    |

| 4.4.2   | FR LIM: Frequency Limit. Register 37 (R/W)          |    |

| 4.4.3   | FR OFF: Frequency Offset. Register 38 (R/W)         |    |

| 4.5     | Tuner Control Read Registers                        |    |

| 4.5.1   | Measured LNB Frequency Error. Registers 7 - 8 (R)   |    |

| 452     | Frequency Error 1 and 2 Registers 111 - 115 (R)     | 28 |

Contents

| 5              | DiSEqC Control                                                         | 29 |

|----------------|------------------------------------------------------------------------|----|

| 5.1            | Screen Printouts of DiSEqC™ Waveforms                                  |    |

| 5.2            | DiSEqC Control Read/Write Registers                                    |    |

| 5.2.1          | DiSEqC™ Mode Control. Register 22 (R/W)                                | 30 |

| 5.2.2          | DiSEqC(tm) Ratio. Register 35 (R/W)                                    | 30 |

| 5.2.3          | DiSEqC™ Instruction (R/W). Register 36 (R/W)                           |    |

| 5.2.4          | DiSEqC <sup>™</sup> 2 Control 1. Registers 121 (R/W)                   | 31 |

| 5.2.5          | DiSEqCTM 2 Control 2. Registers 122 (R/W)                              |    |

| 5.3            | DiSEqC Control Read Registers                                          |    |

| 5.3.1          | DiSEqC™M 2 Interrupt Indicators. Register 118 (R)                      |    |

| 5.3.2<br>5.3.3 | DiSEqC™M 2 Status Indicators. Register 119 (R)                         |    |

|                |                                                                        |    |

| 6              | QPSK demodulator                                                       |    |

| 6.1            | QPSK Demodulator Read/Write Registers                                  |    |

| 6.1.1          | Symbol Rate. Registers 23 - 24 (R/W)                                   |    |

| 6.1.2          | Viterbi mode. Register 25 (R/W)                                        |    |

| 6.1.3          | QPSK Control. Register 26 (R/W)                                        |    |

| 6.1.4          | Go Command. Register 27 (R/W)                                          |    |

| 6.1.5          | QPSK Interrupt Output Enable. Registers 28 - 30 (R/W)                  |    |

| 6.1.6<br>6.2   | QPSK STATUS Output Enable. Register 32 (R/W)                           |    |

| 6.2.1          | QPSK Demodulator Read Registers                                        |    |

| 6.2.1          | QPSK Status. Registers 4 - 5 (R)                                       |    |

| 6.2.3          | Symbol Rate Output. Registers 116 - 117 (R)                            |    |

| 6.2.4          | Monitor Registers. Registers 123 - 124 (R)                             |    |

| _              |                                                                        |    |

| 7              | Forward Error Correction                                               |    |

| 7.1            | Forward Error Correction Read/Write Registers                          |    |

| 7.1.1          | FEC Interrupt Enable. Register 31 (R/W)                                |    |

| 7.1.2          | FEC STATUS Output Enable. Register 33 (R/W)                            |    |

| 7.1.3<br>7.2   | FEC Set Up. Register 97 (R/W)                                          |    |

| 7.2<br>7.2.1   | Forward Error Correction Read Registers  FEC Interrupt. Register 3 (R) |    |

| 7.2.1          | FEC Status. Register 6 (R)                                             |    |

| 7.2.2          | Measured Signal to Noise Ratio. Registers 9 - 10 (R)                   |    |

| 7.2.4          | Viterbi Error Count at Viterbi Input. Registers 11 - 13 (R)            |    |

| 7.2.5          | Reed Solomon Bit Errors Corrected. Registers 14 - 16 (R)               |    |

| 7.2.6          | Reed Solomon Uncorrected block Errors. Registers 17 - 18 (R)           |    |

| 8              | Automatic Gain Control                                                 | 52 |

| 8.1            | Automatic Gain Control Read/Write Registers                            |    |

| 8.1.1          | AGC Control. Register 39 (R/W)                                         |    |

| 8.1.2          | AGC REF Reference Value. Register 41 (R/W)                             |    |

| 8.2            | Automatic Gain Control Read Registers                                  |    |

| 8.2.1          | Measured Signal Level at MT312 Input. Register 19 (R)                  |    |

| 8.2.2          | Measured AGC Feed Back Value. Registers 108 - 110 (R)                  |    |

| 9              | MPEG Packet Data Ouput                                                 | 54 |

| 9.1            | MPEG Clock Modes                                                       |    |

| 9.2            | Data Output Header Format - DVB only                                   |    |

| 9.3            | MPEG/DSS Data Output Signals                                           |    |

| 9.4            | Data output timing                                                     |    |

| 9.5            | MPEG Packet Data Output Read/Write Registers                           |    |

| 9.5.1          | Output Data Control. Register 96 (R/W)                                 |    |

| 9.5.2          | Monitor Control. Register 103 (R/W)                                    |    |

# MT312 Contents

| 10      | Secondary Registers for Test and De-Bugging                                     | 61 |

|---------|---------------------------------------------------------------------------------|----|

| 10.1    | Read / Write Secondary Register Map                                             |    |

| 10.2    | Secondary Registers for Test and De-Bugging Read/Write Registers                |    |

| 10.2.1  | AGC Initial Value. Register 40 (R/W)                                            |    |

| 10.2.2  | AGC Maximum Value. Register 42 (R/W)                                            |    |

| 10.2.3  | AGC Minimum Value. Register 43 (R/W)                                            |    |

| 10.2.4  | AGC Lock Threshold Value. Register 44 (R/W)                                     |    |

| 10.2.5  | AGC Lock Threshold Value. Register 45 (R/W)                                     |    |

| 10.2.6  | AGC Power Setting Initial Value. Register 46 (R/W)                              |    |

| 10.2.7  | QPSK Miscellaneous. Register 47 (R/W)                                           |    |

| 10.2.8  | SNR Low Threshold Value. Register 48 (R/W)                                      |    |

| 10.2.9  | SNR HIGH Threshold Value. Register 49 (R/W)                                     |    |

| 10.2.10 | Timing Synchronisation Sweep Rate. Register 50 (R/W)                            |    |

| 10.2.11 | Timing Synchronisation Sweep Limit Low. Register 51 (R/W)                       |    |

| 10.2.12 | Timing Synchronisation Sweep Limit High. Register 52 (R/W)                      |    |

| 10.2.13 | Carrier Synchronisation Sweep Rate 1. Register 53 (R/W)                         |    |

| 10.2.14 | Carrier Synchronisation Sweep Rate 2. Register 54 (R/W)                         |    |

| 10.2.15 | Carrier Synchronisation Sweep Rate 3. Register 55 (R/W)                         |    |

| 10.2.16 | Carrier Synchronisation Sweep Rate 4. Register 56 (R/W)                         |    |

| 10.2.17 | Carrier Synchronisation Sweep Limit. Register 57 (R/W)                          |    |

| 10.2.18 | Timing Synchronisation Coefficients. Registers 58 - 60 (R/W)                    |    |

| 10.2.19 | Carrier Synchronisation Proportional Part Coefficients. Registers 61 - 62 (R/W) |    |

| 10.2.20 | Carrier Synchronisation Integral Coefficients. Registers 63 - 64 (R/W)          |    |

| 10.2.21 | QPSK Output Scale Factor. Register 65 (R/W)                                     |    |

| 10.2.22 | Timing Lock Detect Threshold out of lock. Register 66 (R/W)                     |    |

| 10.2.23 | Timing Lock Detect Threshold in lock. Register 67 (R/W)                         |    |

| 10.2.24 | Frequency Lock Detect Threshold. Register 68                                    |    |

| 10.2.25 | Phase Lock Detect Threshold out of lock. Registers 69 - 72 (R/W)                |    |

| 10.2.26 | Phase Lock Detect Threshold in lock. Registers 73 - 76 (R/W)                    |    |

| 10.2.27 | Phase Lock Detect Accumulator Time. Register 77 (R/W)                           |    |

| 10.2.28 | Sweep PAR. Register 78 (R/W)                                                    |    |

| 10.2.29 | Start up Time. Register 79 (R/W)                                                | 68 |

| 10.2.30 | Loss Lock Threshold. Register 80 (R/W)                                          |    |

| 10.2.31 | FEC Lock Time. Register 81 (R/W)                                                | 68 |

| 10.2.32 | Loss Lock Time. Register 82 (R/W)                                               | 69 |

| 10.2.33 | Viterbi Error Period. Registers 83 - 85 (R/W)                                   | 69 |

| 10.2.34 | Viterbi Set up. Register 86 (R/W)                                               | 69 |

| 10.2.35 | Viterbi Reference Byte 0. Register 87 (R/W)                                     | 70 |

| 10.2.36 | Viterbi Reference Byte 1. Register 88 (R/W)                                     | 70 |

| 10.2.37 | Viterbi Reference Byte 2. Register 89 (R/W)                                     | 70 |

| 10.2.38 | Viterbi Reference Byte 3. Register 90 (R/W)                                     | 70 |

| 10.2.39 | Viterbi Reference Byte 4. Register 91 (R/W)                                     | 70 |

| 10.2.40 | Viterbi Reference Byte 5. Register 92 (R/W)                                     | 70 |

| 10.2.41 | Viterbi Reference Byte 6. Register 93 (R/W)                                     | 70 |

| 10.2.42 | Viterbi Maximum Error. Register 94 (R/W)                                        |    |

| 10.2.43 | Byte Align Set up. Register 95 (R/W)                                            |    |

| 10.2.44 | Program Synchronising Byte. Register 98 (R/W)                                   |    |

| 10.2.45 | AFC Frequency Search Threshold. Register 99 (R/W)                               |    |

| 10.2.46 | Accumulator Differential Threshold. Register 100 (R/W)                          |    |

| 10.2.47 | QPSK Lock Control. Register 101 (R/W)                                           |    |

| 10.2.48 | QPSK State Control. Register 102 (R/W)                                          |    |

| 10.2.49 | QPSK Reset. Register 104 (R/W)                                                  |    |

| 10.2.50 | QPSK Test Control. Register 105 (R/W)                                           |    |

| 10.2.51 | QPSK Test State. Register 106 (R/W)                                             |    |

| 10.2.52 | Test Mode. Register 125 (R/W)                                                   |    |

| 10.3    | Read only Secondary Register Map                                                |    |

| 10.4    | Secondary Registers for Test and De-Bugging Read Register                       |    |

| 10.4.1  | Test Read. Register 107 (R)                                                     | 73 |

| 11   | Microprocessor Control                 | 74 |

|------|----------------------------------------|----|

| 11.1 | Primary 2-wire bus interface           |    |

| 11.2 | RADD: 2-Wire Register Address (W)      |    |

| 11.3 | Primary 2-Wire Bus Interface           |    |

| 11.4 | Secondary 2-Wire Bus for Tuner Control |    |

| 11.5 | Examples of 2-Wire Bus Messages        |    |

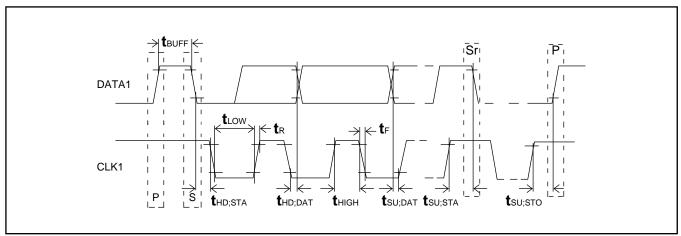

| 11.6 | Primary 2-Wire Bus Timing              |    |

| 12   | Electrical Characteristics             | 78 |

| 12.1 | Recommended Operating Conditions       |    |

| 12.2 | Absolute Maximum Ratings               |    |

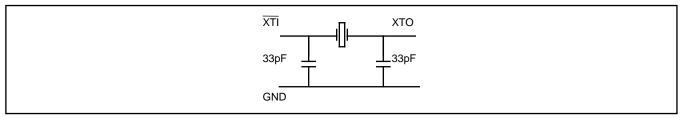

| 12.3 | Crystal Specification                  |    |

| 12.4 | DC Electrical Characteristics          |    |

| 12.5 | MT312 Pinout Description               |    |

| 12.6 | Alphabetical Listing of Pin-Out        |    |

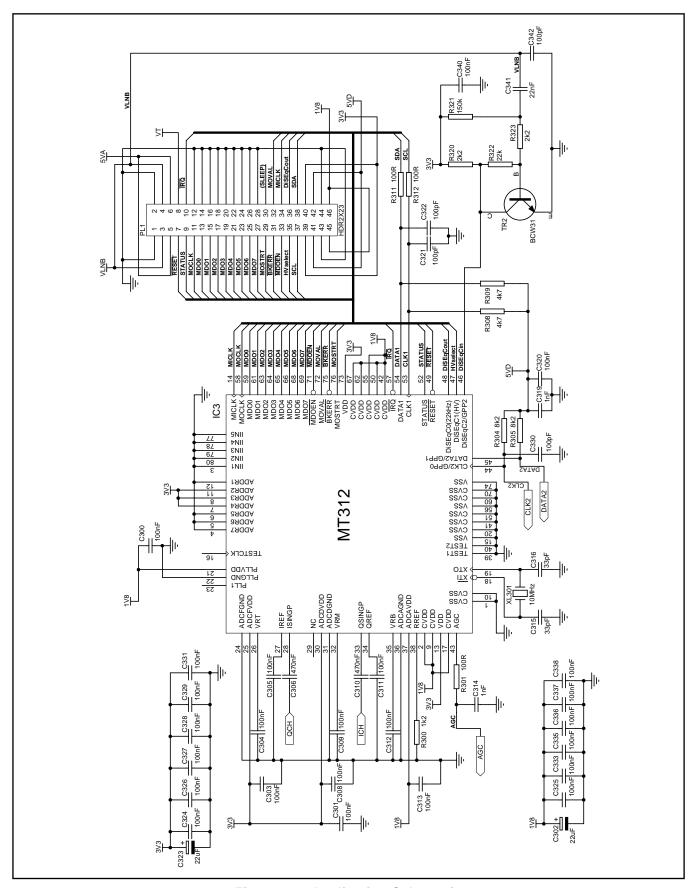

| 13   | Application Diagram                    | 83 |

| 14   | MT312 Register Map                     | 84 |

| 14.1 | Read / Write Register Map              |    |

| 14 2 | Read Only Register Map                 |    |

# MT312 Contents

# List of figures

| Figure 1  | System Block Diagram - SNIM5                                         |    |

|-----------|----------------------------------------------------------------------|----|

| Figure 2  | System Block Diagram - SNIM5                                         | 2  |

| Figure 3  | MT312 Functional Block Diagram                                       | 3  |

| Figure 4  | Viterbi block diagram                                                | 11 |

| Figure 5  | Viterbi error count measurement                                      | 12 |

| Figure 6  | Viterbi error count coarse indication                                | 12 |

| Figure 7  | DVB Conceptual diagram of the concluntional de-interleaver block     | 13 |

| Figure 8  | DSS Conceptual diagram of the convolutional de-interleaver block     | 13 |

| Figure 9  | DVB block structure                                                  | 14 |

| Figure 10 | DSS block structure                                                  | 14 |

| Figure 11 | DVB Energy dispersal conceptual diagram                              | 15 |

| Figure 12 | MT312 Control Structure                                              |    |

| Figure 13 | Alternative System Block Diagram - SNIM6                             | 17 |

| Figure 14 | Initialisation sequence in DVB mode                                  | 20 |

| Figure 15 | Simple channel change sequence                                       | 24 |

| Figure 16 | Channel change sequence with new Symbol rate, DVB mode               | 24 |

| Figure 17 | Channel change sequence with search mode, DVB mode                   | 25 |

| Figure 18 | Results of Symbol rate and code                                      | 25 |

| Figure 19 | A DiSEqC <sup>™</sup> data byte interrupting a continuous 22kHz tone | 29 |

| Figure 20 | One DiSEqC <sup>™</sup> data byte - 0x11 (hex) plus parity bit       | 29 |

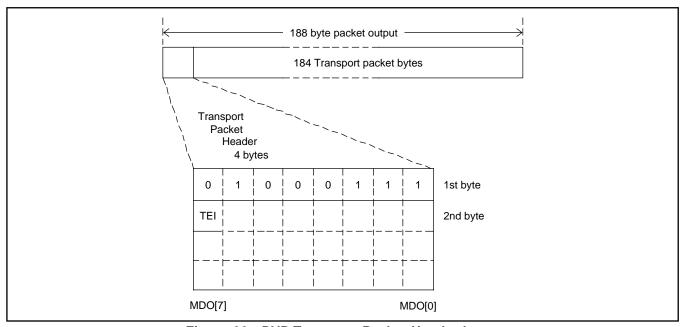

| Figure 21 | DVB Transport Packet Header bytes                                    | 55 |

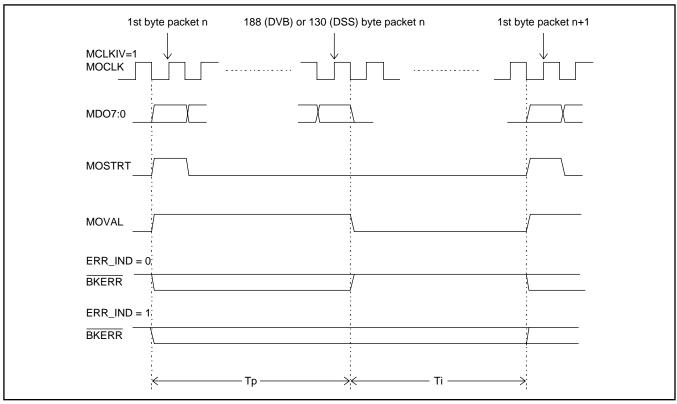

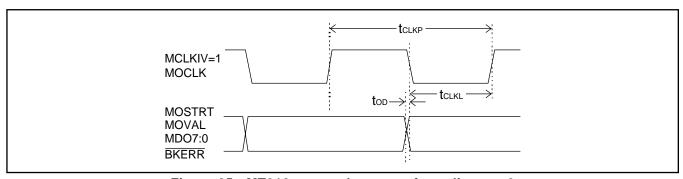

| Figure 22 | MT312 output data wave form diagram                                  | 56 |

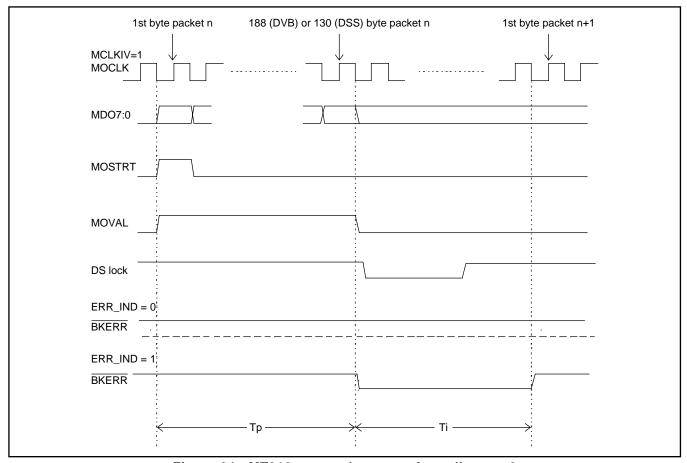

| Figure 23 | MT312 output data wave form diagram 2                                | 57 |

| Figure 24 | MT312 output data wave form diagram 2                                | 58 |

| Figure 25 | One DiSEqC <sup>™</sup> data byte - 0x11 (hex) plus parity bit       | 77 |

| Figure 26 | Crystal oscillator circuit                                           | 79 |

| Figure 27 | Application Schematic                                                | 83 |

Contents

# List of tables

| Table 1  | MT312 pin-out                                  | 2  |

|----------|------------------------------------------------|----|

| Table 2  | MT312 register map overview                    |    |

| Table 3  | Viterbi code rate indication                   | 49 |

| Table 4  | Sigma Delta clock decimation ratio programming | 52 |

| Table 5  | MPEG clock modes 54                            |    |

| Table 6  | MOCLK input minimum and maximum frequencies    | 54 |

| Table 7  | Viterbi code rate search start                 | 69 |

| Table 8  | Primary 2-wire bus timing                      | 77 |

| Table 9  | Recommended operating conditions               | 78 |

| Table 10 | Maximum operating conditions                   | 78 |

| Table 11 | DC electrical characteristics                  | 79 |

| Table 12 | Alphabetical listing of pin-out                | 82 |

PLEASE NOTE: This manual has the following convention:

All numerical values are shown as decimal numbers, unless otherwise defined.

#### 1. Functional Overview

#### 1.1 Introduction

MT312 is a single-chip variable rate digital QPSK/BPSK satellite demodulator and channel decoder. The MT312 accepts base-band in-phase and quadrature analogue signals and delivers an MPEG or DSS packet data stream. Digital filtering in MT312 removes the need for programmable external antialias filtering for all symbol rates from 1 to 45Mbaud. Frequency, timing and carrier phase recovery are all digital and the only feed-back to the analogue frontend is for automatic gain control. The digital phase recovery loop enables very fine bandwidth control that is needed to overcome performance degradation due to phase and thermal noise.

All acquisition algorithms are built into the MT312 controller. The MT312 can be operated in a Command Driven Control (CDC) mode by specifying the Symbol rate and Viterbi code rate. There is also a provision for a search for unknown Symbol rates and Viterbi code rates.

#### 1.2 Analogue-to-Digital Converter

The MT312 contains dual 6-bit A/D converters which each sample a 500mVpp single-ended analogue input at up to 90MHz. The fixed rate sampling clock is provided on-chip using a programmable PLL needing only a low cost 10 to 15MHz crystal. Different crystal frequencies can be combined with different PLL ratios, depending on the maximum symbol rate, allowing a flexible approach to clock generation.

#### 1.3 QPSK Demodulator

The demodulator in the MT312 consists of signal amplitude offset compensation, frequency offset compensation, decimation filtering, carrier recovery, symbol recovery and matched filtering.

The decimation filters give continuous operation from 2Mbits/s to 90Mbits/s allowing one receiver to cover the needs of the consumer market as well as the single carrier per channel (SCPC) market with the same components without compromising performance, that is, the channel reception is within

0.5dB from theory. For a given Symbol rate, control algorithms on the chip detect the number of decimation stages needed and switch them in automatically.

The frequency offset compensation circuitry is capable of tracking out up to  $\pm 15 \text{MHz}$  frequency offset. This allows the system to cope with relatively large frequency uncertainties introduced by the Low Noise Block (LNB). Full control of the LNB is provided by the DiSEqCTM outputs from the MT312. Horizontal / Vertical polarisation and an instruction modulated 22kHz signal are available under register control. All DiSEqCTM v2.2 functions are implemented on the MT312 (ref. 2).

An internal state machine that handles all the demodulator functions controls the signal tracking and acquisition. Various pre-set modes are available as well as blind acquisition where the receiver has no prior knowledge of the received signal. Fast acquisition algorithms have been provided for low Symbol rate applications. Full interactive control of the acquisition function is possible for debug purposes.

In the event of a signal fade or a cycle slip, QPSK demodulator allows sufficient time for the FEC to reacquire lock, for example, via a phase rotation in the Viterbi decoder. This is to minimise the loss of signal due to the signal fade. Only if the FEC fails to reacquire lock for a long period (which is programmable) would QPSK try to re-acquire the signal.

The matched filter is a root-raised-cosine filter with either 0.20 or 0.35 roll-off, compliant with DSS and DVB standards. Although not a part of the DVB standard, MT312 allows a roll-off of 0.20 to be used with other DVB parameters.

An AGC signal is provided to control the signal levels in the tuner section of the receiver and ensure the signal level fed to the MT312 is set at an optimal value under all reception conditions.

The MT312 provides comprehensive information on the input signal and the state of the various parts of the device. This information includes Signal to Noise Ratio (SNR), signal level, AGC lock, timing and carrier lock signals. A maskable interrupt output is available to inform the host controller when events occur.

#### 1.4 Forward Error Correction

The MT312 contains FEC blocks to enable error correction for DVB-S and DSS transmissions. The Viterbi decoder block can decode the convolutional code with rates 1/2, 2/3, 3/4, 5/6, 6/7 or 7/8. The block features automatic synchronisation, automatic IQ phase resolution and automatic code rate detection. The trace back depth of 128 provides better performance at high code rates and the built-in synchronisation algorithm allows the Viterbi decoder to lock onto signals with very poor signal-to-noise ratios. Viterbi bit error rate monitor provides an indication of the error rate at QPSK output.

The 24-bit error count register in the Viterbi decoder allows the bit error rate at the output of the QPSK demodulator to be monitored. The 24-bit bit error count register in the Reed-Solomon decoder allows the Viterbi output bit error rate to be monitored. The 16-bit uncorrectable packet counter vields information about the output packet error rate. These three monitors and the QPSK SNR register allows the performance of the device and its individual components, such as the QPSK demodulator and the Viterbi decoder, to be monitored extensively by the external microprocessor.

The frame/byte align block features a sophisticated synchronisation algorithm to ensure reliable recovery of DVB and DSS framed data streams under worst case signal conditions. The de-interleaver uses on-chip RAM and is compatible with the DVB and DSS algorithms.

The Reed-Solomon decoder is a truncated version of the (255, 239) code. The code block size is 204 for DVB and 146 for DSS. The decoder provides a count of the number of uncorrectable blocks as well as the number of bit errors corrected. The latter gives an indication of the bit error rate at the output of the Viterbi decoder.

In DVB mode, spectrum de-scrambling is performed compatible with the DVB specification. The final output is a parallel or serial transport data stream; packet sync; data clock; and a block error signal. The data clock may be inverted under software control.

#### 1.4.1.1 Viterbi Error Count Measurement

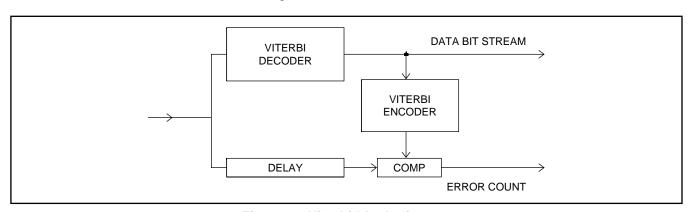

A method of estimating the bit error rate at the output of the QPSK block has been provided in the Viterbi decoder. The incoming data bit stream is delayed and compared with the re-encoded and punctured version of the decoded bit stream to obtain a count of errors see Figure 4 - Viterbi block diagram.

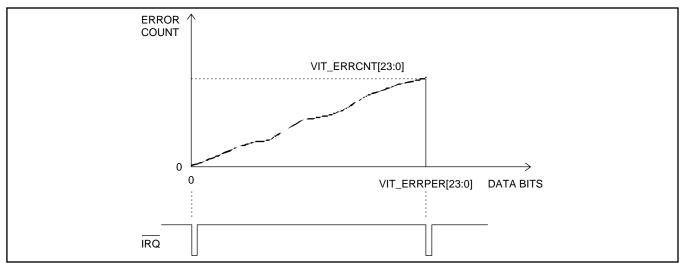

The measurement system has a programmable register to determine the number of data bits (the error count period) over which the count is being recorded. A read register indicates the error count result and an interrupt can be generated to inform the host microprocessor that a new count is available.

The VIT ERRPER H-M-L group of three registers is programmed with required number of data bits (the error count period) (VIT ERRPER[23:0]). The actual value is four times VIT ERRPER[23:0]. The count of errors found during this period is loaded by the MT312 into the VIT ERRCNT H-M-L trio of registers when the bit count VIT ERRPER[23:0] is reached. At the same time an interrupt is generated on the  $\overline{\mbox{IRQ}}$  line. Setting the IE FEC[2] bit in the IE FEC register enables the interrupt, see page 32. Reading the register does not clear VIT ERRCNT [23:0], it is only loaded with the error count.

Figure 4 - Viterbi block diagram

Figure 5 - Viterbi error count measurement

Figure 5 shows the bit errors rising until the maximum programmed value of VIT ERRPER[23:0] is reached, when an interrupt is generated on the  $\overline{IRQ}$  line to advise the host microprocessor that a new value of bit error count has been loaded into the VIT ERRCNT [23:0] register. The  $\overline{IRQ}$  line will go high when the IE FEC register is read by the host microprocessor. The error count may be expressed as a ratio:

VIT\_ERRCNT[23:0] VIT\_ERRPER[23:0]\*4

#### 1.4.1.2 Viterbi Error Count Coarse Indication

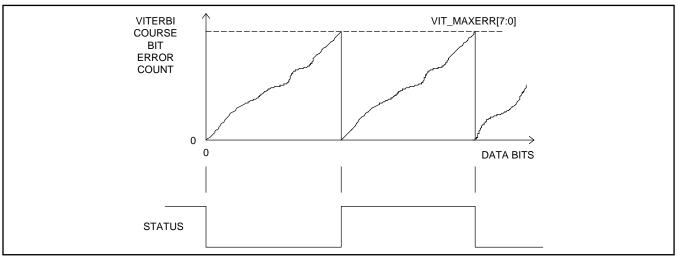

To assist in the process of aligning the receiver dish aerial, a coarse indication of the number of bit errors being received can be provided by monitoring the STATUS line with the following set up conditions.

The frequency of the output waveform will be a function of the bit error count (triggering the

maximum value programmed into the VIT MAXERR[7:0] register and the dish alignment on the satellite. This VIT MAXERR mode is enabled by setting the FEC STAT EN register bit B0. Figure 5 above shows the bit errors rising to the maximum value programmed and triggering a change of state on the STATUS line.

#### 1.4.2 The Frame Alignment Block

The frame alignment algorithm detects a sequence of correctly spaced synchronising bytes in the Viterbi decoded bit-stream and arranges the input into blocks of data bytes. Each block consists of 204 bytes for DVB and 147 bytes for DSS. In the DSS mode, the synchronising byte is removed from the data stream, so only 146 bytes of a block are passed to the next stage. The frame alignment block also removes the 180° phase ambiguity not removed by Viterbi decoder.

Figure 6 - Viterbi error count coarse indication

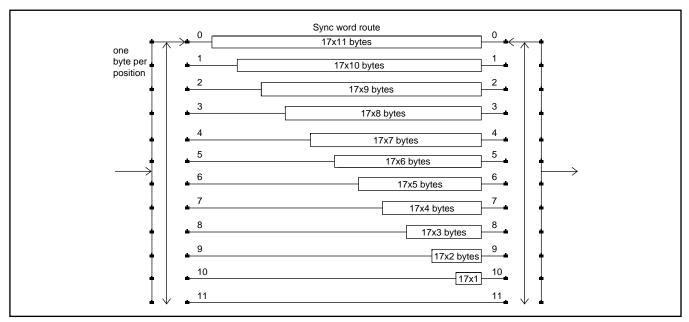

#### 1.4.3 The De-interleaver Block

#### 1.4.3.1 DVB

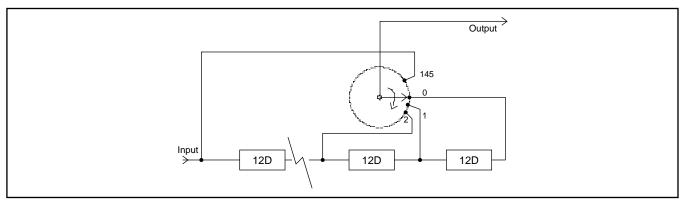

Before transmission, the data bytes are interleaved with each other in a cyclic pattern of twelve. This ensures the bytes are spaced out to avoid the possibility of a noise spike corrupting a group of consecutive message bytes. The diagram below shows conceptually how the convolutional deinterleaving system works. The synchronisation byte is always loaded into the First-In-First-Out (FIFO) memory in branch 0. The switch is operated at regular byte intervals to insert successively received bytes into successive branches. After 12 bytes have been received, byte 13 is written next to the

synchronisation byte in branch 0, etc. In the MT312, this de-interleaving function is realised using on-chip Random Access Memory (RAM).

#### 1.4.3.2 DSS

Before transmission, the data bytes are interleaved with each other in a cyclic pattern of thirteen. This ensures the bytes are spaced out to avoid the possibility of a noise spike corrupting a group of consecutive message bytes. The diagram below shows conceptually how the convolutional deinterleaving system works. On the MT312, this function is realised in the same Random Access Memory (RAM) as used for DVB, but utilising different addressing algorithm.

Figure 7 - DVB Conceptual diagram of the concluntional de-interleaver block

Figure 8 - DSS Conceptual diagram of the convolutional de-interleaver block

#### 1.4.4 The Reed Solomon Decoder Block

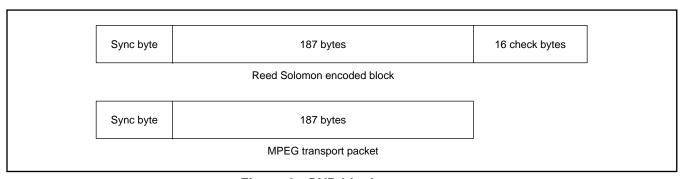

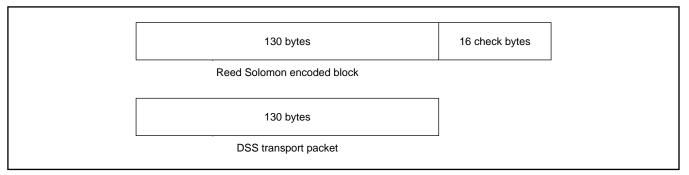

DVB and DSS data are encoded using shortened versions of the Reed-Solomon code of block length 255, containing 239 message bytes and 16 check bytes, that is (255,239) with T=8. Both encoders use the same generator polynomial. The code block size for DVB is 204 and that for DSS is 146. Hence DVB code is (204, 188) and DSS code is (146, 130), with both having T=8. The block structure of the DVB and DSS Reed-Solomon codes are as shown in Figure 9 and Figure 10 below.

The Reed-Solomon decoder can correct up to eight byte errors per packet. If there are more than 8 bytes containing errors, the packet is flagged as uncorrectable using the pin BKERR. In the case of DVB the transport error indicator (TEI) bit of the MPEG packet is set to 1, if setting of TEI is enabled.

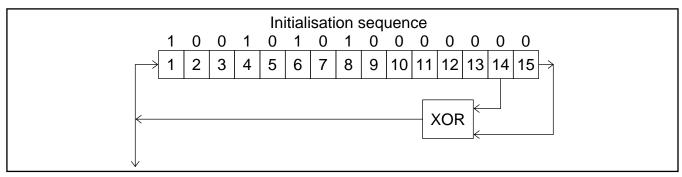

# 1.4.5 The Energy Dispersal (De-Scrambler) Block, DVB only

Before Reed Solomon encoding in the DVB transmission system, the MPEG2 data stream is

randomised using the configuration shown in Figure 11 below. This is a Pseudo Random Binary Sequence (PRBS) generator, with the polynomial:

$$1 + X^{14} + X^{15}$$

The PRBS registers are loaded with the initialisation sequence as shown, at the start of the first transport packet in a group of eight packets. This point is indicated by the inverted sync byte B8hex. The normal DVB sync byte is 47hex. The data starting with the first byte after the sync byte is randomised by exclusive-ORing data bits with the PRBS. (The sync bytes themselves are not randomised).

In the decoder, the process of de-randomising or descrambling the data is exactly the same as described above. The de-scrambler also inverts the sync byte B8hex so that all MPEG output packets have the same synch byte 47hex.

Figure 9 - DVB block structure

Figure 10 - DSS block structure

Figure 11 - DVB Energy dispersal conceptual diagram

#### 1.4.6 Output Stage

Transport stream can be output in a byte-parallel or bit-serial mode. The output interface consists of an 8-bit output, output clock, a packet validation level, a packet start pulse and a block error indicator.

The output clock rate depends on the Symbol rate, QPSK/BPSK choice, convolutional (Viterbi) coding rate, DVB/DSS choice and byte-parallel or bit-serial output mode. This rate is computed by MT312 to be very close to the minimum required to output packet data without packet overlap. Furthermore, the packets at the output of MT312 are as evenly spaced as possible to minimise packet position movement in the transport layer. The maximum movement in the packet synchronisation byte position is limited to ± one output clock period.

An external MPEG clock can be input to synchronise the MPEG data output to MPEG decoders.

#### 1.5 Control

Automatic Symbol Rate Search, Code Rate Search, Signal Acquisition and Signal Tracking algorithms are built into the MT312 using a sophisticated on-chip controller. The software interaction with the device is via a simple Command Driven Control (CDC) interface. This CDC maps high level inputs such as symbol rates in MBaud and frequencies in MHz, to low level on-chip register settings. The on-chip control state machine and the CDC significantly reduces the software overhead as well as the channel search times. There is also an option for the host processor to by-pass both the CDC as well as

the on-chip controller and take direct control of the QPSK demodulator.

Once the MT312 has locked up, any frequency offset can be read from the LNB FREQ error registers 7 and 8. The frequency synthesiser under the software control can be re-tuned in frequency to optimise the received signal within the SAW bandwidth. Note that MT312 compensates for any frequency offsets before QPSK demodulation. Hence a frequency offset will not necessarily lead to a performance loss. Performance loss will occur only if a significant part of the signal is cut off by the SAW or base-band filter. due to this frequency offset. This will happen only if the symbol rate is close to maximum supported by that filter. In such an event it is recommended that front-end be re-tuned to neutralise this error before the SAW filter. It is then necessary for the MT312 to re-acquire the signal.

The MT312 can generate control signals to enable full control of the dish and LNB. The chip implements the signals needed for the full DiSEqC $^{TM}$  v2.2 specification. This includes high/low band selection, polarisation and dish position.

In this mode, the Symbol rate in MBaud and Viterbi code rate are the only values needed to start the MT312 searching for the signal. The CDC module maps the high level parameters into the various low level register settings needed to acquire and track the signal. The low level registers may be read and directly modified to suit very specific requirements. However, this is not recommended.

Figure 12 - MT312 Control Structure

#### 1.5.2 Symbol Rate and Code Rate Search Mode

Where the Symbol rate and/or the Viterbi code rate are unknown, the MT312 can be programmed to search for QPSK/BPSK signals. The user should define the range(s) over which the search is required. The MT312 will then locate and track any signal detected. Failure to find a QPSK signal in the specified frequency and specified symbol rate ranges will be indicated by interrupts (see 6.2 QPSK Demodulator Read Registers). MT312 will carry on searching these ranges after issuing these interrupts. When the MT312 has locked onto a signal, the Symbol rate in MBaud may be read from the MONITOR registers. The Viterbi code rate may be read from the FEC STATUS register. This search facility is primarily for the initial installation of a set top box.

#### 1.6 Direct Conversion Application

Figure 1 shows a direct conversion system that mixes the L-band input to the tuner directly down to I and Q baseband channels at zero intermediate frequency.

The RF AGC amp and tracking filter provide the required tuner noise figure and limit the total power reaching the SL1925. These elements also give isolation between the SL1925 local oscillator and the L-band tuner input. This is an important factor since both signals are at the same frequency.

The baseband filter is an anti-alias filter. This replaces the filtering normally carried out with a SAW filter in conventional single conversion tuners.

It is important to note that all the channel filtering needed to isolate low Baud rate signals is contained within the MT312. The low pass filter before MT312 is designed not to filter channels, but to minimise any aliasing due to sampling. To illustrate this, let the sampling frequency be 90 MHz and the maximum symbol rate be 45 MBaud. The bandwidth of the 45 MBaud QPSK signal, with 0.35 roll-off, is about 60 MHz. If the channel has been mapped precisely to

base-band, the pass-band of the low pass filter should extend up to 30 MHz. However, it is preferable to make this bandwidth larger by about 5 MHz, partly to reduce the in-band phase distortion introduced by the filter and partly to reduce the loss of signal due to LNB offset. The filter must attenuate signals beyond 60 MHz by about 30 dB, as these signal will alias to the useful frequency range with 90 MHz sampling.

Although the system is designed for 45 MBaud, if the actual symbol rate is much lower, say 1 MBaud, then MT312 will automatically introduce all the digital filtering needed to isolate the 1 MBaud signal.

Figure 13 - Alternative System Block Diagram - SNIM6 shows an alternative application when a reduced Symbol rate is acceptable. The SL1935 combines the functions of the RF pre-amp, direct conversion zero IF tuner and synthesiser.

Figure 13 - Alternative System Block Diagram - SNIM6

### 1.7 DiSEqC™ Transmit and Receive Messages

The MT312 has the capability to send and receive DiSEqC™ messages. Eight registers are provided to store a message for transmission and a further eight registers are provided to store a received message. The received bytes have a parity bit and a parity error bit in addition to the eight data bits. These additional bits are read out in following the data bits, so two byte reads are required for each data byte.

### 1.7.1 DiSEqC™ Transmitting Messages

The sequence of events to send a message are as follows:

- Load the required message bytes into the DiSEqC™ Instruction register 36, see page 34. Sequential writes to the same register is achieved by setting the Inhibit Auto Incrementing (IAI) bit 7 in RADD, the register address byte.

- Load the number of bytes (less one) in the DiSEqC™ instruction in the register DISEQC MODE[5:3], see page 32.

- Set DISEQC MODE[2:0] = 4 to command the MT312 to encode the data and transmit the message.

- 4. Reset DISEQC MODE[2:0] to either 0 or 1 depending on previous setting of 22kHz off or on.

The data loaded into DISEQC INSTR register is retained, so that if the same message is to be repeated, the data loading stage 1 above can be omitted.

#### 1.7.2 DiSEqC™ Receiving Messages

The MT312 will automatically listen for DiSEqC™ messages 5ms after a message has been

transmitted. If a return message is expected, the DISEQC MODE[2:0] must be set to zero in order to leave the LNB control signal free for another DiSEqC™ transmitter to respond.

The sequence of events to receive a message are as follows:

- 1. Enable DiSEqC2 GPP2 pin 46 as an input by setting GPP CTRL register 20 B5 to zero.

- 2. Enable interrupts if the  $\overline{\text{IRQ}}$  pin is being used to interrupt the host processor in DISEQC2 CTRL1 register 121.

- 3. Monitor DISEQC2 INT register.

- 4. If B3 = 1 and B1 = 0, there has been no message received.

- If a message has been received, B0 will be set, If B1 is also set the message is complete.

DISEQC2 INT register B7-4 indicate how many bytes have been received.

- 6. Read the received message from DISEQC2 FIFO register 120 by setting the Inhibit Auto Incrementing (IAI) bit 7 in RADD, the register address byte and sequentially reading DISEQC2 FIFO for the indicated number of bytes. Each data byte read requires two 2-wire bus reads. The second or the pair of bytes contains the parity bit and a parity bit error indicator.

The user may choose to wait for the end of message indication, before reading the message, if it is known that the message is not greater than eight bytes. However, if the length of message is not known, the message should be read out of the FIFO by the host as it is being received. Care must be taken to avoid a FIFO buffer overflow. DISEQC2 INT register B7-4 will indicate how many bytes remain in the FIFO.

#### 2 MT312 Software Control

This section describes the sequences of register operations needed to acquire DVB and DSS channels with known or unknown parameters.

Communication with the MT312 is via a standard 2-wire bus and the first byte following the chip address, in write mode, is the register address (RADD).

The register map is organised to group important Read registers at the lowest addresses, then the main control Write registers in the next block of addresses.

The first register to be written must be the Configuration register, which has been placed at the

highest register address, because it is only written once during the initialisation sequence.

The CONFIG register can only be reset by the hardware reset. The MT312 is held in a power saving mode following the hardware reset.

After a hardware reset, the MT312 must be taken out of the power save mode by writing a one to the MSB of the CONFIG register (see 1.1 Introduction). When MT312 is not being used it can be put back into the power save mode by writing a zero to the MSB of CONFIG.

#### 2.1 MT312 Register Map Overview

| Address                      | Description                | Section           | Туре         |

|------------------------------|----------------------------|-------------------|--------------|

| 00 - 06                      | Interrupt and Status       | 5.1to 5.4-        | read         |

| 07 - 19, 108 - 117, 123, 124 | Primary signal monitors    | 5.5 to 5.17       | read         |

| 20 - 39, 41, 96, 103         | Primary control parameters | 4 to 4.20         | write / read |

| 40, 42 - 49, 50 - 106, 125   | Secondary parameters       | 11.1.1 to 11.1.52 | write / read |

| 107, 118 - 122               | Secondary monitors         | 11.2.1 to 4.22    | read         |

| 126                          | Chip identification        | 5.18              | read         |

| 127                          | Chip configuration         | 4.22              | write / read |

Table 2 - MT312 register map overview

All write / read registers take on default values on full software reset, except for the configuration register (127), that is only reset to the default value by a hardware reset.

#### 3 MT312 Initialisation

#### 3.1 The Configuration Register (127)

CONFIG[B7-0]: This register is for setting up the MT312. It must be loaded first before any other register. It can only be reset to the default value by the RESET pin being pulled low. After loading this register, wait 150µs for the Clock PLL to settle before writing to the RESET register. During this wait period, the tuner may be programmed via the General Purpose Port. Note that the GPP register occupies the address space before the RESET register.

CONFIG[B7]: 312 ENHigh = MT312 enable.

Low = MT312 disable to save power.

CONFIG[B6-5]: DSS BDSS A

0 0: DVB mode

0 1: DSS mode 1 - code rate 2/3

1 0: DSS mode 2 - code rate 6/7

1 1: DSS Code Rate search

If both DSS A and DSS B are set high, the MT312 will search for the code rate in DSS mode. If either of the DSS A or DSS B are set high, the Symbol rate is automatically set to 20Mbaud and SYM RATE registers (23 & 24) are ignored. The matched filter root-raised-cosine roll-off is set to 0.20 and bit B0 of QPSK CTRL (26) is ignored. Also, any code rate programmed into VIT MODE register (25) and VIT SETUP register (86) will be ignored.

Also in DSS mode TS SW RATE register (50) must be set to 20, see 10.2.10 Timing Synchronisation Sweep Rate. Register 50 (R/W).

CONFIG[B4]: BPSK High = BPSK

Low = QPSK

CONFIG[B3-2]: PLL FACTOR[1:0]:

B3-2 Multiplication factor

00: 3

01: 4 10: 6

11: 9

CONFIG[B1]: CRYS15 High = 15MHz crystal.

Low = 10MHz crystal.

CONFIG[B0]: ADCEXT High = ADC external.

Low = ADC internal.

e.g. For a crystal frequency of 10MHz, a system clock frequency of 60MHz, the PLL ratio will be 6, requiring the PLL FACTOR[1:0] = 2.

For QPSK reception and ADC internal, the MT312 is enabled by writing 88 hex to register 127.

MT312 computes the System clock frequency using bits B3-B1 above. This frequency is used internally for computing parameters needed for acquiring the QPSK signal.

It is possible to use a crystal frequency other than 10 or 15 MHz. As an example, let the crystal frequency be 10.25MHz and the PLL multiplication factor be 6. Then B3 is set to 1 and B2 to 0. Bit B1 may be given an arbitrary value (0 or 1). The external software must compute the system clock frequency and load this value (multiplied by 2) to the SYS CLK register (Address 34). In the above example, the system clock frequency is 61.5 MHz and hence the value 123 has to be loaded into SYS CLK register.

The QPSK demodulator checks the SYS CLK register and if this is non-zero, it uses the contents of this as the system clock frequency, for internal calculations mentioned above. If this register is zero (which is the default setting), QPSK demodulator works out the system clock frequency from bits B3-B1 of the CONFIG register assuming that the crystal frequency is either 10 or 15 MHz, as defined by bit B1.

#### 3.2 Power Supplies

To avoid the possibility of destructive latch-up, the CVDD supply must never, at any time during power-up, exceed 0.5V above the VDD supply and must also remain within the absolute maximum ratings, see section 12.2 on page 78.

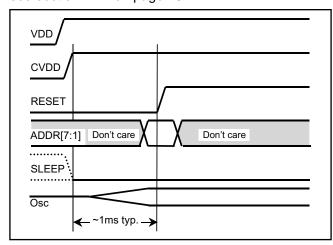

Figure 14 - MT351 power-up sequence

In general therefore, the VDD supply should be established ahead of, or simultaneously with the  $C_{VDD}$  supply.

#### 3.3 Initialisation Sequence

MT312 will be in the power save mode after a hardware reset. The first command to be written must be to the CONFIGURATION register at address 127. After loading this register, wait 150µs before writing to the RESET register. During this wait, the tuner can programmed to the required channel frequency via the General Purpose Port (register 20). If the AGC slope control bit of AGC CTRL(39) or the AGC REF(41) are to be changed, it is best to write to these registers after writing to the RESET register. This will allow the front-end AGC loop to settle while the other registers are being written.

Next write 128 to the RESET register (21) to reset the MT312 state machine and all parameter registers to the default settings. It is then necessary to change the default setting of register 49 to 50 (decimal).

If necessary, other default parameters may need to be changed. These may include:

- Slope of AGC control signal see register (39)

ACG CTRL[B0] AGC SL bit

- AGC Reference value see register (41) AGC REF

- Relative phase of IQ spectrum see register

(25) VIT MODE[B6]

- LNB frequency search range, default is ±6MHz

see register (37) FR LIM

- For low Baud rates only, set fast frequency acquisition mode - see register (26) set QPSK CTRL[B2] = 1

To invert MOCLK or BKERR output signals - see register (96) OP CTRL

After this, the LNB controls are defined, in register (22) DISEQC MODE.

The signal parameters should then be written to the MT312. The symbol rate (registers 23 & 25 SYM RATE) may be specified within ±2% of the required value, absolute precision is not required to achieve successful lock and tracking. If the symbol rate is unknown, a search mode is available.

Selecting the correct bit of register (25) VIT MODE, if known, programs the convolutional code rate. If the code rate is unknown, some or all of the bits of VIT MODE may be set to force the MT312 to search for the code rate.

Finally, the MT312 is given a GO command, register (27) GO =1, to release the state machine and to start the signal acquisition sequence. This is summarised as an example in the following flow diagram.

Figure 15 - Initialisation sequence in DVB mode

#### 3.4 Spectral Inversion

Spectral inversion of the QPSK signal can be caused by the transmitter or the receiver front-end. In the latter case, this could happen due to the way I-Q conversion is carried out or because the I and Q wires are swapped between the I-Q converter and the MT312. If spectral inversion is caused by the receiver front-end, then this must be removed by swapping I and Q (within MT312) before QPSK demodulation, by setting Q IQ SP bit B6 of QPSK CTRL register (26) to 1.

If no spectral inversion is caused by the receiver front-end design, then bit B6 of QPSK CTRL must always be held at zero. If the transmitted signal is known to be spectrally inverted, then V IQ SP bit B6 of the VIT MODE register (25) must be set to 1. Then I and Q are swapped after QPSK demodulation. If the spectral inversion status of the transmitted signal is not known, then after QPSK has locked (i.e. QPSK CT LOCK = 1), the software must try to achieve FEC lock with the bit B6 of VIT MODE register first at zero and then at one.

#### 3.5 MT312 Initialisation Read/Write Registers

#### 3.5.1 Reset. Register 21 (R/W)

FR 312

B7:

| NAME  | ADR | В7        | В6        | B5       | B4       | В3        | B2        | B1       | В0       |     | Def<br>hex |

|-------|-----|-----------|-----------|----------|----------|-----------|-----------|----------|----------|-----|------------|

| RESET | 21  | FR<br>312 | PR<br>312 | FR<br>QP | PR<br>QP | FR<br>VIT | PR<br>VIT | PR<br>BA | PR<br>DS | R/W | 00         |

B6: PR 312 High = Partial reset of MT312 device.

B5: FR QP High = Full reset of QPSK block.

B4: PR QP High = Partial reset of QPSK block.

High = Full reset of MT312 device.

B3: FR VIT High = Full reset of Viterbi block.

B2: PR VIT High = Partial reset of Viterbi block.

B1: PR BA High = Partial reset of Byte Align block.

B0: PR DS High = Partial reset of De-scrambler block.

Writing a one to these register locations generates a reset pulse three crystal clock periods wide.

The register automatically resets to zero after use.

A full reset does reset the registers to their default values.

A partial reset does not reset the registers to their default values.

#### 3.5.2 MT312 Configuration. Register 127 (R/W)

| NAME   | ADR | В7     | В6    | B5    | B4   | В3            | B2 | B1         | В0         |     | Def<br>hex |

|--------|-----|--------|-------|-------|------|---------------|----|------------|------------|-----|------------|

| CONFIG | 127 | 312 EN | DSS B | DSS A | BPSK | PLL FA<br>[1: |    | CRYS<br>15 | ADC<br>EXT | R/W | 80         |

CONFIG[7:0]: This register is for setting up the MT312. It must be loaded first before any other register. It can only be reset by the RESET pin being pulled low.

B7: 312 EN High = MT312 enable.

Low = MT312 disable to save power.

B6-5: DSS B DSS A

0 0: DVB mode

1: DSS mode 1 - code rate 2/31: DSS mode 2 - code rate 6/7

1 1: DSS search mode

If both DSS A and DSS B are set high, the MT312 will search for the code rate in DSS mode. Then the Symbol rate is automatically set to 20Mbaud and SYM RATE registers (23 & 24) are ignored. Also, any code rate programmed into VIT MODE register (25) and VIT SETUP register (86) will be ignored.

Also in DSS mode TS SW RATE register (50) must be set to 20, see page 70.

B4: BPSK High = BPSK

Low = QPSK

B3-2: PLL FACTOR[1:0]:

B3-2 Multiplication factor

00:

3

01:

4

10:

6

11:

9

B1: CRYS15 High = 15MHz crystal.

Low = 10MHz crystal.

B0: ADCEXT High = ADC external.

Low = ADC internal.

e.g. For a crystal frequency of 10MHz, a system clock frequency of 60MHz, the PLL ratio will be 6, requiring the PLL FACTOR[1:0] = 2.

When MT312 is not being used it can be put into power save mode by setting bit B7 to 0.

## 3.5.3 System Clock Frequency. Register 34 (R/W)

| NAME    | ADR | В7 | В6                                              | B5 | B4 | В3 | B2 | B1 | В0 |     | Def<br>hex |

|---------|-----|----|-------------------------------------------------|----|----|----|----|----|----|-----|------------|

| SYS CLK | 34  | SY | SYS CLK[7:0] - System clock frequency x2 in MHz |    |    |    |    |    |    | R/W | 00         |

SYS CLK[7:0] = System clock frequency \* 2 in MHz.

The SYS CLK register must be programmed to indicate the system clock frequency to the calculation unit. The maximum system clock frequency allowed is 90MHz.

e.g. for a crystal frequency = 10MHz, if the PLL multiplication ratio is 9,

The system clock frequency = 90MHz.

Then SYS CLK[7:0] = 180.

The system clock frequency is NOT affected by the setting of SYS CLK[7:0] register.

## 3.6 MT312 Initialisation Read Register

## 3.6.1 Identification. Register 126 (R)

| NAME | ADR | В7 | В6                           | B5 | B4 | В3 | B2 | B1 | В0 |   | Def<br>hex |

|------|-----|----|------------------------------|----|----|----|----|----|----|---|------------|

| ID   | 126 |    | ID[7:0] Chip identification. |    |    |    |    |    |    | R | 03         |

ID[7:0]:

This register provides an identification number related to the MT312 version.

#### **4 Tuner Control**

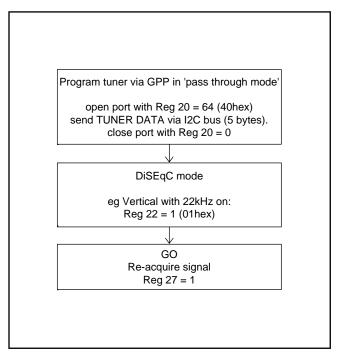

#### 4.1 Simple Channel Change Sequence

If the MT312 is running, to change channel keeping the same signal conditions, it is only necessary to change the tuner data and possibly the DiSEqC™ data. NO reset is necessary.

# 4.2 Channel Change Sequence with a new Symbol Rate

If the MT312 is running, to change channel and Symbol rate but not Viterbi coding rate, change the tuner data and possibly the DiSEqC™ data and Symbol rate. NO reset is necessary.

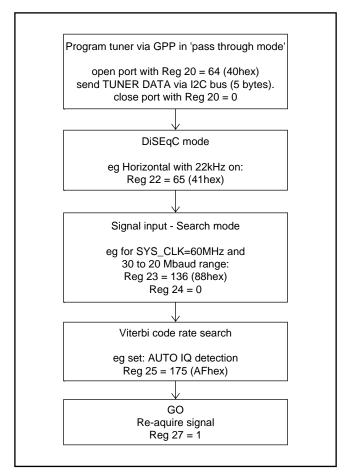

# 4.3 Channel Change Sequence with Search Mode

If the signal parameters are unknown, it is possible to instruct the MT312 to find a digital signal and report the parameters found. Registers 24 and 25 are programmed with the expected range(s) and the search mode bit SYM RATE[B15] is set high. A code rate search is forced by programming more than one bit in VIT MODE (26) register. The IQ spectrum phase can be automatically determined by setting bit 7 in the VIT MODE (26) register.

Note: code rate 6/7 is not searched for DVB mode.

If a signal with the specified symbol rate range (or ranges) is not found in the frequency range searched, a QPSK Baud End interrupt (Bit B6, QPSK INT L (2)) is issued.

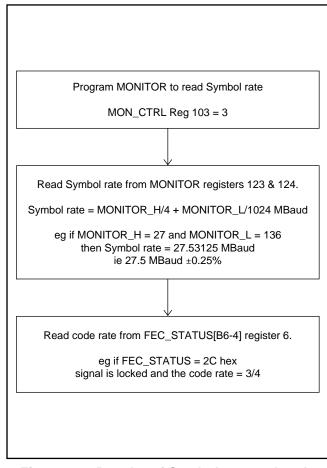

When the MT312 QPSK section has locked to the signal, this is indicated in register (6) by QPSK STAT H[B0] = 1. The symbol rate found can be read from registers (123 - 124) MONITOR, provided the register (103) MON CTRL = 3. The tolerance of the result is  $\pm 0.25\%$ . The 14 MSBs of this result (discarding two LSBs) may be written as the 14 LSBs of the 16-bit register pair (23 and 24) SYM RATE in the non-search mode for re-acquisition of the same channel.

The FEC is locked to the signal, when the Byte Align lock in FEC STATUS[B2] = 1. Then the code rate found can be read from FEC STATUS[B6-4], see register 6 49 for details.

Figure 16 - Simple channel change sequence

Figure 17 - Channel change sequence with new Symbol rate, DVB mode

Figure 18 - Channel change sequence with search mode, DVB mode

Figure 19 - Results of Symbol rate and code rate search, DVB or DSS mode

#### 4.4 Tuner Control Read/Write Registers

#### 4.4.1 General Purpose Port Control. Register 20 (R/W)

| NAME     | ADR | В7       | В6        | B5 | B4       | В3  | B2 | B1      | В0   |     | Def<br>hex |

|----------|-----|----------|-----------|----|----------|-----|----|---------|------|-----|------------|

| GPP CTRL | 20  | Reserved | 2W<br>PAS | GF | PP DIR[2 | :0] | GP | P PIN[2 | 2:0] | R/W | 20         |

B7: Reserved. Must be set low.

B6: 2W PAS: High = 2-wire bus Pass-through.

Low = GPP pin I/O direction set by GPP DIR[2:0].

B5-3: GPP DIR[2:0] Any bit set high configures the corresponding GPP[2:0] pin as output

Any bit set low configures the corresponding GPP[2:0] pin as input

Mixed use of pins as inputs and outputs is allowed.

If B6 = 1, pass-through mode, then:

GPP DIR[1:0] are ignored,

B2: = Input or output set by GPP DIR[2] - relating to pin 46.

# MT312 Tuner Control

Pin 45 = DATA2, this is a transparent, bi-directional connection to the primary DATA1.

Pin 44 = CLK2, this is a transparent, bi-directional connection to the primary CLK1.

If B6 = 0 then: GPP DIR[2:0] defines the input/output conditions of the GPP pins and:

If a pin[n] is defined as output then:

GPP PIN[n] high forces GPP[n] pin high

GPP PIN[n] low forces GPP[n] pin low

If a pin[n] is defined as input then:

GPP[n] pin high sets bit GPP PIN[n] high

GPP[n] pin low sets bit GPP PIN[n] low

Allocation of GPP PIN[2:0] is:

GPP PIN[2] = DiSEqC™ v2.2 input, 3 wire bus Enable or can be used for any other application

GPP PIN[1] = DATA2 or 3 wire bus Data

GPP PIN[0] = CLK2 or 3 wire bus Clock

The register default state of 20 hex allows the GPP[2] pin to be used for the 3 wire bus Enable line and to be kept low at all times, except when programming the Synthesiser.

When GPP[2] pin is used for DiSEqC™ v2.2 input, the GPP CTRL register will need to be set to zero after every full reset to make GPP[2] an input.

### 4.4.2 FR LIM: Frequency Limit. Register 37 (R/W)

| NAME   | ADR | В7       | В6 | B5   | B4        | В3        | B2       | B1 | В0 |     | Def<br>hex |

|--------|-----|----------|----|------|-----------|-----------|----------|----|----|-----|------------|

| FR LIM | 37  | Reserved |    | FR L | IM[6:0] - | Freq. Lir | nit in M | Hz |    | R/W | 30         |

B7: Reserved. Must be set low.

FR LIM[6:0] Frequency search range MHz x 8. This unsigned 7 bit number represents a search range of  $\pm$ 0 to  $\pm$ 1. Default value 30 (hex) =  $\pm$ 1. 6MHz.

#### 4.4.3 FR OFF: Frequency Offset. Register 38 (R/W)

| NAME   | ADR | В7 | В6 | B5      | B4          | В3        | B2  | B1 | В0 |     | Def<br>hex |

|--------|-----|----|----|---------|-------------|-----------|-----|----|----|-----|------------|

| FR OFF | 38  |    | FR | OFF[7:0 | ] - Freq. ( | Offset in | MHz |    |    | R/W | 00         |

FR OFF[7:0] Frequency offset correction value in MHz x 32. This 2's complement 8 bit number represents an offset from -4MHz to +3.96875MHz. Default value 0.

The frequency search is carried out in the range [(-FR LIM + FR OFF), (FR LIM + FR OFF). Frequency offset register can be useful in reducing frequency search during channel hopping, especially with low symbol rates. If the location of the wanted channel with respect to the current channel is known and if the synthesiser step size is too large to set the precise frequency of that channel, then the FR OFF register can be used to take up any residual frequency offset.

#### 4.5 Tuner Control Read Registers

#### 4.5.1 Measured LNB Frequency Error. Registers 7 - 8 (R)

| NAME       | ADR | В7     | В6                                                    | B5       | B4       | В3       | B2        | B1       | В0  |    | Def<br>hex |

|------------|-----|--------|-------------------------------------------------------|----------|----------|----------|-----------|----------|-----|----|------------|

| LNB FREQ H | 07  | LNB FF | REQ15:8                                               | ] Measur | ed LNB f | requency | y error ( | high byt | te) | R  | 00         |

| LNB FREQ L | 08  | LNB F  | LNB FREQ[7:0] Measured LNB frequency error (low byte) |          |          |          |           |          | R   | 00 |            |

LNB FREQ[15:0]: Once the chip is in lock these two registers provide a measurement of the frequency of the signal at the input to MT312. Ideally, this frequency is zero. Due to LNB frequency uncertainty this frequency may take a positive or negative value. Then the analogue front-end may be re-tuned to bring this offset close to zero. Note that MT312 indicates the frequency location of the QPSK spectrum with respect to zero frequency. The direction in which the synthesiser frequency has to be stepped depends on the design of the analogue front-end. Also note that in many instances it will not be necessary to re-tune even when there is a relatively large frequency offset. This is because MT312 compensates for this frequency offset before it demodulates the signal. Re-tune only if a substantial part of the QPSK spectrum is affected by the SAW or base-band filter which precedes MT312. This will be the case only for symbol rates which are close to the maximum symbol rate supported by the above mentioned filters.

When MT312 locks part of the frequency offset is taken up by the frequency compensation mixer and part by the carrier synchroniser. LNB FREQ gives only the value in the frequency compensation mixer. Over a short period of about 1 s after lock, the carrier synchroniser will transfer all the frequency compensation to the mixer. Hence the LNB FREQ reading will have an error less than ±5% of the symbol rate, during this short period after lock. If an accurate frequency reading is needed immediately after lock, the calculation given in section on FREQ ERR2 has to be performed by external software.

LNB FREQ[15:0] Frequency offset MHz x 512. This is a 2's complement 16 bit number. e.g. a hex value of F680 (=-2432) represents an offset of -4.75MHz.

#### 4.5.2 Frequency Error 1 and 2. Registers 111 - 115 (R)

| NAME        | ADR | В7                                                     | В6                                                         | B5        | B4        | В3       | B2     | B1       | В0   |    | Def<br>hex |

|-------------|-----|--------------------------------------------------------|------------------------------------------------------------|-----------|-----------|----------|--------|----------|------|----|------------|

| FREQ ERR1 H | 111 | FREQ E                                                 | RR1[23                                                     | :16] Inpu | t frequen | cy error | coarse | (high by | rte) | R  | 00         |

| FREQ ERR1 M | 112 | FREQ E                                                 | FREQ ERR1[15:8] Input frequency error coarse (middle byte) |           |           |          |        |          |      | R  | 00         |

| FREQ ERR1 L | 113 | FREQ ERR1[7:0] Input frequency error coarse (low byte) |                                                            |           |           |          |        |          | R    | 00 |            |

FREQ ERR1[23:0] Ratio of Frequency Compensation Mixer offset to System Clock x  $2^{24}$ . 24 bit signed number. For most purposes the LS byte can be ignored hence the alternative definition is more useful: FREQ ERR1[23:8] Ratio of Frequency Compensation Mixer offset to System Clock x  $2^{16}$ . 16 bit signed number.

| NAME        | ADR | В7                                                   | В6     | B5         | B4        | В3        | B2       | B1      | В0 |   | Def<br>hex |

|-------------|-----|------------------------------------------------------|--------|------------|-----------|-----------|----------|---------|----|---|------------|

| FREQ ERR2 H | 114 | FREC                                                 | ERR2[1 | 15:8] Inpu | ut freque | ncy error | fine (hi | gh byte | )  | R | 00         |

| FREQ ERR2 L | 115 | FREQ ERR2[7:0] Input frequency error fine (low byte) |        |            |           |           | R        | 00      |    |   |            |

FREQ ERR2 [16:0] Ratio of Carrier Synchroniser offset to Symbol Rate x 2<sup>8</sup>. 16 bit signed number. This value drops to near zero within a second or so of signal lock.

To obtain an accurate value for the frequency offset at any time, especially immediately after lock, the error from each of these registers can be calculated and add together. In practice only the two most significant bytes of FREQ ERR 1 are required, so that the net offset can be calculated as:

Frequency offset =

$$\frac{\text{FREQ\_ERR1}(23:8)^* \text{ PLL\_CLK}}{65536} + \frac{\text{FREQ\_ERR2}(15:0)^* \text{Rs}}{256}$$

Where PLL CLK is the sytem clock frequency (e.g. 60 MHz) and Rs is the symbol rate in MBd.

Any frequency error in FREQ ERR2 transfers to FREQ ERR1 very rapidly after lock, so that any delay between reading the two values will cause an error in the calculation. It is therefore recommended that the five bytes above are read as a block, especially if the two wire bus is subject to congestion or other delays.

# 5 DiSEqC Control

# 5.1 Screen Printouts of DiSEqC™ Waveforms

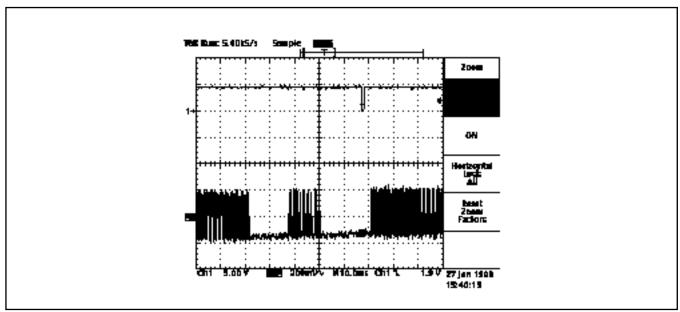

Figure 20 - A DiSEqC™ data byte interrupting a continuous 22kHz tone

The timing periods of the 16ms before the data byte and 16ms afterwards to the interrupt being asserted are clearly shown. The restoration of the 22kHz after the interrupt is controlled by software.

Figure 21 - One DiSEqC™ data byte - 0x11 (hex) plus parity bit

A 'zero' comprises 22kHz on for 1ms then off for 0.5ms. A 'one' comprises 22kHz on for 0.5ms then off for 1ms. The ninth bit is an odd parity bit.

#### 5.2 DiSEqC Control Read/Write Registers

### 5.2.1 DiSEqC™ Mode Control. Register 22 (R/W)

| NAME        | ADR | В7       | В6 | B5 | B4                  | В3 | B2 | B1     | В0 |     | Def<br>hex |

|-------------|-----|----------|----|----|---------------------|----|----|--------|----|-----|------------|

| DISEQC MODE | 22  | Reserved | HV |    | DISEQC<br>uction le |    | 22 | kHz mo | de | R/W | 00         |

B7: Reserved. Must be set low.

B6: HV H/V polarisation control: High = Horizontal, DISEQC[1] pin = high

Low = Vertical, DISEQC[1] pin = low

The DISEQC[1] pin controls the externally generated 13/18V LNB voltage.

B5-3: Number of bytes in DiSEqC™ instruction minus 1, to output on DISEQC[0] pin.

i.e. if the message contains four bytes, program B5-3 with the value three.

B2-0: DiSEqC™ mode:

0: 22kHz off

1: 22kHz on continuous

2: Burst mode - on for 12.5ms = '0'

3: Burst mode - modulated 1:2 for 12.5ms = '1'

4: Modulated with bytes from DISEQC INSTR

5-7: Reserved.

Note: for modes 2 and 3, an interrupt is generated 16ms after the '0' or '1' burst.

for mode 4, there is a 16ms delay before the message bytes, then an interrupt is generated 16ms after the last message byte has been sent. The requisite number of bytes must be pre-loaded into DISEQC INSTR (register 36) before this bit is set, see 31.

#### 5.2.2 DiSEqC(tm) Ratio. Register 35 (R/W)

| NAME         | ADR | В7 | В6 | B5   | В4      | В3     | B2 | B1 | В0 |     | Def<br>hex |

|--------------|-----|----|----|------|---------|--------|----|----|----|-----|------------|

| DISEQC RATIO | 35  |    |    | DISE | QC RATI | O[7:0] |    |    |    | R/W | 00         |

DISEQC RATIO[7:0] This must be programmed to set the Diseqc output tone frequency.

$$F_{out} = \frac{F_{xtal}}{4*DISEQC\_RATIO[7:0]}$$

Where  $F_{out}$  is in kHz and  $F_{xtal}$  is in MHz.

For a 22kHz output tone, DISEQC RATIO[7:0] = 11.364 \* F<sub>xtal</sub>

e.g. with  $F_{xtal} = 10MHz$ , DISEQC RATIO[7:0] = 114, or for 15 MHz 170.

For this example, the DiSEqC<sup>TM</sup> frequency =  $\frac{11E6}{4*125}$  = 22kHz.

For a 10MHz crystal, the tone frequency range is from 9.8kHz with DISEQC RATIO = 255 to 250kHz with DISEQC RATIO = 10. A lower value than 10 causes the tone frequency to become unstable, until the DISEQC RATIO = 0, the default, value giving a 22kHz tone frequency. This range is not guaranteed, the maximum tone frequency should be used with caution.

## 5.2.3 DiSEqC™ Instruction (R/W). Register 36 (R/W)

| NAME         | ADR | В7 | В6 | B5    | B4        | В3         | B2 | B1 | В0 |     | Def<br>hex |

|--------------|-----|----|----|-------|-----------|------------|----|----|----|-----|------------|

| DISEQC INSTR | 36  |    |    | DISEQ | C Instruc | tion [7:0] |    |    |    | R/W | 00         |

Up to eight instruction data bytes are first loaded into a bank of registers through this register. The 2-wire automatic register address incrementing is turned off during this loading by setting B7: IAI = 1 in RADD, (register address). The number of bytes (less one) must be defined in the DiSEqC™ instruction register DISEQC MODE[5:3].

i.e. DISEQC MODE[5:3] = (number of bytes in the DiSEqC™ instruction) - 1

When the DiSEqCTM instruction data bytes have been loaded, set DISEQC MODE[2:0] = 4. At the same time program DISEQC MODE[5:3] as required. The instruction data is modulated onto the 22kHz signal and output from the DISEQC[0] pin.

An interrupt is generated 16ms after all the data bytes have been sent and the MT312 then resets DISEQC MODE[5:0] to zero, see Figure 19 on page 33.

#### 5.2.4 DiSEqC™ 2 Control 1. Registers 121 (R/W)

| NAME             | ADR | В7 | В6 | B5   | В4      | В3       | B2 | B1 | В0 |     | Def<br>hex |

|------------------|-----|----|----|------|---------|----------|----|----|----|-----|------------|

| DISEQC2<br>CTRL1 | 121 |    |    | DISE | QC2 CTR | RL1[7:0] |    |    |    | R/W | 00         |

B7-6: MIN TONE PER Minimum Tone Period.

| B7-6: | MIN TONE PER         |

|-------|----------------------|

| 00    | 3.0 * DISEQC RATIO   |

| 01    | 3.125 * DISEQC RATIO |

| 10    | 2.875 * DISEQC RATIO |

| 11    | 2.75 * DISEQC RATIO  |

B7:6 are for controlling (or fine tuning) the DiSEqC™ 2 receive algorithm.

B5: Send extended pulse to the Status pin 52. This is a test or diagnostics bit. If it is set to 1, then the cleaned up and extended pulse stream is sent to the status pin so that it can be recorded or observed.

B4: DiSEqC™ 2 Reset only the DiSEqCTM 2 receive module. Automatically set low again after use.

# MT312 DiSEqC Control

This is the software (partial) reset for DISEQC2 module. If this is set to 1 in the DISEQC2 listen (or receive) period, any listen operations will be aborted and DISEQC2 will wait until the end of the next transmission to expect a reply.

Note that the host beginning the next DISEQC2 transmission will have a similar effect to writing bit 4.

B3: Interrupt enable for bit B3 of DISEQC2 INT STAT register 118.

B2: Interrupt enable for bit B2 of DISEQC2 INT STAT register 118.

B1: Interrupt enable for bit B1 of DISEQC2 INT STAT register 118.

B0: Interrupt enable for bit B0 of DISEQC2 INT STAT register 118.

Bits B0 and B3 are interrupt enables. These determine whether bits B0 to B3 of DISEQC2 INT (register 118, see 33) have any impact on the pin IRQ 57 of the MT312.

Note that buffer overflow interrupt does not have an interrupt enable and hence this cannot be brought out to the  $\overline{IRQ}$  pin.

### 5.2.5 DiSEqCTM 2 Control 2. Registers 122 (R/W)