## **Document Title**

## 2Mx16 bit Synchronous Burst Uni-Transistor Random Access Memory

## **Revision History**

| Revision No. | History                                                                                                    | Draft Date         | <u>Remark</u> |

|--------------|------------------------------------------------------------------------------------------------------------|--------------------|---------------|

| 0.0          | Initial Draft<br>- Design target                                                                           | September 02, 2004 | Preliminary   |

| 0.1          | Revised<br>- Corrected the name of 9th row of balls on the pakage to 'J' from 'I'<br>on page.2 and page.42 | November 01, 2004  | Preliminary   |

| 1.0          | Finalize                                                                                                   | April 06, 2005     | Final         |

The attached datasheets are provided by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications and products. SAMSUNG Electronics will answer to your questions about device. If you have any questions, please contact the SAMSUNG branch offices.

## 2M x 16 bit Synchronous Burst Uni-Transistor CMOS RAM

## FEATURES

- Process Technology: CMOS

- Organization: 2M x16 bit

- Power Supply Voltage: 1.7~2.0V

- Three State Outputs

- Supports MRS (Mode Register Set)

- MRS control Software Control

Supports Driver Strength Optimized

- Supports Driver Strength Optimization for system environment

Supports Async. 4-Page Read / Async. Write Mode

- Supports Async. 4-Page Read / Async. Write Mode

Supports Sync. Burst Read / Async. Write Mode (Address Latch Type and Low ADV Type)

- Supports Sync. Burst Read / Sync. Burst Write Mode

- Supports 4 word / 8 word / 16 word burst Length

- Supports Linear(Wrap) Burst type

- Latency support : Latency 5 @ 66MHz(tCD 10ns)

- Latency 4 @ 54MHz(tCD 10ns)

- Supports Burst Read Suspend

- Supports Burst Write Data Masking by /UB & /LB control

- Supports WAIT function to indicate data availability.

- Max. Burst Clock Frequency : 66MHz

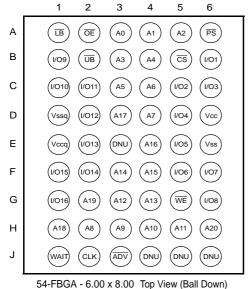

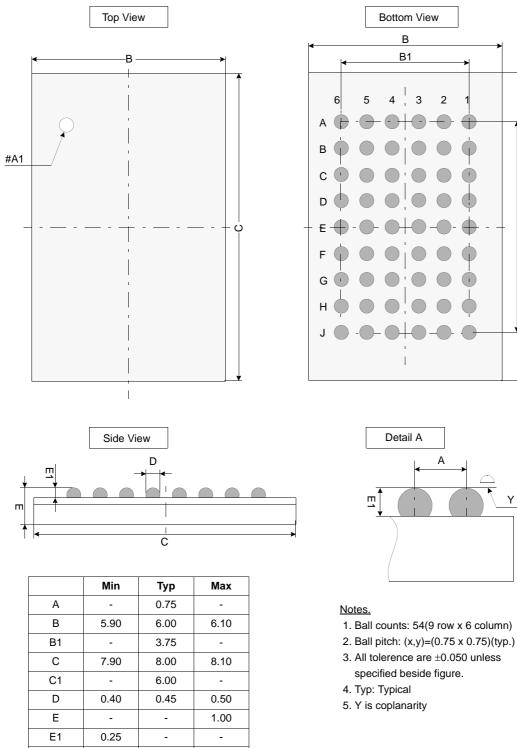

- Package Type : 54 FBGA 6.00 x 8.00

## **GENERAL DESCRIPTION**

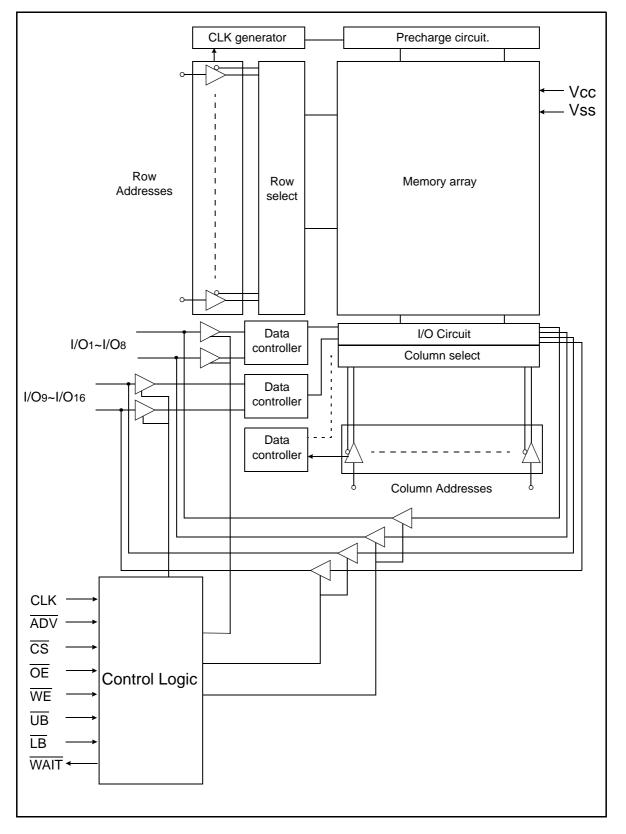

The world is moving into the mobile multi-media era and therefore the mobile handsets need much bigger memory capacity to handle the multi-media data. SAMSUNG's UtRAM products are designed to meet all the request from the various customers who want to cope with the fast growing mobile market. UtRAM is the perfect solution for the mobile market with its low cost, high density and high performance feature. K1B3216BDD is fabricated by SAMSUNG's advanced CMOS technology using one transistor memory cell. The device supports the traditional SRAM like asynchronous bus operation (asynchronous page read and asynchronous write), the NOR flash like synchronous bus operation (synchronous burst read and asynchronous write) and the fully synchronous bus operation (synchronous burst read and synchronous burst write). These three bus operation modes are defined through the mode register setting. The optimization of output driver strength is possible through the mode register setting to adjust for the different data loadings. Through this driver strength optimization, the device can minimize the noise generated on the data bus during read operation.

| Table 1. | PRODUCT FAMILY |

|----------|----------------|

|----------|----------------|

| Product Family | Operating Temp.      | Vcc Range | Clock Freq.<br>(Max) | Async. Speed<br>(tAA) | Power Dissipation<br>Standby Operating<br>(ISB1, Max.) (ICc2, Max.) |      | PKG Type               |

|----------------|----------------------|-----------|----------------------|-----------------------|---------------------------------------------------------------------|------|------------------------|

| K1B3216BDD-I   | Industrial(-40~85°C) | 1.7~2.0V  | 66MHz                | 70ns                  | 100uA                                                               | 35mA | 54 FBGA<br>6.00 x 8.00 |

## Fig.1 PIN DESCRIPTION

## Table 2. PIN DESCRIPTION

| Name       | Function            | Name | Function            |

|------------|---------------------|------|---------------------|

| CLK        | Clock Input         | Vcc  | Power Supply        |

| ADV        | Address Input Valid | Vccq | I/O Power Supply    |

| PS*        | Power Save          | Vss  | Ground              |

| CS         | Chip Select         | Vssq | I/O Ground          |

| OE         | Output Enable Input | UB   | Upper Byte(I/O9~16) |

| WE         | Write Enable Input  | LB   | Lower Byte(I/O1~8)  |

| A0~A20     | Address Inputs      | WAIT | Data Availability   |

| I/O1~I/O16 | Data Inputs/Outputs | DNU  | Do Not Use          |

\* PS must be tied to Vcc.

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

## CONTENTS

Page

| Revision History                                 | - 1  |

|--------------------------------------------------|------|

| Features and General Description                 |      |

| Power Up Sequence                                | - 7  |

| Functional Description                           |      |

| Mode Register Setting Operation                  | - 10 |

| Mode Register Setting Timing                     |      |

| Asynchronous Operation                           | -12  |

| Asynchronous 4 Page Read Operation               | -12  |

| Asynchronous Write Operation                     | -12  |

| Asynchronous Write Operation in Synchronous Mode | -12  |

| Synchronous Burst Operation                      | -12  |

| Synchronous Burst Read Operation                 | -12  |

| Synchronous Burst Write Operation                | -12  |

| Synchronous Burst Operation Terminology          | -13  |

| Clock                                            |      |

| Latency Count                                    | -13  |

| Burst Length                                     |      |

| Burst Stop                                       |      |

| WAIT Control                                     | -14  |

| Burst Type                                       |      |

| Product List                                     | 15   |

| Absolute Maximum Ratings                         | -15  |

| Recommended DC Operating Conditions              |      |

|                                                  | -15  |

| DC and Operating Characteristics                 | -15  |

| Asynchronous AC Characteristics                  | -16  |

| Asynchronous Timing Waveforms                    | -17  |

| Synchronous AC Characteristics                   | -26  |

| Synchronous Timing Waveforms                     | -27  |

| Transition Timing Waveforms                      | - 36 |

| Package Dimension                                | -42  |

| r dokugo Dimonolom                               | 74   |

## LIST of TABLES

UtRAM

| Table 1.  | Product Family                                                                              | 2  |

|-----------|---------------------------------------------------------------------------------------------|----|

| Table 2.  | Pin Description                                                                             | 2  |

| Table 3.  | Asynchronous 4 Page Read & Asynchronous Write Mode Truth Table                              | 8  |

| Table 4.  | Synchronous Burst Read & Asynchronous Write Mode Truth Table                                | 8  |

| Table 5.  | Synchronous Burst Read & Synchronous Burst Write Mode Truth Table                           | 9  |

| Table 6.  | Mode Register Setting according to Field of Function                                        | 10 |

| Table 7.  | Mode Register Set.                                                                          | 10 |

| Table 8.  | Latency Count Support                                                                       | 13 |

| Table 9.  | Number of Clocks for 1st Data                                                               | 13 |

|           | Burst Sequence                                                                              |    |

|           | Product List                                                                                |    |

| Table 12. | Absolute Maximum Ratings                                                                    | 15 |

| Table 13. | Recommended DC Operating Conditions                                                         | 15 |

| Table 14. | Capacitance                                                                                 | 15 |

| Table 15. | DC and Operating Characteristics                                                            | 15 |

| Table 16. | Asynchronous AC Characteristics                                                             | 16 |

| Table 17. | Asynchronous Read AC Characteristics                                                        | 17 |

| Table 18. | Asynchronous Page Read AC Characteristics                                                   | 18 |

| Table 19. | Asynchronous Write AC Characteristics(WE Controlled)                                        | 19 |

| Table 20. | Asynchronous Write AC Characteristics (UB & LB Controlled)                                  | 20 |

| Table 21. | Asynch. Write in Synch. Mode AC Characteristics(Address Latch Type, WE Controlled)          | 21 |

| Table 22. | Asynch. Write in Synch. Mode AC Characteristics (Address Latch Type, UB & LB Controlled)    | 22 |

| Table 23. | Asynch. Write in Synch. Mode AC Characteristics (Low ADV Type, WE Controlled)               | 23 |

| Table 24. | Asynch. Write in Synch. Mode AC Characteristics (Low ADV Type, UB & LB Controlled)          | 24 |

|           | Asynch. Write in Synch. Mode AC Characteristics(Low ADV Type Multiple Write, WE Controlled) |    |

|           | Synchronous AC Characteristics                                                              |    |

| Table 27. | Burst Operation AC Characteristics                                                          | 27 |

|           | Burst Read AC Characteristics(CS Toggling Consecutive Burst)                                |    |

|           | Burst Read AC Characteristics(CS Low Holding Consecutive Burst)                             |    |

| Table 30. | Burst Read AC Characteristics(Last Data Sustaining)                                         | 30 |

| Table 31. | Burst Write AC Characteristics(CS Toggling Consecutive Burst)                               | 31 |

| Table 32. | Burst Write AC Characteristics(CS Low Holding Consecutive Burst)                            | 32 |

| Table 33. | Burst Read Stop AC Characteristics                                                          | 32 |

| Table 34. | Burst Write Stop AC Characteristics                                                         | 33 |

| Table 35  | Burst Read Suspend AC Characteristics                                                       | 35 |

| Table 36. | Burst Read to Asynch. Write(Address Latch Type) AC Characteristics                          | 36 |

| Table 37  | Burst Read to Asynch. Write(Low ADV Type) AC Characteristics                                | 37 |

| Table 38  | Asynch. Write(Address Latch Type) to Burst Read AC Characteristics                          | 38 |

| Table 39  | Asynch. Write(Low ADV Type) to Burst Read AC Characteristics                                | 39 |

| Table 40  | Burst Read to Burst Write AC Characteristics                                                | 40 |

| Table 41  | Burst Write to Burst Read AC Characteristics                                                | 41 |

|           |                                                                                             |    |

## LIST of FIGURES

# Page

UtRAM

|            | Pin Description                                                                      |    |

|------------|--------------------------------------------------------------------------------------|----|

| Figure 2.  | Functional Block Diagram                                                             | 6  |

| Figure 3.  | Power Up Timing                                                                      | 7  |

| Figure 4.  | Standby Mode State Machine                                                           | 7  |

| Figure 5.  | Mode Register Setting Timing                                                         | 11 |

| Figure 6.  | Asynchronous 4-Page Read                                                             | 12 |

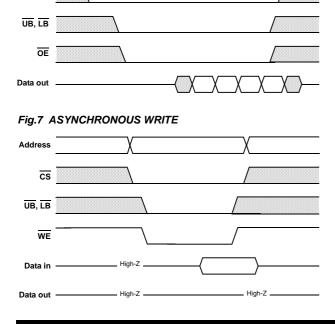

| Figure 7.  | Asynchronous Write                                                                   | 12 |

| Figure 8.  | Synchronous Burst Read                                                               | 12 |

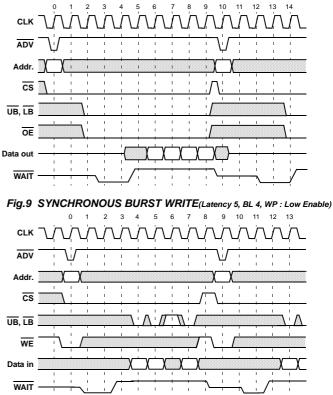

| Figure 9.  | Synchronous Burst Write                                                              | 12 |

| Figure 10. | Latency Configuration(Read)                                                          | 13 |

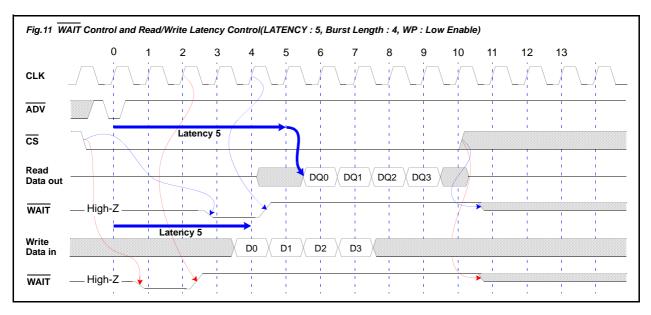

| Figure 11. | WAIT Control and Read/Write Latency Control                                          | 14 |

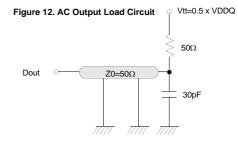

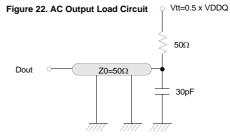

| Figure 12. | AC Output Load Circuit(Asynchronous)                                                 | 16 |

| Figure 13. | Timing Waveform of Asynchronous Read Cycle                                           | 17 |

| Figure 14. | Timing Waveform of Page Read Cycle                                                   | 28 |

| Figure 15. | Timing Waveform of Write Cycle(Asynchronous, WE Controlled).                         | 19 |

| Figure 16. | Timing Waveform of Write Cycle(Asynchronous, UB & LB Controlled)                     | 20 |

| Figure 17. | Timing Waveform of Write Cycle(Asynchronous, Address Latch Type, WE Controlled)      | 21 |

| Figure 18. | Timing Waveform of Write Cycle(Asynchronous, Address Latch Type, UB & LB Controlled) | 22 |

| Figure 19. | Timing Waveform of Write Cycle(Asynchronous, Low ADV Type, WE Controlled)            | 23 |

| Figure 20. | Timing Waveform of Write Cycle(Asynchronous, Low ADV Type, UB & LB Controlled)       | 24 |

| Figure 21. | Timing Waveform of Multiple Write Cycle(Asynchronous, Low ADV Type, WE Controlled.)  | 25 |

|            | AC Output Load Circuit(Synchronous)                                                  |    |

| Figure 23. | Timing Waveform of Basic Burst Operation                                             | 27 |

|            | Timing Waveform of Burst Read Cycle(CS Toggling Consecutive Burst Read)              |    |

| Figure 25. | Timing Waveform of Burst Read Cycle(CS Low Holding Consecutive Burst Read)           | 29 |

|            | Timing Waveform of Burst Read Cycle(Last Data Sustaining)                            |    |

| Figure 27. | Timing Waveform of Burst Write Cycle(CS Toggling Consecutive Burst Write)            | 31 |

|            | Timing Waveform of Burst Write Cycle(CS Low Holding Consecutive Burst Write).        |    |

|            | Timing Waveform of Burst Read Stop by $\overline{CS}$                                |    |

| Figure 30. | Timing Waveform of Burst Write Stop by $\overline{CS}$                               | 34 |

| Figure 31. | Timing Waveform of Burst Read Suspend Cycle                                          | 35 |

|            | Synch. Burst Read to Asynch. Write(Address Latch Type) Timing Waveform               |    |

|            | Synch. Burst Read to Asynch. Write(Low ADV Type) Timing Waveform                     |    |

|            | Asynch. Write(Address Latch Type) to Synch. Burst Read Timing Waveform               |    |

| Figure 35. | Asynch. Write(Low ADV Type) to Synch. Burst Read Timing Waveform                     | 39 |

|            | Synch. Burst Read to Synch. Burst Write Timing Waveform                              |    |

| Figure 37. | Synch. Burst Write to Synch. Burst Read Timing Waveform                              | 41 |

| -          |                                                                                      |    |

## Fig.2 FUNCTIONAL BLOCK DIAGRAM

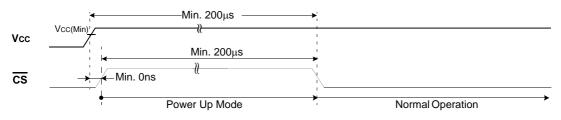

## POWER UP SEQUENCE

After applying Vcc upto minimum operating voltage(1.7V), drive  $\overline{CS}$  High. Then the device gets into the Power Up mode. Wait for minimum 200µs to get into the normal operation mode. During the Power Up mode, the standby current can not be guaranteed. To get the stable standby current level, at least one cycle of active operation should be implemented regardless of wait time duration. To get the appropriate device operation, be sure to keep the following power up sequence. 1. Apply power.

2. Maintain stable power(Vcc min.=1.7V) for a minimum 200 $\mu$ s with  $\overline{CS}$  high.

## Fig.3 POWER UP TIMING

## Fig.4 STANDBY MODE STATE MACHINES

Default mode after power up is Asynchronous mode (4 Page Read and Asynchronous Write). But this default mode is not 100% guaranteed so MRS setting sequence is highly recommended after power up.

## **FUNCTIONAL DESCRIPTION**

### Table 3. ASYNCHRONOUS 4 PAGE READ & ASYNCHRONOUS WRITE MODE (A15/A14=0/0)

| CS | OE              | WE              | LB              | UB              | I/O0~7 | <b>I/O</b> 8~15 | Mode             | Power   |

|----|-----------------|-----------------|-----------------|-----------------|--------|-----------------|------------------|---------|

| н  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z | High-Z          | Deselected       | Standby |

| L  | н               | н               | X <sup>1)</sup> | X <sup>1)</sup> | High-Z | High-Z          | Output Disabled  | Active  |

| L  | X <sup>1)</sup> | X <sup>1)</sup> | н               | н               | High-Z | High-Z          | Output Disabled  | Active  |

| L  | L               | н               | L               | н               | Dout   | High-Z          | Lower Byte Read  | Active  |

| L  | L               | Н               | н               | L               | High-Z | Dout            | Upper Byte Read  | Active  |

| L  | L               | Н               | L               | L               | Dout   | Dout            | Word Read        | Active  |

| L  | Н               | L               | L               | Н               | Din    | High-Z          | Lower Byte Write | Active  |

| L  | Н               | L               | Н               | L               | High-Z | Din             | Upper Byte Write | Active  |

| L  | Н               | L               | L               | L               | Din    | Din             | Word Write       | Active  |

1. X must be VIL or VIH.

In asynchronous mode, Clock and ADV are ignored.

/WAIT pin is High-Z in Asynchronous mode.

### Table 4. SYNCHRONOUS BURST READ & ASYNCHRONOUS WRITE MODE(A15/A14=0/1)

| CS | OE              | WE              | LB              | UB              | <b>I/O</b> 0~7 | <b>I/O</b> 8~15 | CLK             | ADV              | Mode             | Power   |

|----|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|-----------------|------------------|------------------|---------|

| н  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | X <sup>1)</sup> | X <sup>1)</sup>  | Deselected       | Standby |

| L  | Н               | н               | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | X <sup>1)</sup> | Н                | Output Disabled  | Active  |

| L  | X <sup>1)</sup> | X <sup>1)</sup> | н               | н               | High-Z         | High-Z          | X <sup>1)</sup> | Н                | Output Disabled  | Active  |

| L  | X <sup>1)</sup> | н               | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | 5               |                  | Read Command     | Active  |

| L  | L               | Н               | L               | н               | Dout           | High-Z          |                 | Н                | Lower Byte Read  | Active  |

| L  | L               | н               | н               | L               | High-Z         | Dout            |                 | Н                | Upper Byte Read  | Active  |

| L  | L               | н               | L               | L               | Dout           | Dout            |                 | Н                | Word Read        | Active  |

| L  | Н               | L               | L               | Н               | Din            | High-Z          | X <sup>1)</sup> | ⁻∟ or Ъ́         | Lower Byte Write | Active  |

| L  | Н               | L               | н               | L               | High-Z         | Din             | X <sup>1)</sup> | ⁻∟ or ЪГ         | Upper Byte Write | Active  |

| L  | Н               | L               | L               | L               | Din            | Din             | X <sup>1)</sup> | ⁻∟ or <b>ጊ</b> ୮ | Word Write       | Active  |

X must be VIL or VIH.

/WAIT is device output signal so does not have any affect to the mode definition. Please refer to each timing diagram for /WAIT pin function.

| CS | OE              | WE              | LB              | UB              | <b>I/O</b> 0~7 | <b>I/O</b> 8~15 | CLK             | ADV                | Mode             | Power   |

|----|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|-----------------|--------------------|------------------|---------|

| Н  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | X <sup>1)</sup> | X <sup>1)</sup>    | Deselected       | Standby |

| L  | н               | н               | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | X <sup>1)</sup> | Н                  | Output Disabled  | Active  |

| L  | X <sup>1)</sup> | X <sup>1)</sup> | Н               | Н               | High-Z         | High-Z          | X <sup>1)</sup> | Н                  | Output Disabled  | Active  |

| L  | X <sup>1)</sup> | Н               | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          |                 |                    | Read Command     | Active  |

| L  | L               | н               | L               | н               | Dout           | High-Z          |                 | Н                  | Lower Byte Read  | Active  |

| L  | L               | Н               | Н               | L               | High-Z         | Dout            |                 | Н                  | Upper Byte Read  | Active  |

| L  | L               | н               | L               | L               | Dout           | Dout            |                 | Н                  | Word Read        | Active  |

| L  | X <sup>1)</sup> | LorЪ            | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          |                 |                    | Write Command    | Active  |

| L  | н               | X <sup>1)</sup> | L               | Н               | Din            | High-Z          |                 | Н                  | Lower Byte Write | Active  |

| L  | н               | X <sup>1)</sup> | Н               | L               | High-Z         | Din             |                 | H Upper Byte Write |                  | Active  |

| L  | н               | X <sup>1)</sup> | L               | L               | Din            | Din             |                 | Н                  | Word Write       | Active  |

#### Table 5. SYNCHRONOUS BURST READ & SYNCHRONOUS WRITE MODE(A15/A14=1/0)

1. X must be VIL or VIH.

WAIT is device output signal so does not have any affect to the mode definition. Please refer to each timing diagram for /WAIT pin function.

The last data written in the previous Asynchronous write mode is not valid. To make the lastly written data valid, then implement at least one dummy write cycle before change mode into synchronous burst read and synchronous burst write mode.

5. The data written in Synchronous burst write operation can be corrupted by the next Asynchronous write operation. So the transition from Synchronous burst write operation to Asynchronous write operation is prohibited.

### MODE REGISTER SETTING OPERATION

The device has several modes : Asynchronous Page Read mode, Asynchronous Write mode, Synchronous Burst Read mode, Synchronous Burst Write mode, Standby mode. Mode Register Set(MRS) option also defines Burst Length, Burst Type, Wait Polarity and Latency Count at Synchronous Burst Read/Write mode.

#### Mode Register Set (MRS)

The mode register stores the data for controlling the various operation modes of UtRAM. It programs Burst Length, Burst Type, Latency Count and various vendor specific options to make UtRAM useful for a variety of different applications. The default values of mode register are defined, therefore when the reserved address is input, the device runs at default modes. The mode register is written by driving CS, ADV, WE, UB, LB to VIL and OE to VIH during valid address. The mode register is divided into various fields depending on the fields of functions. Burst Length field uses A5~A7, Burst Type uses A8, Latency Count uses A9~A11, Wait Polarity uses A13, Operation Mode uses A14~A15 and Driver Strength uses A16~A17.

Refer to the Table below for detailed Mode Register Setting. A18~A22 addresses are "Don't care" in Mode Register Setting.

#### Table 6. Mode Register Setting according to field of function

| Address  | A17~A16 | A15~A14 | A13 | A12 | A11~A9  | A8 | A7~A5 | A4~A0 |

|----------|---------|---------|-----|-----|---------|----|-------|-------|

| Function | DS      | MS      | WP  | RFU | Latency | BT | BL    | RFU   |

NOTE : DS(Driver Strength), MS(Mode Select), WP(Wait Polarity), Latency(Latency Count), BT(Burst Type), BL(Burst Length), RFU(Reserved for Future Use)

|     | Drive    | er Strengt | h     |      |     |     | Mode     | Select   | :             |          |           |    |    |          |       |

|-----|----------|------------|-------|------|-----|-----|----------|----------|---------------|----------|-----------|----|----|----------|-------|

| A17 | A16      |            | DS    | A15  | A14 |     |          |          | MS            |          |           |    |    |          |       |

| 0   | 0        | Ful        | Drive | 0    | 0   |     | Async. 4 | Page I   | Read / Async  | . Write  |           |    |    |          |       |

| 0   | 1        | 1/2        | Drive | 0    | 1   |     | Sync. E  | Burst Re | ead / Async.  | Write    |           |    |    |          |       |

| 1   | 0        | 1/4        | Drive | 1    | 0   | S   | ync. Bu  | rst Rea  | d / Sync. Bur | st Write | e         |    |    |          |       |

| W   | AIT Pola | arity      |       | RFU  |     |     | Later    | ος Οοι   | unt           | В        | urst Type |    | E  | Burst Le | ength |

| A13 | ١        | WP         | A12   | RFU  |     | A11 | A10      | A9       | Latency       | A8       | вт        | A7 | A6 | A5       |       |

| 0   | Low      | Enable     | 0     | Must | :   | 0   | 0        | 0        | 3             | 0        | Linear    | 0  | 1  | 0        | 4     |

| 1   | Linda    |            |       |      |     | 0   | 0        | 1        | 4             | 4        | DNU*      | 0  | 1  | 1        | 8     |

|     | High     | Enable     | 1     | DNU  |     | 0   | 0        | 1        | 4             | 1        | DNU       | 0  | 1  | 1        | 0     |

#### Table 7. Mode Register Set

\* DNU: Do Not Use.

NOTE :

\* The address bits other than those listed in the table above are reserved.

For example, Burst Length address bits(A7:A6:A5) have 4 sets of reserved bits like 0:0:0, 0:0:1, 1:0:1 and 1:1:0.

1

0

If the reserved address bits are input, then the mode will be set into the default mode. Each field has its own default mode and these default modes are written in blue-bold in the table above.

1

6

\* A12 is a reserved bit for future use. A12 must be set as "0".

\* Not all the mode settings are tested. Per the mode settings to be tested.

\* The last data written in the previous Asynchronous write mode is not valid. To make the lastly written data valid, then implement at least one dummy write cycle before change mode into synchronous burst read and synchronous burst write mode.

\* The data written in Synchronous burst write operation can be corrupted by the next Asynchronous write operation. So the transition from Synchronous burst write operation to Asynchronous write operation is prohibited.

BL 4 word 8 word 16 word

DNU\*

1

1

1

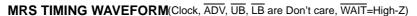

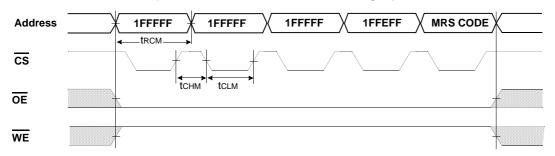

## MODE REGISTER SETTING TIMING

This device supports software access control type mode register setting timing. This timing consists of 5 cycles of Read operation. Each cycle of Read Operation is normal asynchronous read operation. Clock and ADV are don't care and WAIT signal is High-Z. CS should be toggling between cycles. The address for 1st, 2nd and 3rd cycle should be 1FFFFF(h) and the address for 4th cycle should be 1FFEFF. The address for 5th cycle should be MRS code(Register setting values).

## AC CHARACTERISTICS

| Parameter           | Sym-         | Min | Max | Unit | Parameter          | Sym-         | Mi | Ма | Unit |

|---------------------|--------------|-----|-----|------|--------------------|--------------|----|----|------|

| Read Cycle time     | <b>t</b> RCM | 70  | -   | ns   | CS Low pulse width | <b>t</b> CLM | 60 | -  | ns   |

| CS High pulse width | tснм         | 10  | -   | ns   |                    |              |    |    |      |

### **ASYNCHRONOUS OPERATION**

#### **Asynchronous 4 Page Read Operation**

Asynchronous normal read operation starts when  $\overline{CS}$ ,  $\overline{OE}$  and  $\overline{UB}$  or  $\overline{LB}$  are driven to VIL under the valid address without toggling page addresses(A0, A1). If the page addresses(A0, A1) are toggled under the other valid address, the first data will be out with the normal read cycle time(tRC) and the second, the third and the fourth data will be out with the page cycle time(tPC). ( $\overline{WE}$  should be driven to VIH during the asynchronous (page) read operation)

Clock, ADV, WAIT signals are ignored during the asynchronous (page) read operation.

### **Asynchronous Write Operation**

Asynchronous write operation starts when  $\overline{CS}$ ,  $\overline{WE}$  and  $\overline{UB}$  or  $\overline{LB}$  are driven to VIL under the valid address.( $\overline{OE}$  should be driven to VIH during the asynchronous write operation.) Clock,  $\overline{ADV}$ ,  $\overline{WAIT}$  signals are ignored during the asynchronous (page) read operation.

### Asynchronous Write Operation in Synchronous Mode

A write operation starts when  $\overline{CS}$ ,  $\overline{WE}$  and  $\overline{UB}$  or  $\overline{LB}$  are driven to V<sub>IL</sub> under the valid address. Clock input does not have any affect to the write operation( $\overline{OE}$  should be driven to V<sub>IH</sub> during write operation. ADV can be either toggling for address latch or held in V<sub>IL</sub>). Clock,  $\overline{ADV}$ ,  $\overline{WAIT}$  signals are ignored during the asynchronous (page) read operation.

#### Fig.6 ASYNCHRONOUS 4-PAGE READ

A22~A2

A1~A0

CS

## SYNCHRONOUS BURST OPERATION

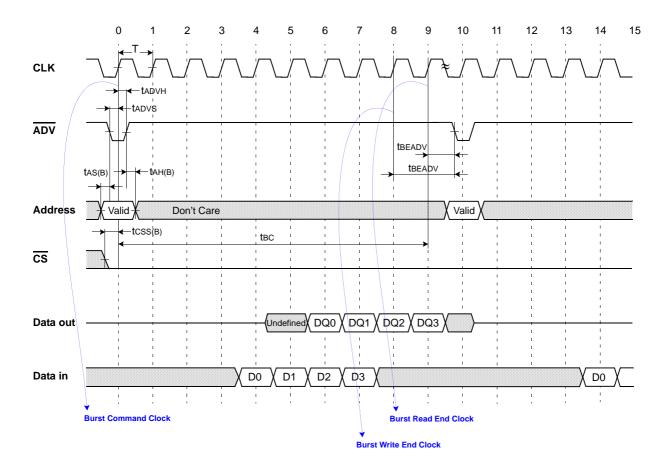

Burst mode operations enable the system to get high performance read and write operation. The address to be accessed is latched on the rising edge of clock or ADV(whichever occurs first). CS should be setup before the address latch. During this first clock rising edge, WE indicates whether the operation is going to be a Read(WE High) or a Write(WE Low). For the optimized Burst Mode to each system, the system should determine how many clock cycles are required for the first data of each burst access(Latency Count), how many words the device outputs at an access(Burst Length) and which type of burst operation(Burst Type : Linear ) is needed. The Wait Polarity should also be determined.(See Table "Mode Register Set")

#### **Synchronous Burst Read Operation**

The Synchronous Burst Read command is implemented when the clock rising is detected during the  $\overline{\text{ADV}}$  low pulse.  $\overline{\text{ADV}}$  and  $\overline{\text{CS}}$  should be set up before the clock rising. During Read command,  $\overline{\text{WE}}$  should be held in VIH. The multiple clock risings(during low  $\overline{\text{ADV}}$  period) are allowed but the burst operation starts from the first clock rising. The first data will be out with Latency count and tCD.

#### **Synchronous Burst Write Operation**

The Synchronous Burst Write command is implemented when the clock rising is detected during the  $\overline{ADV}$  and  $\overline{WE}$  low pulse.  $\overline{ADV}$ ,  $\overline{WE}$  and  $\overline{CS}$  should be set up before the clock rising. The multiple clock risings(during low  $\overline{ADV}$  period) are allowed but the burst operation starts from the first clock rising. The first data will be written in the Latency clock with tDS.

Fig.8 SYNCHRONOUS BURST READ(Latency 5, BL 4, WP : Low Enable)

SAMSUNG

Revision 1.0 April 2005

#### SYNCHRONOUS BURST OPERATION TERMINOLOGY

#### Clock(CLK)

The clock input is used as the reference for synchronous burst read and write operation of UtRAM. The synchronous burst read and write operation is synchronized to the rising edge of the clock. The clock transitions must swing between VIL and VIH.

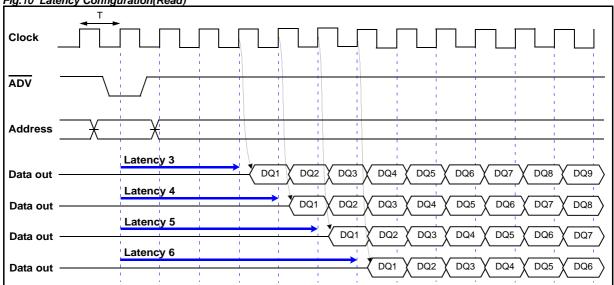

#### Latency Count

The Latency Count configuration tells the device how many clocks must elapse from the burst command before the first data should be available on its data pins. This value depends on the input clock frequency. The supported Latency Count is as follows.

#### Table 8. Latency Count support : 3, 4, 5

| Clock Frequency | Upto 66MHz | Upto 54MHz | Upto 40MHz |

|-----------------|------------|------------|------------|

| Latency Count   | 5          | 4          | 3          |

#### Table 9. Number of Clocks for 1st Data

| Set Latency                     | Latency 3 | Latency 4 | Latency 5 |

|---------------------------------|-----------|-----------|-----------|

| # of Clocks for 1st data(Read)  | 4         | 5         | 6         |

| # of Clocks for 1st data(Write) | 2         | 3         | 4         |

## Fig.10 Latency Configuration(Read)

NOTE : The first data will always keep the Latency. From the second data, some period of wait time might be caused by WAIT pin.

#### **Burst Length**

Burst Length identifies how many data the device outputs at an access. The device supports 4 word, 8 word and 16 word burst read or write. The first data will be out with the set Latency + tCD. From the second data, the data will be out with tCD from each clock.

#### **Burst Stop**

Burst stop is used when the system wants to stop burst operation on special purpose. If driving CS to VIH during the burst read operation, then the burst operation will be stopped. During the burst read operation, the new burst operation can not be issued. The new burst operation can be issued only after the previous burst operation is finished.

The burst stop feature is very useful because it enables the user to utilize the un-supported burst length such as 1 burst or 2 burst which accounts for big portion in usage for the mobile handset application environment.

## SYNCHRONOUS BURST OPERATION TERMINOLOGY

### WAIT Control(WAIT)

The WAIT signal is the device's output signal which indicates to the host system when the device's data-out or data-in is valid. To be compatible with the Flash interfaces of various microprocessor types, the WAIT polarity(WP) can be configured. The polarity can be programmed to be either low enable or high enable.

For the timing of WAIT signal, the WAIT signal should be set active one clock prior to the data regardless of Read or Write cycle.

#### **Burst Type**

The device supports Linear type burst sequence. Linear type burst sequentially increments the burst address from the starting address. The detailed Linear type burst address sequence is shown in burst sequence table.

| Start  | Burst Address Sequence(Decimal) |                 |                                       |  |  |  |  |  |  |  |

|--------|---------------------------------|-----------------|---------------------------------------|--|--|--|--|--|--|--|

| Length | 4 word Burst                    | 8 word Burst    | 16 word Burst                         |  |  |  |  |  |  |  |

| 0      | 0-1-2-3                         | 0-1-2-3-4-5-6-7 | 0-1-2-3-4-5-6-7-8-9-10-11-12-13-14-15 |  |  |  |  |  |  |  |

| 1      | 1-2-3-0                         | 1-2-3-4-5-6-7-0 | 1-2-3-4-5-6-7-8-9-10-11-12-13-14-15-0 |  |  |  |  |  |  |  |

| 2      | 2-3-0-1                         | 2-3-4-5-6-7-0-1 | 2-3-4-5-6-7-8-9-10-11-12-13-14-15-0-1 |  |  |  |  |  |  |  |

| 3      | 3-0-1-2                         | 3-4-5-6-7-0-1-2 | 3-4-5-6-7-8-9-10-11-12-13-14-15-0-1-2 |  |  |  |  |  |  |  |

| 4      |                                 | 4-5-6-7-0-1-2-3 | 4-5-6-7-8-9-10-11-12-13-14-15-0-1-2-3 |  |  |  |  |  |  |  |

| 5      |                                 | 5-6-7-0-1-2-3-4 | 5-6-7-8-9-10-11-12-13-14-15-0-1-2-3-4 |  |  |  |  |  |  |  |

| 6      |                                 | 6-7-0-1-2-3-4-5 | 6-7-8-9-10-11-12-13-14-15-0-1-2-3-4-5 |  |  |  |  |  |  |  |

| 7      |                                 | 7-0-1-2-3-4-5-6 | 7-8-9-10-11-12-13-14-15-0-1-2-3-4-5-6 |  |  |  |  |  |  |  |

| ~      |                                 |                 | ~                                     |  |  |  |  |  |  |  |

| 14     |                                 |                 | 14-15-0-1-2-3-4-5-6-7-8-9-10-11-12-13 |  |  |  |  |  |  |  |

| 15     |                                 |                 | 15-0-1-2-3-4-5-6-7-8-9-10-11-12-13-14 |  |  |  |  |  |  |  |

#### Table 11. PRODUCT LIST

| Industrial Temperature Products (-40~85°C) |                   |  |  |  |  |  |

|--------------------------------------------|-------------------|--|--|--|--|--|

| Part Name                                  | Function          |  |  |  |  |  |

| K1B3216BDD                                 | 1.8V, 70ns, 66MHz |  |  |  |  |  |

#### Table 12. ABSOLUTE MAXIMUM RATINGS<sup>1)</sup>

| Item                                 | Symbol    | Ratings          | Unit |

|--------------------------------------|-----------|------------------|------|

| Voltage on any pin relative to Vss   | VIN, VOUT | -0.2 to Vcc+0.3V | V    |

| Power supply voltage relative to Vss | Vcc       | -0.2 to 2.5V     | V    |

| Power Dissipation                    | PD        | 1.0              | W    |

| Storage temperature                  | Тѕтс      | -65 to 150       | °C   |

| Operating Temperature                | ТА        | -40 to 85        | °C   |

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation should be restricted to be used under recommended operating condition. Exposure to absolute maximum rating conditions longer than 1 second may affect reliability.

### Table 13. RECOMMENDED DC OPERATING CONDITIONS<sup>1)</sup>

| Item                 | Symbol | Min                | Тур  | Max       | Unit |

|----------------------|--------|--------------------|------|-----------|------|

| Power supply voltage | Vcc    | 1.7                | 1.85 | 2.0       | V    |

| Ground               | Vss    | 0                  | 0    | 0         | V    |

| Input high voltage   | Vін    | 0.8 x Vcc          | -    | Vcc+0.22) | V    |

| Input low voltage    | VIL    | -0.2 <sup>3)</sup> | -    | 0.3       | V    |

1. TA=-40 to 85°C, otherwise specified.

2. Overshoot: Vcc+1.0V in case of pulse width  $\leq$ 3ns. 3. Undershoot: -1.0V in case of pulse width  $\leq$ 3ns.

4. Overshoot and undershoot are sampled, not 100% tested.

## Table 14. CAPACITANCE<sup>1</sup>(f=1MHz, TA=25°C)

| Item                     | Symbol | Test Condition | Min | Max | Unit |

|--------------------------|--------|----------------|-----|-----|------|

| Input capacitance        | CIN    | VIN=0V         | -   | 8   | pF   |

| Input/Output capacitance | Сю     | Vio=0V         | -   | 10  | pF   |

1. Capacitance is sampled, not 100% tested.

## Table 15. DC AND OPERATING CHARACTERISTICS

| Item                         | Symbol             | Test Conditions                                                                    | Min | Тур | Max | Unit |

|------------------------------|--------------------|------------------------------------------------------------------------------------|-----|-----|-----|------|

| Input Leakage Current        | Iц                 | VIN=Vss to Vcc                                                                     | -1  | -   | 1   | μA   |

| Output Leakage Current       | Ilo                | $\overline{CS}$ =VIH, $\overline{OE}$ =VIH or $\overline{WE}$ =VIL, VIO=Vss to VCC | -1  | -   | 1   | μA   |

| Average Operating<br>Current | ICC2               | Cycle time=tRC+3tPC, IIO=0mA, 100% duty, $\overline{CS}$ =VIL, VIN=VIL or VIH      | -   | -   | 35  | mA   |

| Output Low Voltage           | Vol                | lo∟=0.1mA                                                                          | -   | -   | 0.2 | V    |

| Output High Voltage          | Vон                | Іон=-0.1mA                                                                         | 1.4 | -   | -   | V    |

| Standby Current(CMOS)        | ISB1 <sup>1)</sup> | CS≥Vcc-0.2V, Other inputs=Vss to Vcc                                               | -   | -   | 100 | μΑ   |

1. Standby mode is supposed to be set up after at least one active operation.

ISB1 is measured after 60ms from the time when standby mode is set up.

## AC OPERATING CONDITIONS

**TEST CONDITIONS**(Test Load and Test Input/Output Reference) Input pulse level: 0.2 to Vcc-0.2V Input rising and falling time: 3ns Input and output reference voltage: 0.5 x Vcc Output load: CL=30pF

## Table 16. ASYNCHRONOUS AC CHARACTERISTICS (Vcc=1.7~2.0V, TA=-40 to 85°C)

|        | Devementer List                           | Symbol        | :                | Speed           | Units |

|--------|-------------------------------------------|---------------|------------------|-----------------|-------|

|        | Parameter List                            | Symbol        | Min              | Max             | Units |

|        | CS High pulse width                       | <b>t</b> CSHP | 10               | -               | ns    |

|        | Read Cycle Time                           | tRC           | 70               | -               | ns    |

|        | Page Read Cycle Time                      | tPC           | 25               | -               | ns    |

|        | Address Access Time                       | tAA           | -                | 70              | ns    |

|        | Page Access Time                          | <b>t</b> PA   | -                | 20              | ns    |

|        | Chip Select to Output                     | tco           | -                | 70              | ns    |

| Async. | Output Enable to Valid Output             | tOE           | -                | 35              | ns    |

| (Page) | UB, LB Access Time                        | tва           | -                | 35              | ns    |

| Read   | Chip Select to Low-Z Output               | tLZ           | 10               | -               | ns    |

|        | UB, LB Enable to Low-Z Output             | tBLZ          | 5                | -               | ns    |

|        | Output Enable to Low-Z Output             | tolz          | 5                | -               | ns    |

|        | Chip Disable to High-Z Output             | tснz          | 0                | 12              | ns    |

|        | UB, LB Disable to High-Z Output           | tвнz          | 0                | 12              | ns    |

|        | Output Disable to High-Z Output           | tонz          | 0                | 12              | ns    |

|        | Output Hold                               | toн           | 3                | -               | ns    |

|        | Write Cycle Time                          | twc           | 70               | -               | ns    |

|        | Chip Select to End of Write               | tcw           | 60               | -               | ns    |

|        | ADV Minimum Low Pulse Width               | tadv          | 7                | -               | ns    |

|        | Address Set-up Time to Beginning of Write | tas           | 0                | -               | ns    |

|        | Address Set-up Time to ADV Falling        | tas(a)        | 0                | -               | ns    |

|        | Address Hold Time from ADV Rising         | tAH(A)        | 7                | -               | ns    |

| Async. | CS Setup Time to ADV Rising               | tCSS(A)       | 10               | -               | ns    |

| Write  | Address Valid to End of Write             | taw           | 60               | -               | ns    |

|        | UB, LB Valid to End of Write              | tBW           | 60               | -               | ns    |

|        | Write Pulse Width                         | twp           | 55 <sup>1)</sup> | -               | ns    |

|        | WE High Pulse Width                       | twhp          | 5 ns             | Latency-1 clock | -     |

|        | Write Recovery Time                       | twr           | 0                | -               | ns    |

|        | WE Low to Read Latency                    | twlrl         | 1                | -               | clock |

|        | Data to Write Time Overlap                | tDW           | 30               | -               | ns    |

|        | Data Hold from Write Time                 | tdн           | 0                | -               | ns    |

1. tWC(min)=90ns or tWP(min)=70ns for continuous write operation over 50 times.

## U*t*RAM

## ASYNCHRONOUS READ TIMING WAVEFORM

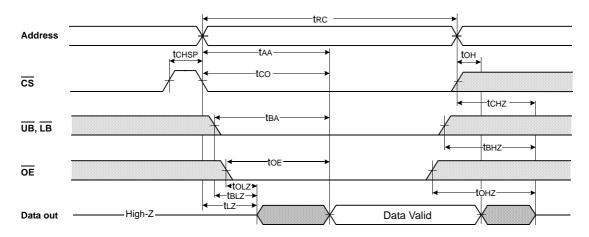

### Fig.13 TIMING WAVEFORM OF ASYNCHRONOUS READ CYCLE (WE=VIH, WAIT=High-Z)

(ASYNCHRONOUS READ CYCLE)

1. tCHZ and tOHZ are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels. 2. At any given temperature and voltage condition, tCHZ(Max.) is less than tLZ(Min.) both for a given device and from device to device

interconnection.

3. In asynchronous read cycle, Clock, ADV and WAIT signals are ignored.

| Symbol        | Speed |     | Units Symbol | Sp     | Units |     |      |

|---------------|-------|-----|--------------|--------|-------|-----|------|

| Gymbol        | Min   | Max | onno         | Cymbol | Min   | Max | onno |

| tRC           | 70    | -   | ns           | tolz   | 5     | -   | ns   |

| taa           | -     | 70  | ns           | tBLZ   | 5     | -   | ns   |

| tco           | -     | 70  | ns           | tLZ    | 10    | -   | ns   |

| tBA           | -     | 35  | ns           | tснz   | 0     | 12  | ns   |

| tOE           | -     | 35  | ns           | tвнz   | 0     | 12  | ns   |

| tон           | 3     | -   | ns           | tонz   | 0     | 12  | ns   |

| <b>t</b> CSHP | 10    | -   | ns           |        |       |     |      |

#### Table 17. ASYNCHRONOUS READ AC CHARACTERISTICS

## ASYNCHRONOUS READ TIMING WAVEFORM

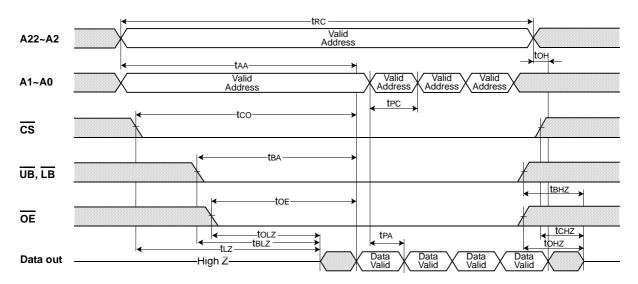

Fig.14 TIMING WAVEFORM OF PAGE READ CYCLE(WE=VIH, WAIT=High-Z)

(ASYNCHRONOUS 4 PAGE READ CYCLE)

1. tCHZ and tOHZ are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels. 2. At any given temperature and voltage condition, tCHZ(Max.) is less than tLZ(Min.) both for a given device and from device to device

interconnection. 3. In asynchronous 4 page read cycle, Clock,  $\overline{\text{ADV}}$  and  $\overline{\text{WAIT}}$  signals are ignored.

## Table 18. ASYNCHRONOUS PAGE READ AC CHARACTERISTICS

| Symbol      | Speed |     | Units Symbol | Sp     | Units |     |       |

|-------------|-------|-----|--------------|--------|-------|-----|-------|

| Symbol      | Min   | Max | Onits        | Symbol | Min   | Max | Units |

| tRC         | 70    | -   | ns           | toн    | 3     | -   | ns    |

| taa         | -     | 70  | ns           | tolz   | 5     | -   | ns    |

| tPC         | 25    | -   | ns           | tBLZ   | 5     | -   | ns    |

| <b>t</b> PA | -     | 20  | ns           | tLZ    | 10    | -   | ns    |

| tco         | -     | 70  | ns           | tснz   | 0     | 12  | ns    |

| tвА         | -     | 35  | ns           | tвнz   | 0     | 12  | ns    |

| tOE         | -     | 35  | ns           | tонz   | 0     | 12  | ns    |

## **ASYNCHRONOUS WRITE TIMING WAVEFORM**

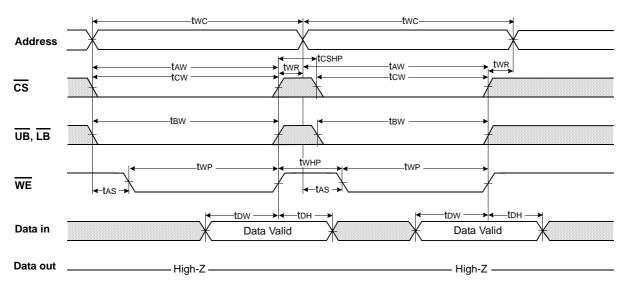

#### Fig.15 TIMING WAVEFORM OF WRITE CYCLE(1)( DE=VIH, WAIT=High-Z, WE Controlled)

(ASYNCHRONOUS WRITE CYCLE - WE Controlled)

1. A write occurs during the overlap(twP) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or LB for single byte operation or simultaneously asserting UB and LB for double byte operation. A write ends at the earliest transition when CS goes high or WE goes high. The twp is measured from the beginning of write to the end of write.

- 2. tow is measured from the CS going low to the end of write. 3. tas is measured from the address valid to the beginning of write.

- 4. two is measured from the end of write to the address change. two is applied in case a write ends with  $\overline{CS}$  or  $\overline{WE}$  going high. 5. In asynchronous write cycle, Clock,  $\overline{ADV}$  and  $\overline{WAIT}$  signals are ignored.

- 6. Condition for continuous write operation over 50 times : tWP(min)=70ns

### Table 19. ASYNCHRONOUS WRITE AC CHARACTERISTICS(WE Controlled)

| Symbol | Speed            |     | Units Symbol | Speed         |     | Units |       |

|--------|------------------|-----|--------------|---------------|-----|-------|-------|

| Cymbol | Min              | Max | onita        | Cymbol        | Min | Max   | onita |

| twc    | 70               | -   | ns           | tas           | 0   | -     | ns    |

| tcw    | 60               | -   | ns           | twR           | 0   | -     | ns    |

| taw    | 60               | -   | ns           | tow           | 30  | -     | ns    |

| tBW    | 60               | -   | ns           | tdн           | 0   | -     | ns    |

| tWP    | 55 <sup>1)</sup> | -   | ns           | <b>t</b> CSHP | 10  | -     | ns    |

1. tWP(min)=70ns for continuous write operation over 50 times.

## **ASYNCHRONOUS WRITE TIMING WAVEFORM**

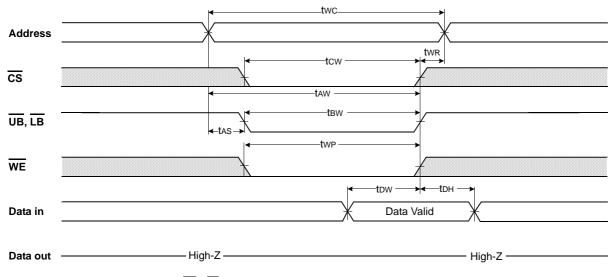

Fig.16 TIMING WAVEFORM OF WRITE CYCLE(2)( OE=VIH, WAIT=High-Z, UB & LB Controlled)

(ASYNCHRONOUS WRITE CYCLE - UB & LB Controlled)

1. A write occurs during the overlap(twp) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or LB for single byte operation or simultaneously asserting  $\overline{UB}$  and  $\overline{LB}$  for double byte operation. A write ends at the earliest transition when  $\overline{CS}$  goes high or  $\overline{WE}$  goes high. The twp is measured from the beginning of write to the end of write.

- 2. tcw is measured from the  $\overline{CS}$  going low to the end of write.

- 3. tas is measured from the address valid to the beginning of write.

4. twr is measured from the end of write to the address change. twr is applied in case a write ends with CS or WE going high.

5. In asynchronous write cycle, Clock, ADV and WAIT signals are ignored.

| Symbol | Speed            |     | Units | Symbol | Sp  | eed                | Units |

|--------|------------------|-----|-------|--------|-----|--------------------|-------|

| Symbol | Min              | Max | Units | Symbol | Min | Max<br>-<br>-<br>- | onno  |

| twc    | 70               | -   | ns    | tas    | 0   | -                  | ns    |

| tcw    | 60               | -   | ns    | twr    | 0   | -                  | ns    |

| taw    | 60               | -   | ns    | tDW    | 30  | -                  | ns    |

| tвw    | 60               | -   | ns    | tdн    | 0   | -                  | ns    |

| twp    | 55 <sup>1)</sup> | -   | ns    |        |     |                    |       |

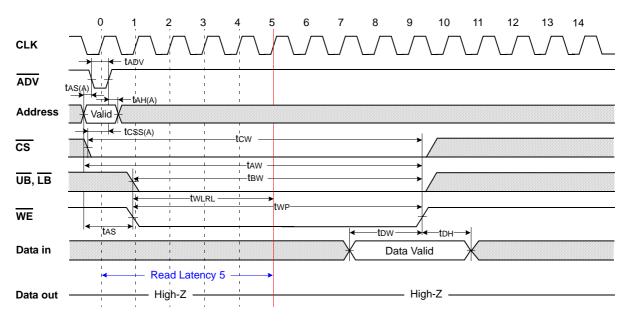

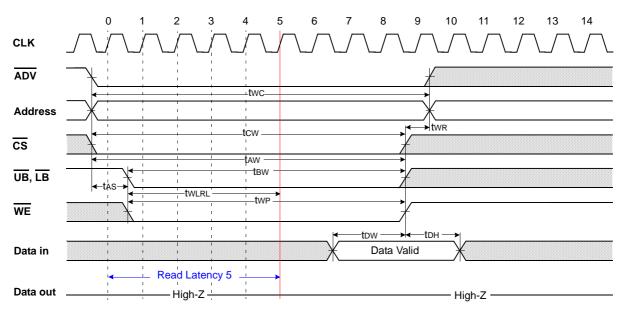

#### Fig.17 TIMING WAVEFORM OF WRITE CYCLE(Address Latch Type)( OE=VIH, WAIT=High-Z, WE Controlled)

(ADDRESS LATCH TYPE ASYNCHRONOUS WRITE CYCLE - WE Controlled)

1. A write occurs during the overlap(twP) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or LB for single byte operation or simultaneously asserting UB and LB for word operation. A write ends at the earliest transition when  $\overline{CS}$  goes high or  $\overline{WE}$  goes high. The twP is measured from the beginning of write to the end of write.

2. taw is measured from the address valid to the end of write. In this address latch type write timing, two is same as taw.

3. tcw is measured from the  $\overline{CS}$  going low to the end of write.

4. tBW is measured from the UB and LB going low to the end of write.

5. Clock input does not have any affect to the write operation if the parameter tWLRL is met.

#### Table 21. ASYNCH. WRITE IN SYNCH. MODE AC CHARACTERISTICS (Address Latch Type, WE Controlled)

| Symbol  | Speed |     | Units Symbol |        | Speed            |     | Units |

|---------|-------|-----|--------------|--------|------------------|-----|-------|

| Symbol  | Min   | Max | Units        | Symbol | Min              | Max | Units |

| tadv    | 7     | -   | ns           | tвw    | 60               | -   | ns    |

| tas(a)  | 0     | -   | ns           | twp    | 55 <sup>1)</sup> | -   | ns    |

| tah(a)  | 7     | -   | ns           | twlrl  | 1                | -   | clock |

| tCSS(A) | 10    | -   | ns           | tas    | 0                | -   | ns    |

| tcw     | 60    | -   | ns           | tDW    | 30               | -   | ns    |

| taw     | 60    | -   | ns           | tDH    | 0                | -   | ns    |

## **ASYNCHRONOUS WRITE TIMING WAVEFORM in SYNCHRONOUS MODE**

0 2 3 5 6 7 8 9 10 11 12 13 14 1 4 CLK ADV tas AH(A Address Valid tCSS(A) tcw cs -taw -tew UB, LB tAS -twi Ri -twp WE -tow -tDH Data in Data Valid **Read Latency 5** High-Z -Data out High-Z

Fig.18 TIMING WAVEFORM OF WRITE CYCLE(Address Latch Type)( DE=VIH, WAIT=High-Z, UB & LB Controlled)

(ADDRESS LATCH TYPE ASYNCHRONOUS WRITE CYCLE - UB & LB Controlled)

1. A write occurs during the overlap(twP) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or  $\overline{LB}$  for single byte operation or simultaneously asserting  $\overline{UB}$  and  $\overline{LB}$  for word operation. A write ends at the earliest transition when  $\overline{CS}$  goes or and  $\overline{WE}$  goes high. The twP is measured from the beginning of write to the end of write.

2. taw is measured from the address valid to the end of write. In this address latch type write timing, twc is same as taw.

3. tcw is measured from the  $\overline{CS}$  going low to the end of write.

4. tew is measured from the  $\overline{\text{UB}}$  and  $\overline{\text{LB}}$  going low to the end of write.

5. Clock input does not have any affect to the write operation if the parameter tWLRL is met.

## Table 22. ASYNCH. WRITE IN SYNCH. MODE AC CHARACTERISTICS(Address Latch Type, UB & LB Controlled)

| Symbol  | Speed |     | Units | Symbol | Speed            |     | Units |

|---------|-------|-----|-------|--------|------------------|-----|-------|

| Symbol  | Min   | Max | Units | Symbol | Min              | Max | Units |

| tadv    | 7     | -   | ns    | tвw    | 60               | -   | ns    |

| tas(a)  | 0     | -   | ns    | twp    | 55 <sup>1)</sup> | -   | ns    |

| tah(a)  | 7     | -   | ns    | twlrl  | 1                | -   | clock |

| tCSS(A) | 10    | -   | ns    | tas    | 0                | -   | ns    |

| tcw     | 60    | -   | ns    | tDW    | 30               | -   | ns    |

| taw     | 60    | -   | ns    | tDH    | 0                | -   | ns    |

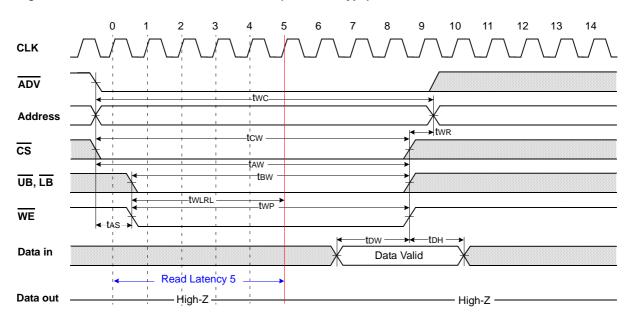

Fig.19 TIMING WAVEFORM OF WRITE CYCLE(Low ADV Type)( OE=VIH, WAIT=High-Z, WE Controlled)

(LOW ADV TYPE WRITE CYCLE - WE Controlled)

1. A write occurs during the overlap(twp) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or LB for single byte operation or simultaneously asserting  $\overline{UB}$  and  $\overline{LB}$  for double byte operation. A write ends at the earliest transition when  $\overline{CS}$  goes high or  $\overline{WE}$  goes high. The twp is measured from the beginning of write to the end of write.

2. tcw is measured from the  $\overline{CS}$  going low to the end of write.

3. tas is measured from the address valid to the beginning of write.

4. twr is measured from the end of write to the address change. twr is applied in case a write ends with CS or WE going high.

5. Clock input does not have any affect to the write operation if the parameter tWLRL is met.

#### Table 23. ASYNCH. WRITE IN SYNCH. MODE AC CHARACTERISTICS(Low ADV Type, WE Controlled)

| Symbol | Speed            |     | Units Symbol | Sp     | eed | Units |       |

|--------|------------------|-----|--------------|--------|-----|-------|-------|

| Symbol | Min              | Max | Units        | Symbol | Min | Max   | Onits |

| twc    | 70               | -   | ns           | twlrl  | 1   | -     | clock |

| tcw    | 60               | -   | ns           | tas    | 0   | -     | ns    |

| tAW    | 60               | -   | ns           | twR    | 0   | -     | ns    |

| tвw    | 60               | -   | ns           | tow    | 30  | -     | ns    |

| tWP    | 55 <sup>1)</sup> | -   | ns           | tDH    | 0   | -     | ns    |

Fig.20 TIMING WAVEFORM OF WRITE CYCLE(Low ADV Type)( DE=VIH, WAIT=High-Z, UB & LB Controlled)

(LOW ADV TYPE WRITE CYCLE - UB & LB Controlled)

1. A write occurs during the overlap(twe) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or LB for single byte operation or simultaneously asserting UB and LB for double byte operation. A write ends at the earliest transition when  $\overline{CS}$  goes high or  $\overline{WE}$  goes high. The twp is measured from the beginning of write to the end of write. 2. tcw is measured from the  $\overline{CS}$  going low to the end of write. 3. tas is measured from the address valid to the beginning of write.

4. twr is measured from the end of write to the address change. twr is applied in case a write ends with CS or WE going high.

5. Clock input does not have any affect to the write operation if the parameter tWLRL is met.

| Table 24. ASYNCH. WRITE IN SYNCH. MODE AC CHARACTERISTICS(Low ADV Type, UL | B & LB Controlled) |

|----------------------------------------------------------------------------|--------------------|

|----------------------------------------------------------------------------|--------------------|

| Symbol | Speed            |     | Units Symbol | Sp     | eed | Units |       |

|--------|------------------|-----|--------------|--------|-----|-------|-------|

| Symbol | Min              | Мах | Units        | Symbol | Min | Max   | Onits |

| twc    | 70               | -   | ns           | twlrl  | 1   | -     | clock |

| tcw    | 60               | -   | ns           | tas    | 0   | -     | ns    |

| taw    | 60               | -   | ns           | twR    | 0   | -     | ns    |

| tBW    | 60               | -   | ns           | tDW    | 30  | -     | ns    |

| tWP    | 55 <sup>1)</sup> | -   | ns           | tDH    | 0   | -     | ns    |

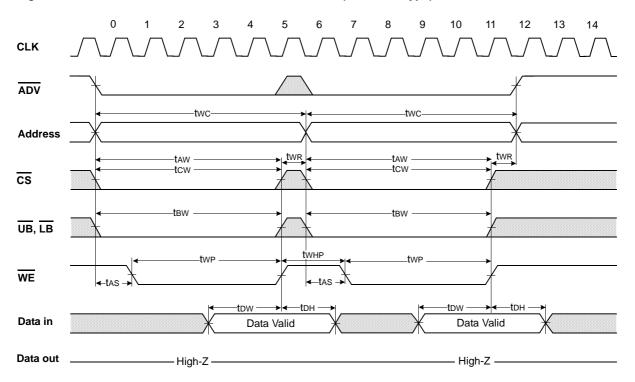

Fig.21 TIMING WAVEFORM OF MULTIPLE WRITE CYCLE(Low ADV Type)( DE=VIH, WAIT=High-Z, WE Controlled)

(LOW ADV TYPE MULTIPLE WRITE CYCLE)

1. A write occurs during the overlap(twP) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or LB for single byte operation or simultaneously asserting  $\overline{UB}$  and  $\overline{LB}$  for double byte operation. A write ends at the earliest transition when  $\overline{CS}$  goes high or  $\overline{WE}$  goes high. The twP is measured from the beginning of write to the end of write.

2. tcw is measured from the  $\overline{CS}$  going low to the end of write.

3. tas is measured from the address valid to the beginning of write.

4. twr is measured from the end of write to the address change. twr is applied in case a write ends with  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going high.

5. Clock input does not have any affect to the asynchronous multiple write operation if twHP is shorter than (Read Latency - 1) clock duration.

6. tWP(min)=70ns for continuous write operation over 50 times.

| Symbol | Sp               | Speed |       | Units Symbol | Sp  | Units           |       |

|--------|------------------|-------|-------|--------------|-----|-----------------|-------|

| Symbol | Min              | Мах   | onito | Symbol       | Min | Max             | Units |

| twc    | 70               | -     | ns    | twhp         | 5ns | Latency-1 clock | -     |

| tcw    | 60               | -     | ns    | tas          | 0   | -               | ns    |

| taw    | 60               | -     | ns    | twR          | 0   | -               | ns    |

| tBW    | 60               | -     | ns    | tow          | 30  | -               | ns    |

| tWP    | 55 <sup>1)</sup> | -     | ns    | tDH          | 0   | -               | ns    |

## Table 25. ASYNCH. WRITE IN SYNCH. MODE AC CHARACTERISTICS(Low ADV Type Multiple Write, WE Controlled)

## AC OPERATING CONDITIONS

**TEST CONDITIONS**(Test Load and Test Input/Output Reference) Input pulse level: 0.2 to Vcc-0.2V Input rising and falling time: 3ns Input and output reference voltage: 0.5 x Vcc Output load: CL=30pF

# Table 26. SYNCHRONOUS AC CHARACTERISTICS (Vcc=1.7~2.0V, TA=-40 to 85 °C, Maximum Main Clock Frequency=66MHz)

|                    | Parameter List                            | Symbol         | Sp  | eed  | Units |

|--------------------|-------------------------------------------|----------------|-----|------|-------|

|                    | Parameter List                            | Symbol         | Min | Max  | Units |

|                    | Clock Cycle Time                          | Т              | 15  | 200  | ns    |

|                    | Burst Cycle Time                          | tBC            | -   | 2500 | ns    |

|                    | Address Set-up Time to ADV Falling(Burst) | tas(b)         | 0   | -    | ns    |

|                    | Address Hold Time from ADV Rising(Burst)  | tAH(B)         | 7   | -    | ns    |

|                    | ADV Setup Time                            | tadvs          | 5   | -    | ns    |

|                    | ADV Hold Time                             | <b>t</b> advh  | 7   | -    | ns    |

| _                  | CS Setup Time to Clock Rising(Burst)      | tCSS(B)        | 5   | -    | ns    |

| Burst<br>Operation | Burst End to New ADV Falling              | <b>t</b> BEADV | 7   | -    | ns    |

| (Common)           | Burst Stop to New ADV Falling             | <b>t</b> BSADV | 12  | -    | ns    |

| . ,                | CS Low Hold Time from Clock               | <b>t</b> CSLH  | 7   | -    | ns    |

|                    | CS High Pulse Width                       | <b>t</b> CSHP  | 5   | -    | ns    |

|                    | ADV High Pulse Width                      | <b>t</b> ADHP  | 5   | -    | ns    |

|                    | Chip Select to WAIT Low                   | tw∟            | -   | 10   | ns    |

|                    | ADV Falling to WAIT Low                   | tawl           | -   | 10   | ns    |

|                    | Clock to WAIT High                        | twн            | -   | 12   | ns    |

|                    | Chip De-select to WAIT High-Z             | twz            | -   | 12   | ns    |

|                    | UB, LB Enable to End of Latency Clock     | <b>t</b> BEL   | 1   | -    | Clock |

|                    | Output Enable to End of Latency Clock     | tOEL           | 1   | -    | Clock |

|                    | UB, LB Valid to Low-Z Output              | tBLZ           | 5   | -    | ns    |

|                    | Output Enable to Low-Z Output             | toLz           | 5   | -    | ns    |

| Burst Read         | Latency Clock Rising Edge to Data Output  | tCD            | -   | 10   | ns    |

| Operation          | Output Hold                               | tон            | 3   | -    | ns    |

|                    | Burst End Clock to Output High-Z          | tHZ            | -   | 12   | ns    |

|                    | Chip De-select to Output High-Z           | tCHZ           | -   | 12   | ns    |

|                    | Output Disable to Output High-Z           | tонz           | -   | 12   | ns    |

|                    | UB, LB Disable to Output High-Z           | tвнz           | -   | 12   | ns    |

|                    | WE Set-up Time to Command Clock           | twes           | 5   | -    | ns    |

|                    | WE Hold Time from Command Clock           | twen           | 5   | -    | ns    |

|                    | WE High Pulse Width                       | twhp           | 5   | -    | ns    |

| Burst Write        | UB, LB Set-up Time to Clock               | tBS            | 5   | -    | ns    |

| Operation          | UB, LB Hold Time from Clock               | tвн            | 5   | -    | ns    |

|                    | Byte Masking Set-up Time to Clock         | tBMS           | 7   | -    | ns    |

|                    | Byte Masking Hold Time from Clock         | tвмн           | 7   | -    | ns    |

|                    | Data Set-up Time to Clock                 | tDS            | 5   | -    | ns    |

|                    | Data Hold Time from Clock                 | <b>t</b> DHC   | 3   | -    | ns    |

## U*t*RAM

## SYNCHRONOUS BURST OPERATION TIMING WAVEFORM

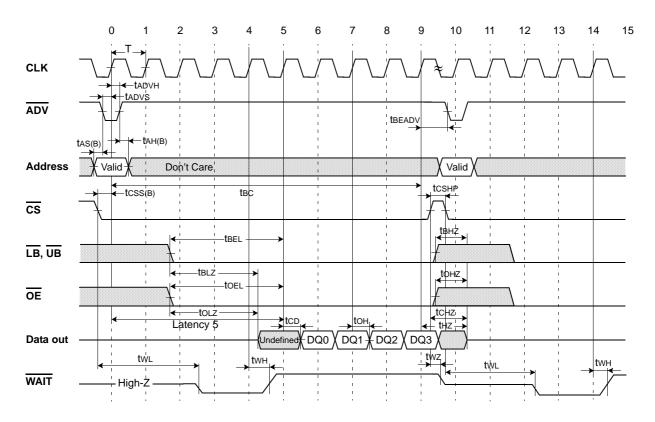

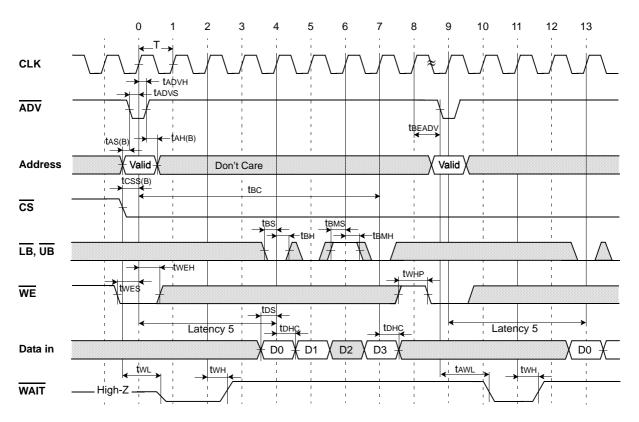

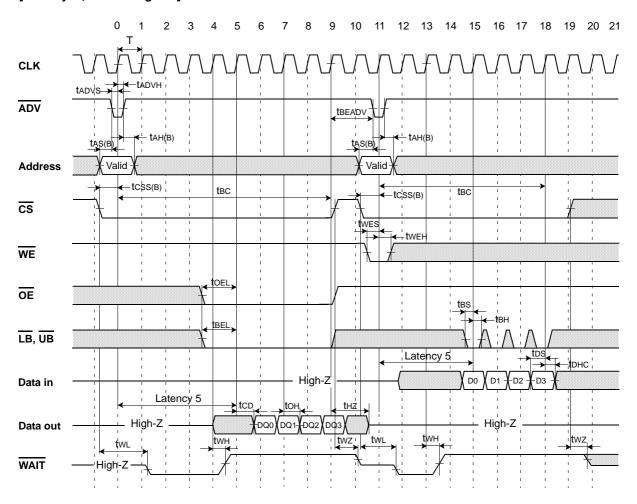

### Fig.23 TIMING WAVEFORM OF BASIC BURST OPERATION [Latency=5,Burst Length=4]

| Symbol        | Sp  | eed  | Units | Symbol         | Sp  | eed | Units |

|---------------|-----|------|-------|----------------|-----|-----|-------|

| Symbol        | Min | Max  | Units | Symbol         | Min | Мах | Units |

| т             | 15  | 200  | ns    | tAS(B)         | 0   | -   | ns    |

| tвс           | -   | 2500 | ns    | tAH(B)         | 7   | -   | ns    |

| tadvs         | 5   | -    | ns    | tCSS(B)        | 5   | -   | ns    |

| <b>t</b> ADVH | 7   | -    | ns    | <b>t</b> BEADV | 7   | -   | ns    |

### SYNCHRONOUS BURST READ TIMING WAVEFORM

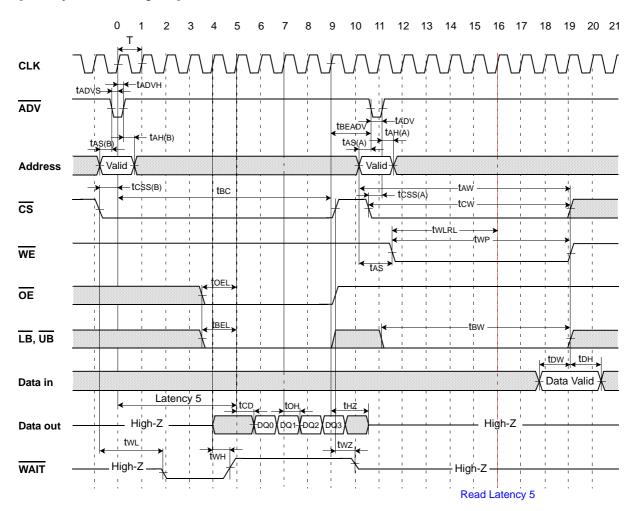

#### Fig.24 TIMING WAVEFORM OF BURST READ CYCLE(1) [Latency=5,Burst Length=4,WP=Low enable](WE=VIH) - CS Toggling Consecutive Burst Read

(SYNCHRONOUS BURST READ CYCLE - CS Toggling Consecutive Burst Read)

1. The new burst operation can be issued only after the previous burst operation is finished. For the new burst operation, tBEADV should be met.

2. /WAIT Low(tWL or tAWL) : Data not available(driven by CS low going edge or ADV low going edge) WAIT High(tWH): Data available(driven by Latency-1 clock)

WAIT High(tWH): Data available(driven by Latency-1 clock)

WAIT High-Z(tWZ): Data don't care(driven by CS high going edge)

Multiple clock risings are allowed during low ADV period. The burst operation starts from the first clock rising.

4. Burst Cycle Time(tBC) should not be over  $2.5\mu s$ .

### Table 28. BURST READ AC CHARACTERISTICS(CS Toggling Consecutive Burst)

| Symbol        | Sp  | eed | Units | Symbol | Sp  | eed | Units |

|---------------|-----|-----|-------|--------|-----|-----|-------|

| Cymbol        | Min | Max | onits | Cymbol | Min | Max | Onits |

| <b>t</b> CSHP | 5   | -   | ns    | tонz   | -   | 12  | ns    |

| <b>t</b> BEL  | 1   | -   | clock | tвнz   | -   | 12  | ns    |

| tOEL          | 1   | -   | clock | tCD    | -   | 10  | ns    |

| <b>t</b> BLZ  | 5   | -   | ns    | toн    | 3   | -   | ns    |

| tolz          | 5   | -   | ns    | twL    | -   | 10  | ns    |

| tHZ           | -   | 12  | ns    | twн    | -   | 12  | ns    |

| tснz          | -   | 12  | ns    | twz    | -   | 12  | ns    |

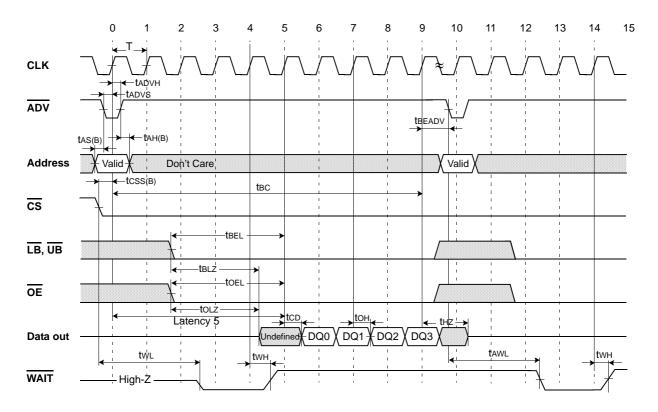

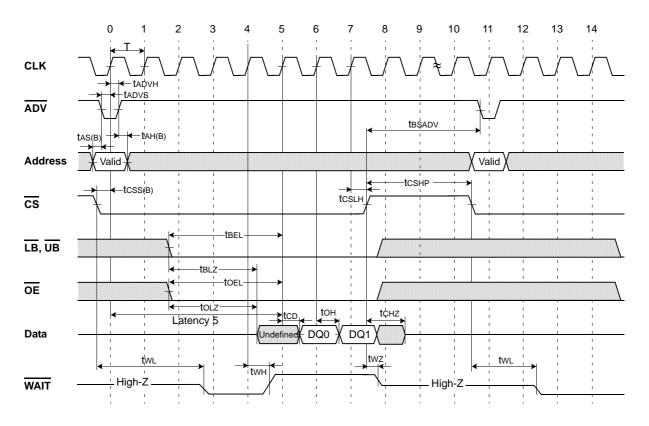

### SYNCHRONOUS BURST READ TIMING WAVEFORM

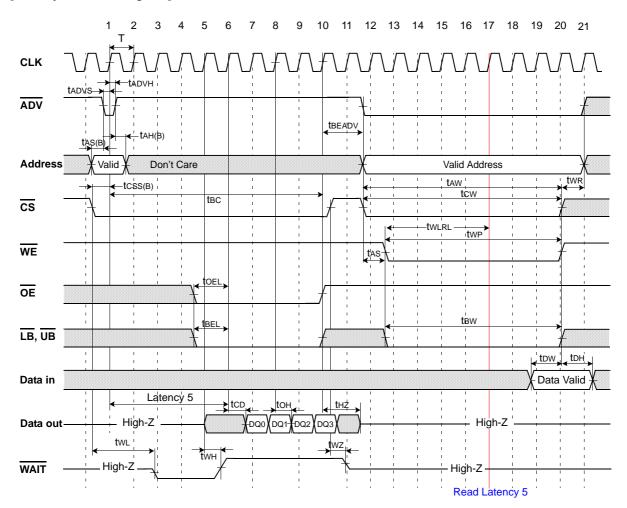

#### Fig.25 TIMING WAVEFORM OF BURST READ CYCLE(2) [Latency=5,Burst Length=4,WP=Low enable](WE=VIH) - CS Low Holding Consecutive Burst Read

(SYNCHRONOUS BURST READ CYCLE - CS Low Holding Consecutive Burst Read)

- 1. The new burst operation can be issued only after the previous burst operation is finished. For the new burst operation, tBEADV should be met.

- 2. *I*/WAIT Low(tWL or tAWL) : Data not available(driven by  $\overline{CS}$  low going edge or  $\overline{ADV}$  low going edge)

- WAIT Low(IVE of IAWE): Data hot available(driven by CS low going edge of ADV low going edge) /WAIT High(tWH): Data available(driven by Latency-1 clock) /WAIT High-Z(tWZ): Data don't care(driven by CS high going edge)

Multiple clock risings are allowed during low ADV period. The burst operation starts from the first clock rising.

The consecutive multiple burst read operation with holding CS low is possible through issuing only new ADV and address.

5. Burst Cycle Time(tBC) should not be over 2.5  $\mu s.$

#### Table 29. BURST READ AC CHARACTERISTICS (CS Low Holding Consecutive Burst)

| Symbol | Sp  | eed | Units | Symbol | Spe | eed | Units |

|--------|-----|-----|-------|--------|-----|-----|-------|

| Cymbol | Min | Max | onita | Oymbol | Min | Max | Onits |

| tBEL   | 1   | -   | clock | tCD    | -   | 10  | ns    |

| tOEL   | 1   | -   | clock | toн    | 3   | -   | ns    |

| tBLZ   | 5   | -   | ns    | tw∟    | -   | 10  | ns    |

| toLz   | 5   | -   | ns    | tawl   | -   | 10  | ns    |

| tHZ    | -   | 12  | ns    | twн    | -   | 12  | ns    |

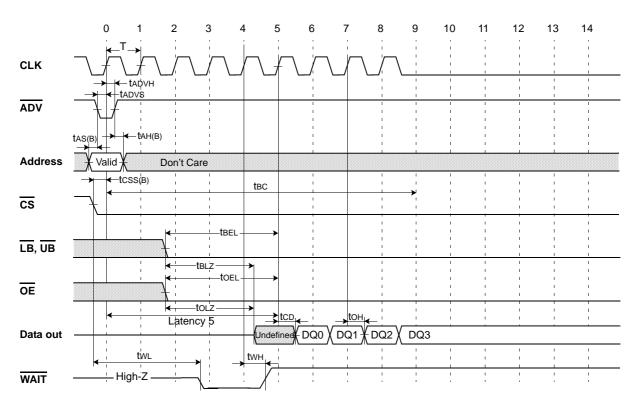

## SYNCHRONOUS BURST READ TIMING WAVEFORM

#### Fig.26 TIMING WAVEFORM OF BURST READ CYCLE(3) [Latency=5,Burst Length=4,WP=Low enable](WE=VH) - Last Data Sustaining

(SYNCHRONOUS BURST READ CYCLE - Last Data Sustaining)

WAIT Low(tWL or tAWL): Data not available(driven by CS low going edge or ADV low going edge) /WAIT High(tWH): Data available(driven by Latency-1 clock) /WAIT High-Z(tWZ): Data don't care(driven by CS high going edge)

Multiple clock risings are allowed during low ADV period. The burst operation starts from the first clock rising.

3. Burst Cycle Time(tBC) should not be over 2.5µs.

### Table 30. BURST READ AC CHARACTERISTICS(Last Data Sustaining)

| Symbol | Sp  | eed | Units | Symbol | Sp  | eed | Units |

|--------|-----|-----|-------|--------|-----|-----|-------|

| Symbol | Min | Max | Units | Symbol | Min | Max | Units |

| tBEL   | 1   | -   | clock | tCD    | -   | 10  | ns    |

| tOEL   | 1   | -   | clock | toн    | 3   | -   | ns    |

| tBLZ   | 5   | -   | ns    | twL    | -   | 10  | ns    |

| toLz   | 5   | -   | ns    | twн    | -   | 12  | ns    |

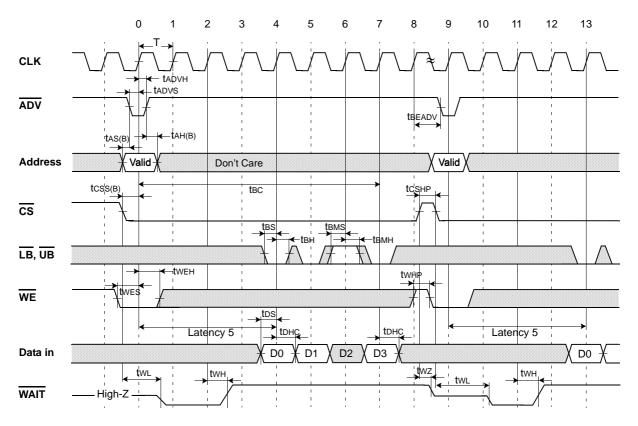

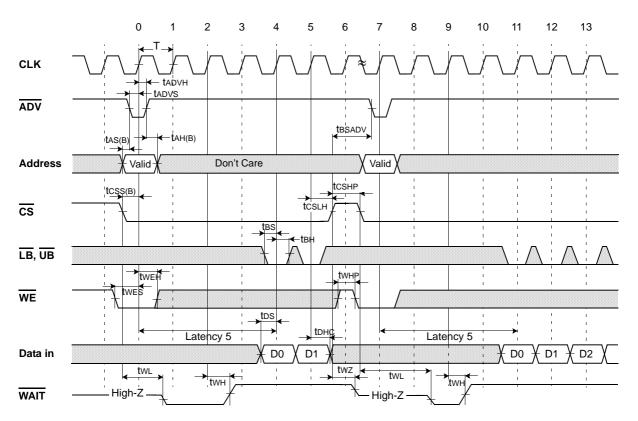

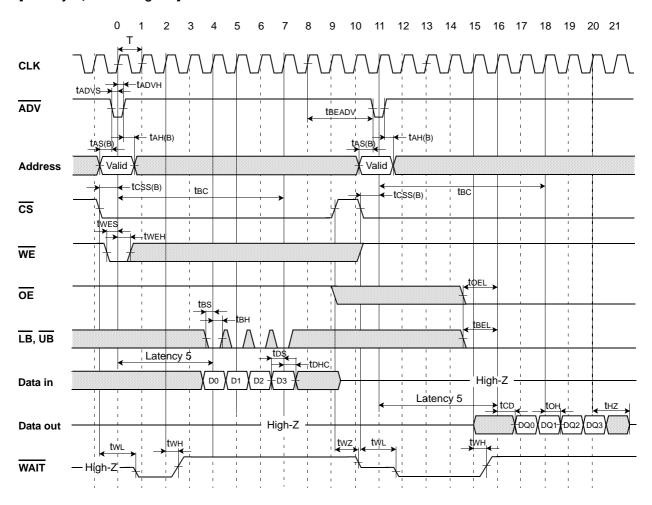

## SYNCHRONOUS BURST WRITE TIMING WAVEFORM

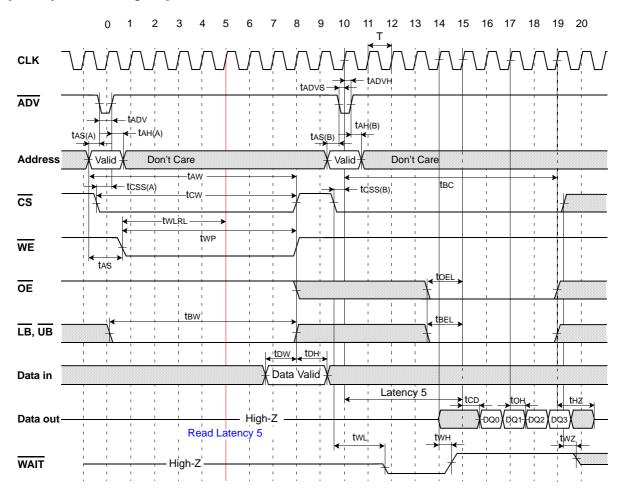

Fig.27 TIMING WAVEFORM OF BURST WRITE CYCLE(1) [Latency=5,Burst Length=4,WP=Low enable](OE=VIH) - CS Toggling Consecutive Burst Write

- (SYNCHRONOUS BURST WRITE CYCLE CS Toggling Consecutive Burst Write)

- 1. The new burst operation can be issued only after the previous burst operation is finished. For the new burst operation, tBEADV

- should be met.

- Should be met.

Multiple clock risings are allowed during low ADV period. The burst operation starts from the first clock rising.

/WAIT Low(tWL or tAWL) : Data not available(driven by CS low going edge or ADV low going edge)

/WAIT High(tWH) : Data available(driven by Latency-1 clock)

/WAIT High-Z(tWZ) : Data don't care(driven by CS high going edge)

D2 is masked by UB and LB.

Paysed by UB and LB.

- 5. Burst Cycle Time(tBC) should not be over  $2.5\mu s$ .

| Symbol        | Sp  | eed | Units | Symbol       | Spo | eed | Units |

|---------------|-----|-----|-------|--------------|-----|-----|-------|

| Cymbol        | Min | Мах | onno  | Cymbol       | Min | Max | onno  |

| <b>t</b> CSHP | 5   | -   | ns    | twhp         | 5   | -   | ns    |

| tBS           | 5   | -   | ns    | tDS          | 5   | -   | ns    |

| tвн           | 5   | -   | ns    | <b>t</b> DHC | 3   | -   | ns    |

| tBMS          | 7   | -   | ns    | twL          | -   | 10  | ns    |

| tвмн          | 7   | -   | ns    | twн          | -   | 12  | ns    |

| twes          | 5   | -   | ns    | twz          | -   | 12  | ns    |

| tweн          | 5   | -   | ns    |              |     |     |       |

Table 31. BURST WRITE AC CHARACTERISTICS (CS Toggling Consecutive Burst)

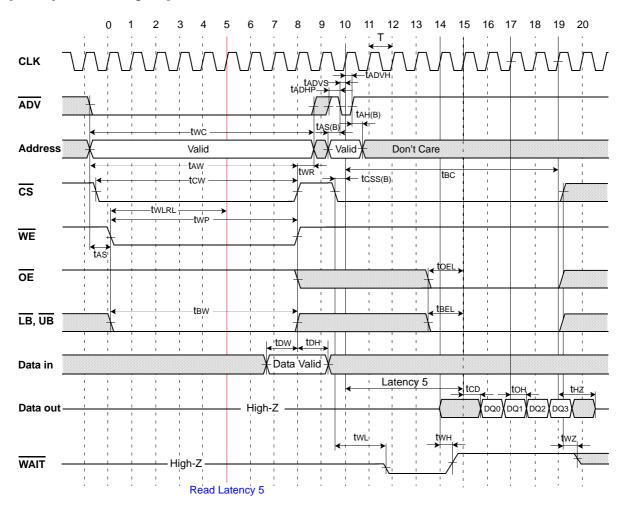

### SYNCHRONOUS BURST WRITE TIMING WAVEFORM

<sup>(</sup>SYNCHRONOUS BURST WRITE CYCLE - CS Low Holding Consecutive Burst Write)

- 1. The new burst operation can be issued only after the previous burst operation is finished. For the new burst operation, tBEADV should be met.

- snould be met.

2. Multiple clock risings are allowed during low ADV period. The burst operation starts from the first clock rising.

3. /WAIT Low(tWL or tAWL) : Data not available(driven by CS low going edge or ADV low going edge)

/WAIT High(tWH) : Data available(driven by Latency-1 clock)

/WAIT High-Z(tWZ) : Data don't care(driven by CS high going edge)

4. D2 is masked by UB and LB.

- 5. The consecutive multiple burst read operation with holding CS low is possible through issuing only new ADV and address.

- 6. Burst Cycle Time(tBC) should not be over 2.5µs.

Table 32. BURST WRITE AC CHARACTERISTICS (CS Low Holding Consecutive Burst)

| Symbol | Sp  | eed | Units | Symbol       | Sp  | eed | Units |

|--------|-----|-----|-------|--------------|-----|-----|-------|

| Gymbol | Min | Max | onits | Cymbol       | Min | Max | onits |

| tBS    | 5   | -   | ns    | twhp         | 5   | -   | ns    |

| tвн    | 5   | -   | ns    | tDS          | 5   | -   | ns    |

| tBMS   | 7   | -   | ns    | <b>t</b> DHC | 3   | -   | ns    |

| tвмн   | 7   | -   | ns    | tw∟          | -   | 10  | ns    |

| twes   | 5   | -   | ns    | tawl         | -   | 10  | ns    |

| tweн   | 5   | -   | ns    | twн          | -   | 12  | ns    |

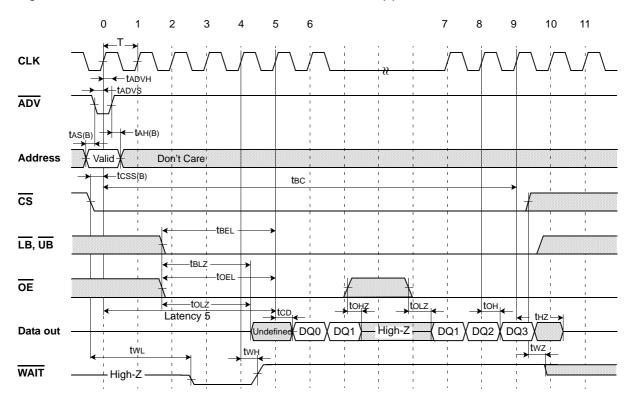

### SYNCHRONOUS BURST READ STOP TIMING WAVEFORM

## Fig.29 TIMING WAVEFORM OF BURST READ STOP by CS [Latency=5,Burst Length=4,WP=Low enable](WE=VIH)

(SYNCHRONOUS BURST READ STOP TIMING)

- 1. The new burst operation can be issued only after the previous burst operation is finished. For the new burst operation, tBSADV

- WAIT Low(tWL or tAWL) : Data not available(driven by CS low going edge or ADV low going edge) /WAIT High(tWH) : Data available(driven by Latency-1 clock) /WAIT High-Z(tWZ) : Data don't care(driven by CS high going edge)

Multiple clock risings are allowed during low ADV period. The burst operation starts from the first clock rising.

- 4. The burst stop operation should not be repeated for over  $2.5\mu$ s.

### Table 33. BURST READ STOP AC CHARACTERISTICS

| Symbol         | Sp  | eed | Units | Symbol | Sp  | eed | Units |

|----------------|-----|-----|-------|--------|-----|-----|-------|

| Cymbol         | Min | Max | onita | Cymbol | Min | Max | onna  |

| <b>t</b> BSADV | 12  | -   | ns    | tCD    | -   | 10  | ns    |

| tCSLH          | 7   | -   | ns    | toн    | 3   | -   | ns    |

| tCSHP          | 5   | -   | ns    | tснz   | -   | 12  | ns    |

| <b>t</b> BEL   | 1   | -   | clock | twL    | -   | 10  | ns    |

| tOEL           | 1   | -   | clock | twн    | -   | 12  | ns    |

| <b>t</b> BLZ   | 5   | -   | ns    | twz    | -   | 12  | ns    |