## YAMAHA L 5 I

# **YTZ420**

## **FCC**

**Fieldbus Communication Contoroller LSI**

- YAMAHA CORPORATION

YTZ420 CATALOG CATALOG No.: LSI-4TZ420A6 2008.10

## **General Description**

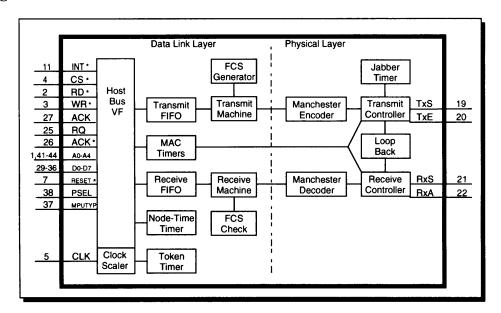

YTZ420 is a communication controller intended for use in a node of fieldbus operating per International standard, IEC 1158. YTZ420 is based on a latest sub micron CMOS technology. Its provides 100% compatible Physical Layer functionality to IEC 1158-2, and ISA S50.2. Lower part of Data Link Layer is also implemented to conform IEC Committee Draft SC65C(Secretariat) 106. See Figure 1 for block diagram. A low power consumption feature of YTZ420 is an ideal solution for Intrinsic-Safety (I.S.) devices. YTZ420 shall be used in cooperation with a microcontroller / microprocessor that serves for higher part of communication protocol.

#### **Features**

#### General

- Small Package: 44 pin plastic LQFP or QFP

- Low Power consumption: less than 3mW

- Wide supply voltage range: 3~5V

- Flexible 8 bit parallel interface directly connectable to both Intel and Motorola type microcontrollers

- Two-mode DMA interface to reduce interrupts

- Programmable prescaler to allow 0.5, 1, 2, 4, 8, and 16MHz clock input

#### **Physical Layer**

- 100% compatible to IEC 1158-2

- Data rate: 31.25kbps and 1Mbps

- Manchester encoder/decoder

- Two useful signal driving methods including standard MDA-MAU interface

- Automatic correction of signal polarity

- Addition and deletion of preamble, start- and stop-delimiters

- Internal Jabber timer (4096 bit time)

- Internal and external loop back capability for self diagnostics

#### **Data Link Layer**

- Automatic calculation of 16 bit FCS

- Internal data buffers to reduce microcontroller overhead (32 stage transmit-FIFO and 32 stage receive FIFO)

- DL-timer (NODE time and Token hold time)

- Timers for time-dependent operation

## **Applications**

- Distributed Control System

- Single Loop Controller

- Temperature Controller

- Field transmitter

- Field actuator

## **Block Diagram**

Figure 1 Block Diagram of YTZ420

## **Absolute Maximum Ratings**

| Description           | Symbol          | Min     | Max                  | Unit            | Condition      |

|-----------------------|-----------------|---------|----------------------|-----------------|----------------|

| Supply Voltage        | V <sub>DD</sub> | Vss-0.5 | Vss+7.0              | V               |                |

| Input Voltage         | Vı              | Vss-0.5 | V <sub>DD</sub> +0.5 | V               |                |

| Output Voltage        | Vo              | Vss-0.5 | V <sub>DD</sub> +0.5 | V               |                |

| Operating Temperature | Topr            | -40     | 85                   | ${\mathfrak C}$ |                |

| Storage Temperature   | Tstg            | -40     | +125                 | ${\mathbb C}$   |                |

| Input HIGH Current    | Іон             | -       | +20                  | mA              | $V_0 = V_{DD}$ |

| Input LOW Current     | Iol             | -20     | -                    | mA              | Vo = 0V        |

| Power Dissipation     | PD              | 0       | 100                  | mW              |                |

## **Recommended Operating Condition**

| Description         | Symbol          | Min | Max | Unit          | Condition     |

|---------------------|-----------------|-----|-----|---------------|---------------|

| Supply Voltage      | V <sub>DD</sub> | 2.7 | 5.5 | V             |               |

| Ambient Temperature | TA              | 0   | 70  | ${\mathbb C}$ |               |

| Clock Frequency     | FCLK            | 0.5 | 4   | MHz           | $V_{DD} = 3V$ |

|                     |                 | 0.5 | 16  | 1             | $V_{DD} = 5V$ |

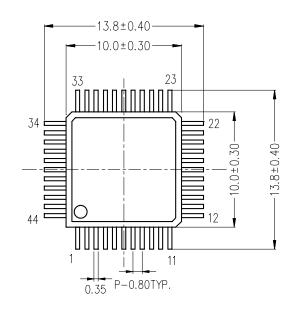

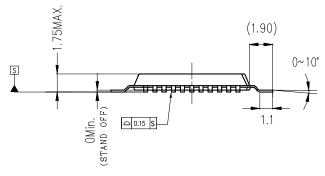

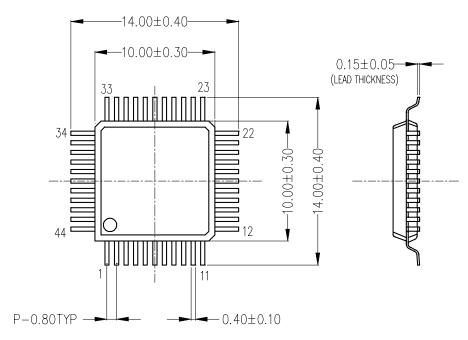

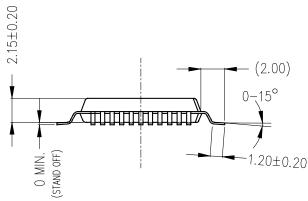

## **Package**

YTZ420 is packaged in a plastic surface-mount flat package (LQFP) of 44 pins to occupy minimum space in your electronicsciruit bodrd. Figure 2 shows the package dimension.

- Lead-free plating LQFP44 (YTZ420-VZ); in production

- Lead-free plating QFP44 (YTZ420-FZ); discontinued

#### How it works

YTZ420 transmits data blocks of assigned length stored in the transmit FIFO buffer by adding preamble, start-delimiter, frame check sequence (FCS) and end delimiter. It also observes input signal to find preamble for bit synchronization and start-delimiter for octet synchronization. It stores received data into the receive FIFO buffer by deleting preamble, delimiters and FCS. A DMA interface capability does them without making interrupt to the microcontroller.

YTZ420 evaluates validity of received frames by delimiters and FCS to generate an interrupt when an error is detected.

| Preamble | Start | Data   | FCS       | End |  |

|----------|-------|--------|-----------|-----|--|

| Transmit |       | A V    | Receive   |     |  |

|          |       | FIFO   |           |     |  |

| DMA      |       | ΑŢ     | Interrupt |     |  |

|          |       | Memory |           |     |  |

YTZ420 also provides various timers for time-critical part of Data Link Layer. They are NODE Time timer, Remaining timer for token holding time, timer to guarantee minimum time period between data frame and timer to detect inactivity of the fieldbus.

## **Chip Specification**

## Pin Configuration

| Pin | Signal Name     |

|-----|-------------|-----|-------------|-----|-------------|-----|-----------------|

| 1   | A4          | 12  | MO0         | 23  | TST0        | 34  | D5              |

| 2   | RD*/E       | 13  | MO1         | 24  | TST1        | 35  | · D6            |

| 3   | WR*/RW      | 14  | MO2         | 25  | RQ          | 36  | D7              |

| 4   | CS*         | 15  | MO3         | 26  | ACK*        | 37  | MPUTYP          |

| 5   | CLK         | 16  | MO4         | 27  | RDY         | 38  | PSEL            |

| 6   | VSS         | 17  | $V_{DD}$    | 28  | Vss         | 39  | V <sub>DD</sub> |

| 7   | RESET*      | 18  | Vss         | 29  | D0          | 40  | Vss             |

| 8   | MS0         | 19  | TxS         | 30  | D1          | 41  | <b>A</b> 0      |

| 9   | MS1         | 20  | TxE*/ADD    | 31  | D2          | 42  | Al              |

| 10  | MS2         | 21  | RxS         | 32  | D3          | 43  | A2              |

| 11  | INT*        | 22  | RxA         | 33  | D4          | 44  | A3              |

Asterisk (\*) indicates negative (LOW active) signal

## **Signal Description**

| Signal    | Pins             | I/O | Description                                                                                                                                                                                           |

|-----------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDD       | 17, 39           | -   | Power supply. 3~5V DC (5%) is expected.                                                                                                                                                               |

| VSS       | 6, 18,<br>28, 40 | -   | Ground level                                                                                                                                                                                          |

| RESET*    | 7                | I   | Reset input. LOW input at this pin and at least four (4) cycle of CLK input are required to reset YTZ420.                                                                                             |

| CLK       | 5                | I   | Clock input. Frequency is expected as one from 1, 2, 4 and 8MHz.                                                                                                                                      |

| CS*       | 4                | I   | Chip Select. A LOW input to this pin enables bus access to YTZ420.                                                                                                                                    |

| A0-A4     | 1, 42-44         | I   | Address input from host processor.                                                                                                                                                                    |

| D0-D7     | 29-36            | ľO  | Data bus for host processor. These pins are initialized to high impedance by reset.                                                                                                                   |

| MPUTYP    | 37               | I   | Selects bus operation type:  Low: Intel type 8 bit bus  HIGH: Motorola type 8 bit bus                                                                                                                 |

| PSEL      | 38               | I   | Selects bus access protocol:  LOW: asynchronous bus cycle to use RDY signal HIGH: RDY signal is not used.                                                                                             |

| RD*/E     | 2                | I   | Read strobe (RD*) in Intel mode (MPUTYP = LOW) Enable (E) in Motorola mode (MPUTYP = HIGH)                                                                                                            |

| WR*/RW    | 3                | I   | Write strobe (WR*) in Intel mode (MPUTYP = LOW) Read/Write select (R/W*) in Motorola mode (MPUTYP = HIGH)                                                                                             |

| RDY       | 27               | 0   | Access ready signal to host processor. This signal is available only when PSEL = LOW. This signal is always HIGH when PSEL = HIGH. This signal is initialized to HIGH by reset.                       |

| INT*      | 11               | 0   | Interrupt to host processor. This signal is initialized to HIGH by reset.                                                                                                                             |

| RQ        | 25               | 0   | Data transfer request to DMA controller.                                                                                                                                                              |

| ACK*      | 26               | I   | Data transfer acknowledge from DMA controller.                                                                                                                                                        |

| TxS       | 19               | 0   | Transmit signal to medium attachment unit. This signal is a Manches ter-encoded and initialized to LOW by reset. This signal stays LOW when YTZ420 is not transmitting or in internal loop back mode. |

| TxE*/ADD  | 20               | 0   | Transmit control to medium attachment unit.                                                                                                                                                           |

| RxS       | 21               | I   | Receive Signal from medium attachment unit                                                                                                                                                            |

| RxA       | 22               | I   | Receive activity (carrier detect) from medium attachment unit                                                                                                                                         |

| TST0-TST1 | 23-24            | I   | Input for chip test. These pins should be connected to Vss in normal operation.                                                                                                                       |

| MS0-MS2   | 8-10             | I   | Input for chip test. These pins should be connected to Vss in normal operation.                                                                                                                       |

| MO0-MO4   | 12-16            | О   | Output for chip test. These pin should be kept open in normal operation.                                                                                                                              |

Note: Since INT\*, RDY and RQ outputs are not "open-drain" type, you are not able to make wired-or with other signals.

## **DC Characteristics**

| Description         | Symbol | Min                  | Max     | Unit | Condition                                |

|---------------------|--------|----------------------|---------|------|------------------------------------------|

| High Input Voltage  | Vih    | 2.2                  | -       | V    | $V_{DD} = 3.0V \pm 10\%$                 |

|                     |        | 3.5                  | -       |      | $V_{DD} = 5.0V \pm 10\%$                 |

| LOW Input Voltage   | VIL    | -                    | 0.5     | V    | $V_{DD} = 3.0V \pm 10\%$                 |

|                     |        | -                    | 1.0     |      | $V_{DD} = 5.0V \pm 10\%$                 |

| High Output Voltage | Vон    | VDD-0.6              | -       | V    | $V_{DD} = 3.0V$ ,                        |

|                     |        |                      |         |      | Iон = -1mA                               |

|                     | 1      | V <sub>DD</sub> -1.0 | -       |      | $V_{DD} = 5.0V$ ,                        |

|                     |        |                      |         |      | Iон = -2mA                               |

| Low Output Voltage  | Vol    |                      | Vss+0.4 | V    | $V_{DD} = 3.0V$ , $I_{OL} = 1 \text{mA}$ |

|                     |        |                      | Vss+0.4 |      | $V_{DD} = 5.0V$ , $I_{OL} = 2mA$         |

| Supply Current      | Icc    | -                    | 0.2     | mA   | Static Operation *                       |

| Input Capacitance   | Cin    | -                    | 8       | pF   | Ta=25C, Fclk=1MHz                        |

| Output Capacitance  | Cout   | -                    | 10      | pF   | $V_{DD} = VI = 0V$                       |

| I/O pin capacitance | Сю     | -                    | 12      | pF   |                                          |

## \* Static Operation:

FCLK = 1MHz; VDD = 5.0V; D0-D7 = VDD, RxS = RxA = TST0-TST1 = MS0-MS2 = Vss; RESET\* = VDD; Other inputs = VDD; all outputs are open.

AC Characteristics  $3V \pm 10\%$  operation

| Description             | Symbol      | Min      | Max          | Unit | Condition                            |

|-------------------------|-------------|----------|--------------|------|--------------------------------------|

|                         |             | 0.50±    | 0.1%         |      | PRD <b>♦</b> = 1 <sub>B</sub>        |

| Clock frequency         | Fclk        | 1.0±0.1% |              | MHz  | CLOCK ♥ = 00B                        |

|                         |             | 2.0±0.1% |              |      | CLOCK ♥ = 01B                        |

|                         |             | 4.0±     | 0.1%         |      | CLOCK <sup>♦</sup> = 10 <sub>B</sub> |

| CLK pulse width (LOW)   | tpwl        | 100      | -            | ns   |                                      |

| CLK pulse width (HIGH)  | tpwh        | 100      | -            | ns   |                                      |

| RESET* pulse width      | trst        | 4        | -            | tcyc | stays in LOW                         |

| Bit time of RxS         | tbT         | 32±      | 0.9          | μs   |                                      |

| Rise time of RxS, RxA   | tir         | -        | 100          | ns   |                                      |

| Fall time of RxS, RxA   | tif         | -        | 100          | ns   |                                      |

| Positive jitter of RxS  | <b>t</b> PJ | -        | 0.15         | tвт  |                                      |

| Negative jitter of RxS  | tpn         | -        | 0.15         | tвт  |                                      |

| RxA setup time          | tcds        | 0        | -            | ns   |                                      |

| RxA hold time           | tcdh        | 0        | _            | ns   |                                      |

| RD* pulse width         | tpwrd       | 200      | -            | ns   |                                      |

| WR* pulse width         | tpwwr       | 200      | -            | ns   |                                      |

| E pulse width           | tpweh       | 200      | -            | ns   |                                      |

| Address setup time      | tas         | 9        | -            | ns   |                                      |

| Address hold time       | tah         | 0        | -            | ns   |                                      |

| Data setup time         | tDS         | 2        | -            | ns   |                                      |

| Data hold time          | tDH         | 9        | -            | ns   |                                      |

| CS* setup time          | tcs         | 0        | -            | ns   |                                      |

| CS* hold time           | tch         | 0        | -            | ns   |                                      |

| R/W* setup time         | trws        | 1        | -            | ns   |                                      |

| R/W* hold time          | trwh        | 1        | -            | ns   |                                      |

| Data output delay time  | tddr        |          | 86           | ns   |                                      |

| Read data hold time     | tdhr        | 14       | <b>65</b> ♦2 | ns   |                                      |

| RDY output delay time   | trdw        | -        | 60           | ns   |                                      |

| RDY pulse width         | tpwrl       | 0        | 4            | tcyc |                                      |

| RDY hold time           | trdwh       | 0        | -            | ns   |                                      |

| Read data valid to RDY  | tdvr        | _        | 1            | tcyc | Period(RDY=LOW)                      |

| TxS to TxE/ADD (jitter) | tJCR        | -3.5     | 3.5          | ns   |                                      |

| TxS to TxE/ADD (jitter) | tJSM        | -0.7     | 0.7          | ns   |                                      |

| ACK* setup time         | taks        | 3        | -            | ns   |                                      |

| ACK* hold time          | takh        | 0        | -            | ns   |                                      |

| RQ clear time           | trqc        |          | 60           | ns   |                                      |

$V_{DD} = 3.0V \pm 10\%$ ,  $TA = -40 \sim 85^{\circ}C$ , Output Load = 50pF.

Note † : PRD bit in Clock Mode register and CLOCK bits in Mode register

† 2: Data bus is in Hi-z status at tDHR Max

$5V \pm 10\%$  operation

| Description             | Symbol | Min      | Max    | Unit | Condition                            |

|-------------------------|--------|----------|--------|------|--------------------------------------|

|                         |        | 0.50±    | 0.1%   |      | PRD <sup>♦</sup> = 1 <sub>B</sub>    |

|                         |        | 1.0±     | 0.1%   | MHz  | CLOCK <sup>♦</sup> = 00 <sub>B</sub> |

| Clock frequency         | FCLK   | 2.0±0.1% |        | 1    | CLOCK <sup>♦</sup> = 01 <sub>B</sub> |

|                         |        | 4.0±     | 0.1%   | 1    | CLOCK <b>†</b> = 10 <sub>B</sub>     |

|                         |        | 8.0±     | 0.1%   | 1    | CLOCK *= 11B                         |

|                         |        | 16.0±    | 0.1%   |      | PRD <sup>♦</sup> = 1 <sub>B</sub>    |

| CLK pulse width (LOW)   | tPWL   | 25       | -      | ns   |                                      |

| CLK pulse width (HIGH)  | tpwh   | 25       | -      | ns   |                                      |

| RESET* pulse width      | trst   | 4        | -      | tcyc | stays in LOW                         |

| Bit time of RxS         | tBT    | 32 ±     | 0.9    | μs   | 31.25kbps                            |

|                         |        | 1.0±     | 0.025  | μs   | 1Mbps                                |

| Rise time of RxS, RxA   | tir    | -        | 100    | ns   |                                      |

| Fall time of RxS, RxA   | tıF    | -        | 100    | ns   |                                      |

| Positive jitter of RxS  | tpJ    | -        | 0.15   | tBT  |                                      |

| Negative jitter of RxS  | tpn    | -        | 0.15   | tBT  |                                      |

| RxA setup time          | tcds   | 0        | -      | ns   |                                      |

| RxA hold time           | tcdh   | 0        | -      | ns   |                                      |

| RD* pulse width         | tpwrd  | 50       | -      | ns   |                                      |

| WR* pulse width         | tpwwr  | 50       | -      | ns   |                                      |

| E pulse width           | tpweh  | 50       | -      | ns   |                                      |

| Address setup time      | tas    | 5        | -      | ns   |                                      |

| Address hold time       | tah    | 0        | -      | ns   | ,                                    |

| Data setup time         | tDS    | 2        | -      | ns   |                                      |

| Data hold time          | tDH    | 5        | -      | ns   |                                      |

| CS* setup time          | tcs    | 0        | -      | ns   |                                      |

| CS* hold time           | tсн    | 0        | -      | ns   |                                      |

| R/W* setup time         | trws   | 1        | -      | ns   |                                      |

| R/W* hold time          | trwh   | . 1      | -      | ns   |                                      |

| Data output delay time  | tddr   | _        | 39     | ns   |                                      |

| Read data hold time     | tdhr   | 5        | 36 ♦ 2 | ns   |                                      |

| RDY output delay time   | trdw   | -        | 30     | ns   |                                      |

| RDY pulse width         | tpwrl  | 0        | 4      | tcyc | Period(RDY=LOW)                      |

| RDY hold time           | trdwh  | 0        | -      | ns   |                                      |

| Read data valid to RDY  | tdvr   | -        | 1      | tcyc |                                      |

| TxS to TxE/ADD (jitter) | tJCR   | -1.5     | 1.5    | ns   |                                      |

| TxS to TxE/ADD (jitter) | USM    | -0.6     | 0.6    | ns   |                                      |

| ACK* setup time         | taks   | 3        | -      | ns   |                                      |

| ACK* hold time          | takh   | 0        | -      | ns   |                                      |

| RQ clear time           | trQC   | -        | 30     | ns   |                                      |

$V_{DD} = 5.0V \pm 10\%$ ,  $TA = -40 \sim 85^{\circ}C$ , Output Load = 50pF.

Note †: PRD bit in Clock Mode register and CLOCK bits in Mode register

♦ 2: Data bus is in Hi-z status at tDHR Max

$5V \pm 5\%$  operation

| Description             | Symbol | Min      | Max           | Unit | Condition                         |

|-------------------------|--------|----------|---------------|------|-----------------------------------|

|                         |        | 0.50±    | -0.1%         |      | PRD <sup>♦</sup> = 1 <sub>B</sub> |

|                         |        | <b></b>  | 0.1%          | MHz  | CLOCK * = 00B                     |

| Clock frequency         | Fclk   | 2.0±0.1% |               |      | CLOCK * = 01B                     |

| Crook requestey         | T CEM  |          | 0.1%          |      | CLOCK * = 10B                     |

|                         |        | <b></b>  | 0.1%          |      | CLOCK * = 11B                     |

|                         |        | <b>!</b> | 0.1%          |      | PRD *= 1B                         |

| CLK pulse width (LOW)   | tPWL   | 25       | -             | ns   |                                   |

| CLK pulse width (HIGH)  | tPWH   | 25       | -             | ns   |                                   |

| RESET* pulse width      | trst   | 4        | -             | tcyc | stays in LOW                      |

| Bit time of RxS         | tBT    | 32±      | -0.9          | μs   | 31.25kbps                         |

|                         |        | 1.0±     | 0.025         | μs   | 1Mbps                             |

| Rise time of RxS, RxA   | tir    | -        | 100           | ns   |                                   |

| Fall time of RxS, RxA   | tiF    | -        | 100           | ns   |                                   |

| Positive jitter of RxS  | tpJ    | -        | 0.15          | tвт  |                                   |

| Negative jitter of RxS  | tpn    | -        | 0.15          | tвт  |                                   |

| RxA setup time          | tcds   | 0        | -             | ns   |                                   |

| RxA hold time           | tcdh   | 0        | -             | ns   |                                   |

| RD* pulse width         | tpwrd  | 50       | -             | ns   |                                   |

| WR* pulse width         | tpwwr  | 50       | -             | ns   |                                   |

| E pulse width           | tpweh  | 50       | -             | ns   |                                   |

| Address setup time      | tas    | 5        | -             | ns   |                                   |

| Address hold time       | tah    | 0        | -             | ns   |                                   |

| Data setup time         | tDS    | 2        | -             | ns   |                                   |

| Data hold time          | tDH    | 4        | -             | ns   |                                   |

| CS* setup time          | tcs    | 0        | -             | ns   |                                   |

| CS* hold time           | tсн    | 0        | -             | ns   |                                   |

| R/W* setup time         | trws   | 1        | -             | ns   |                                   |

| R/W* hold time          | trwh   | 1        | -             | ns   |                                   |

| Data output delay time  | tddr   | -        | 30            | ns   |                                   |

| Read data hold time     | tdhr   | 20       | 32 <b>♦</b> 2 | ns   |                                   |

| RDY output delay time   | trdw   | -        | 26            | ns   |                                   |

| RDY pulse width         | tpwrl  | 0        | 4             | tcyc | Period(RDY=LOW)                   |

| RDY hold time           | trdwh  | 0        | _             | ns   |                                   |

| Read data valid to RDY  | tdvr   | -        | 11            | tcyc |                                   |

| TxS to TxE/ADD (jitter) | tJCR   | -1.5     | 1.5           | ns   |                                   |

| TxS to TxE/ADD (jitter) | tJSM   | -0.6     | 0.6           | ns   |                                   |

| ACK* setup time         | taks   | 3        | -             | ns   |                                   |

| ACK* hold time          | takh   | 0        | -             | ns   |                                   |

| RQ clear time           | trQC   | -        | 26            | ns   |                                   |

$V_{DD} = 5.0V \pm 5\%$ , TA = 0~70°C, Output Load = 50pF.

Note  $\phi$ : PRD bit in Clock Mode register and CLOCK bits in Mode register

\$\psi\_2\$: Data bus is in Hi-z status at tDHR Max

## **Package Dimension**

## 1. YTZ420-VZ

C-PK44VP1-1

端子厚さ/Lead Thickness: 0.17

モールドコナー形状は、本図面と若干異なるタイプもあります。 We have a different corner type of plastic body from this drawing.

カッコ内の寸法値は参考値とする。

The value parenthesized is not specified.

E-MY外形寸法はバリを含まない。 Plastic body dimensions do not include burr of resin.

UNIT: mm

表面実装LSIは、保管条件、及び半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせください。

Note: The storage and soldering of LSIs for surface mounting need special consideration. For detailed information, please contact your local Yamaha agent.

## 2. YTZ420-FZ

## C-PK44FP-1

モールドコーナー形状は、この図面と若干異なるタイプもあります。カッコ内の寸法値は参考値です。

モールド外形寸法はバリを含みません。

単位: mm

The shape of the molded corner may slightly differ from the shape in this diagram. The figure in the parentheses () should be used as a reference.

Plastic body dimensions do not include resin burr.

UNIT: mm

## 注) 表面実装LSIは、保管条件、及び半田付けについての特別な配慮が必要です。 詳しくはヤマハ代理店までお問い合わせください。

Note: The storage and soldering of LSIs for surface mounting need special consideration. For detailed information, please contact your local Yamaha agent.

### IMPORTANT NOTICE

- YAMAHA RESERVES THE RIGHT TO MAKE CHANGES TO ITS PRODUCTS AND TO THIS DOCUMENT WITHOUT

NOTICE. THE INFORMATION CONTAINED IN THIS DOCUMENT HAS BEEN CAREFULLY CHECKED AND IS

BELIEVED. HOWEVER, YAMAHA SHALL ASSUME NO RESPONSIBILITIES FOR INACCURACIES AND MAKE NO

COMMITMENT TO UPDATE OR TO KEEP CURRENT THE INFORMATION CONTAINED IN THIS DOCUMENT.

- 2. THESE YAMAHA PRODUCTS ARE DESIGNED ONLY FOR COMMERCIAL AND NORMAL INDUSTRIAL APPLICATIONS, AND ARE NOT SUITABLE FOR OTHER USES, SUCH AS MEDICAL LIFE SUPPORT EQUIPMENT, NUCLEAR FACILITIES, CRITICAL CARE EQUIPMENT OR ANY OTHER APPLICATION THE FAILURE OF WHICH COULD LEAD TO DEATH, PERSONAL INJURY OR ENVIRONMENTAL OR PROPERTY DAMAGE. USE OF THE PRODUCTS IN ANY SUCH APPLICATION IS AT THE CUSTOMER'S OWN RISK AND EXPENSE.

- YAMAHA SHALL ASSUME NO LIABILITY FOR INCIDENTAL, CONSEQUENTIAL OR SPECIAL DAMAGES OR INJURY THAT MAY RESULT FROM MISAPPLICATION OR IMPROPER USE OR OPERATION OF THE PRODUCT.

- 4. YAMAHA MAKES NO WARRANTY OR REPRESENTATION THAT THE PRODUCTS ARE SUBJECT TO INTELLECTUAL PROPERTY LICENSE FROM YAMAHA OR ANY THIRD PARTY, AND YAMAHA MAKES NO WARRANTY OR REPRESENTATION OF NON-INFRINGEMENT WITH RESPECT TO THE PRODUCTS. YAMAHA SPECIFICALLY EXCLUDES ANY LIABILITY TO THE CUSTOMER OR ANY THIRD PARTY ARISING FROM OR RELATED TO THE PRODUCTS INFRINGEMENT OF ANY THIRD PARTY'S INTELLECTUAL PROPERTY RIGHTS, INCLUDING THE PATENT, COPYRIGHT, TRADEMARK OR TRADE SECRET RIGHTS OF ANY THIRD PARTY.

- 5. EXAMPLES OF USE DESCRIBED HEREIN ARE MERELY TO INDICATE THE CHARACTERISTICS AND PERFORMANCE OF PRODUCTS. YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR ANY INTELLECTUAL PROPERTY CLAIMES OR OTHER PROBLEMS THAT MAY RESULT FROM APPLICATIONS BASED ON THE EXAMPLES DESCRIBED HEREIN. YAMAHA MAKES NO WARRANTY WITH RESPECT TO THE PRODUCTS, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR USE AND TITLE.

- 6. YAMAHA MAKES EVERY EFFORT TO IMPROVE THE QUALITY AND RELIABILITY OF ITS PRODUCTS. HOWEVER, ALL SEMICONDUCTOR PRODUCTS FAIL WITH SOME PROBABILITY. THEREFORE, YAMAHA REQUIRES THAT SUFFICIENT CARE BE GIVEN TO ENSURING SAFE DESIGN IN CUSTOMER PRODUCTS SUCH AS REDUNDANT DESIGN, ANTI-CONFLAGRATION DESIGN, AND DESIGN FOR PREVENTING MALFUNCTION IN ORDER TO PREVENT ACCIDENTS RESULTING IN INJURY OR DEATH, FIRE OR OTHER SOCIAL DAMAGE FROM OCCURRING AS A RESULT OF PRODUCT FAILURE.

- 7. INFORMATION DESCRIBED IN THIS DOCUMENT: APPLICATION CIRCUITS AND ITS CONSTANTS AND CALCULATION FORMULAS, PROGRAMS AND CONTROL PROCEDURES ARE PROVIDED FOR THE PURPOSE OF EXPLAINING TYPICAL OPERATION AND USAGE. THEREFORE, PLEASE EVALUATE THE DESIGN SUFFICIENTLY AS WHOLE SYSTEM UNDER THE CONSIDERATION OF VARIOUS EXTERNAL OR ENVIRONMENTAL CONDITIONS AND DETERMINE THEIR APPLICATION AT THE CUSTOMER'S OWN RISK. YAMAHA SHALL ASSUME NO RESPONSIBILITY FOR CLAIMS, DAMAGES, COSTS AND EXPENSES CAUSED BY THE CUSTOMER OR ANY THIRD PARTY, OWING TO THE USE OF THE ABOVE INFORMATION.

Notice

The specifications of this product are subject to improvement changes without prior notice.

AGENT —

## - YAMAHA CORPORATION -

Address inquiries to:

Semiconductor Sales & Marketing Department

■ Head Office 203, Matsunokijima, Iwata,

Shizuoka, 438-Ŏ192, Japan

Tel. +81-539-62-4918 Fax. +81-539-62-5054

■ Tokyo Office 2-17-11, Takanawa, Minato-ku,

Tokyo, 108-8568, Japan

Tel. +81-3-5488-5431 Fax. +81-3-5488-5088

■ Osaka Office 3-12-12, Minami Senba, Chuo-ku,

Osaka City, Osaka, 542-0081, Japan Tel. +81-6-6252-6221 Fax. +81-6-6252-6229