# **TMC2210**

# **CMOS Multiplier-Accumulator**

16 x 16 Bit, 65, 80, 95 ns

# **Description**

The TMC2210 is a high-speed 16 x 16 bit digital multiplier-accumulator which is available in speed bins of 65, 80 or 95 ns. Input data may be specified as two's complement or unsigned magnitude, yielding a 32-bit product. Products may be accumulated to a 35-bit result.

Individually clocked input and output registers are provided to maximize system throughput and simplify bus interfacing. These registers are constructed using positive-edge-triggered D-type flip-flops. The result is divided into a 3-bit Extended Product (XTP), a 16-bit Most Significant Product (MSP) and a 16-bit Least Significant Product (LSP). Individual three-state output ports are provided for the XTP and MSP. The LSP is multiplexed with the Y operand inputs. The output register can be preloaded directly via the output ports.

The TMC2210 is a drop in replacement for the TMC2010 and the TMC2110, and is pin and function compatible with the industry standard Raytheon Semiconductor La Jolla TDC1010, the LMA1010/2010, IDT7210 and CY7510.

### **Features**

- ♦ 65, 80 or 95 ns multiply-accumulate time

- 16 x 16 parallel multiplication with accumulation to 35-bit result

- Selectable accumulation, subtraction, rounding, and accumulator preload

- Two's complement or unsigned magnitude operation

- All inputs and outputs are registered and TTL compatible

- ◆ Low power consumption CMOS process

- ♦ Single +5V power supply

- Available in a 64-pin ceramic or plastic DIP, 68-pin grid array and 68-lead plastic J-leaded chip carrier

# **Applications**

- Array processors

- ♦ Video processors

- Radar signal processors

- ◆ FFT processors

- General purpose digital signal processors

- Microcomputer/minicomputer accelerators

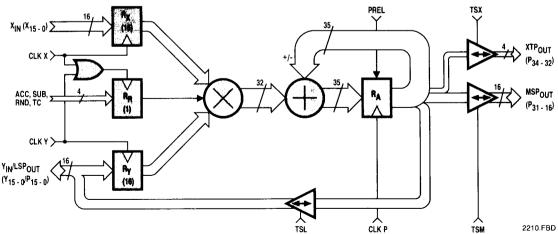

# **Functional Block Diagram**

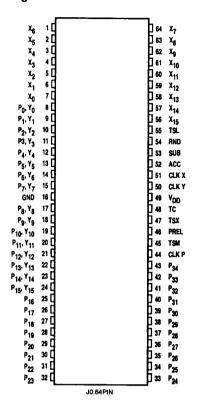

## **Pin Assignments**

64 Pin Hermetic Ceramic DIP - J0, NO Package

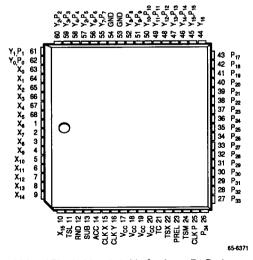

68-Lead Plastic J-Leaded chip Carrier — R1 Package

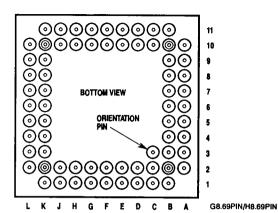

68 Pin Ceramic (G8) or Plastic (H8) Pin Grid Array

| Pin | Name                            | Pin | Name                            | Pin | Name                              | Pin        | Name            |

|-----|---------------------------------|-----|---------------------------------|-----|-----------------------------------|------------|-----------------|

| A2  | NC                              | В9  | X <sub>12</sub>                 | F10 | V <sub>DD</sub>                   | K4         | P <sub>20</sub> |

| A3  | Po, Yo                          | B10 | X <sub>14</sub>                 | F11 | CLK Y                             | K5         | P <sub>22</sub> |

| A4  | X <sub>1</sub>                  | B11 | NC                              | G1  | P <sub>11</sub> , Y <sub>11</sub> | K6         | P <sub>24</sub> |

| A5  | Х3                              | C1  | P4, Y4                          | G2  | P <sub>10</sub> , Y <sub>10</sub> | K7         | P <sub>26</sub> |

| A6  | X <sub>5</sub>                  | C2  | P <sub>3</sub> , Y <sub>3</sub> | G10 | TSX                               | K8 .       | P <sub>28</sub> |

| Α7  | X <sub>7</sub>                  | C10 | TSL                             | G11 | TC                                | K9         | P <sub>30</sub> |

| A8  | X <sub>9</sub>                  | C11 | X <sub>15</sub>                 | H1  | P <sub>13</sub> , Y <sub>13</sub> | K10        | P <sub>32</sub> |

| A9  | X <sub>11</sub>                 | D1  | P <sub>6</sub> , Y <sub>6</sub> | H2  | P <sub>12</sub> , Y <sub>12</sub> | K11        | P <sub>33</sub> |

| A10 | X <sub>13</sub>                 | D2  | P <sub>5</sub> , Y <sub>5</sub> | H10 | TSM                               | L2         | P <sub>17</sub> |

| B1  | P <sub>2</sub> , Y <sub>2</sub> | D10 | SUB                             | H11 | PREL                              | L3         | P <sub>19</sub> |

| B2  | P <sub>1</sub> , Y <sub>1</sub> | D11 | RND                             | J1  | P <sub>15</sub> , Y <sub>15</sub> | L4         | P <sub>21</sub> |

| B3  | x <sub>0</sub>                  | E1  | GND                             | J2  | P <sub>14</sub> , Y <sub>14</sub> | <b>L</b> 5 | P <sub>23</sub> |

| B4  | X <sub>2</sub>                  | E2  | P7, Y7                          | J10 | P <sub>34</sub>                   | L6         | P <sub>25</sub> |

| B5  | X <sub>4</sub>                  | E10 | CLK X                           | J11 | CLK P                             | L7         | P <sub>27</sub> |

| B6  | x <sub>6</sub>                  | E11 | ACC                             | K1  | NC                                | L8         | P <sub>29</sub> |

| B7  | Х <sub>8</sub>                  | F1  | Pg, Yg                          | K2  | P <sub>16</sub>                   | L9         | P <sub>31</sub> |

| B8  | X <sub>10</sub>                 | F2  | P <sub>8</sub> , Y <sub>8</sub> | К3  | P <sub>18</sub>                   | L10        | NC              |

## **Functional Description**

### **General Information**

The TMC2210 consists of four functional sections: input registers, an asynchronous multiplier array, an adder and output registers. The input registers store the two 16-bit numbers which are to be multiplied and the control lines which control the input numerical format (two's complement or unsigned magnitude), output rounding, accumulation and subtraction. The round control is used when a single-word output is desired. Each number is independently stored, simplifying multiplication by a constant. The output registers can be preloaded with a constant to provide the sum of products plus a constant. The asynchronous multiplier array uses a modified Booth's algorithm and has been designed to handle two's complement or unsigned magnitude numbers. The output registers hold the product as two 16-bit words and one 3-bit word: the MSP, the LSP and the XTP. Three-state output drivers permit the TMC2210 to be used on a bus or allow the outputs to be multiplexed over the same 16-bit output lines. The LSP is multiplexed with the Y input.

The TMC2210 has three clock lines, one for each of the input registers and one for the product register. Data present at the inputs of these registers are loaded into the registers on the rising edge of the appropriate clock. The Round (RND), Two's Complement (TC), Accumulate (ACC) and Subtract (SUB) inputs are registered and all four bits are clocked in on the rising edge of the logical OR of both CLK X and CLK Y. Problems with the loading of these four control signals can be avoided by the use of normally LOW clocks.

# **Signal Definitions**

#### Power

V<sub>DD</sub>, GND

The TMC2210 operates from a single +5V supply. All power and ground lines must be connected.

#### **Data Inputs**

X<sub>15-0</sub>, Y<sub>15-0</sub> There are two 16-bit two's complement or unsigned magnitude data inputs, labeled X and Y. The Most Significant Bits (MSBs), denoted  $X_{15}$  and  $Y_{15}$ , carry the sign information when two's complement notation is used. The remaining bits are denoted  $X_{14-0}$  and  $Y_{14-0}$  (with  $X_0$  and  $Y_0$

the Least Significant Bits). Data present at the X and Y inputs are clocked into the input registers on the rising edge of the appropriate clock.

### **Data Outputs**

P34-0

There is a 35-bit two's complement or unsigned magnitude result that is the sum of the products of the two input data values and the previous products which have been accumulated. The output is divided into two 16-bit output words, the MSP and LSP, and one 3-bit output word, the XTP. The MSB of the XTP is the sign bit if two's complement notation is used.

#### Clocks

CLK X CLK Y CLK P CLK X is the clock input for the X<sub>15-0</sub> data register. CLK Y is the clock input for the Y<sub>15-0</sub> data register. CLK P is the clock input for the product register.

### **Controls**

TSX, TSM, TSL TSX, TSM and TSL are three-state enable lines for the XTP, the MSP and the LSP, respectively. The output driver is in the high-impedance state when TSX, TSM or TSL is HIGH and enabled when the appropriate control is LOW.

PREL

PREL (Preload) is an active HIGH control which has several effects when active. First, all output buffers are forced into the high-impedance state. Second, when any or all of TSX, TSM and TSL are also HIGH, external data present at the output pins will be preloaded into the corresponding section of the output register on the rising edge of CLK P. Normal data setup and hold times apply both to the logical AND of PREL and the relevant three-state control (TSX, TSM, TSL) and to the data being preloaded. These setup and hold times are with respect to the rising edge of CLK P.

**RND**

RND (Round) controls the addition of a one to the MSB of the LSP for rounding. When RND is HIGH, a one is added to the MSB of the LSP for rounding the product in the MSP and XTP (if appropriate) rather than truncating.

# **TMC2210**

### Controls (cont.)

TC

TC (Two's Complement) controls how the device interprets data on the X and Y inputs. When TC is HIGH, both inputs are two's complement inputs. When TC is LOW, both inputs are unsigned magnitude only inputs. The necessary sign extension for negative two's complement numbers is provided internally.

ACC

When ACC (Accumulate) is HIGH, the content of the output register is added to or subtracted from the next product generated, and the result is stored back into the output registers on the next rising edge of CLK P. When ACC is LOW, multiplication without accumulation is performed, and the next product generated will be stored into the output registers directly. This operation is used for the first term in a summation to eliminate the need for a separate "clear" operation.

SUB

The SUB (Subtract) control is used in conjunction with the ACC control. When both the ACC and SUB controls are HIGH, the content of the output register is subtracted from the next product generated, and the difference is stored back into the output register. When ACC is HIGH and SUB is LOW, the content of the output register is added to the next product generated and the sum is stored back into the output register. Note that the previous output is subtracted from the product, not the product from the previous output.

### **No Connects**

NC

The pin grid array version of the TMC2210 has four pins which are not connected internally.

### **Package Interconnections**

| Signal<br>Type | Signal<br>Name    | Function         | G8, H8 Package Pins                                                                                                                                    | JO, NO Package Pins | R1 Package Pins |

|----------------|-------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|

| Power          | $V_{DD}$          | Supply Voltage   | F10                                                                                                                                                    | 49                  | 17, 18, 19, 20  |

|                | GND               | Ground           | E1                                                                                                                                                     | 16                  | 53, 54          |

| Data Inputs    | X <sub>15-0</sub> | X Input Word     | C11, B10, A10, B9, A9, B8, A8, B7,<br>A7, B6, A6, B5, A5, B4, A4, B3                                                                                   | 56-64, 1-7          | 1-10, 63-68     |

|                | Y <sub>15-0</sub> | Y Input Word     | J1, J2, H1, H2, G1, G2, F1, F2,<br>E2, D1, D2, C1, C2, B1, B2, A3                                                                                      | 24-17, 15-8         | 45-52, 55-62    |

| Data Outputs   | P <sub>34-0</sub> | Product Output   | J10, K11, K10, L9, K9, L8, K8, L7, K7,<br>L6, K6, L5, K5, L4, K4, L3, K3, L2,<br>K2, J1, J2, H1, H2, G1, G2, F1, F2,<br>E2, D1, D2, C1, C2, B1, B2, A3 | 43-17, 15-8         | 26-52, 55-62    |

| Clocks         | CLK X             | X Register Clock | E10                                                                                                                                                    | 51                  | 15              |

|                | CLK Y             | Y Register Clock | F11                                                                                                                                                    | 50                  | 16              |

|                | CLK P             | P Regsiter Clock | J11                                                                                                                                                    | 44                  | 25              |

| Controls       | TSX               | XTP Three-State  | G10                                                                                                                                                    | 47                  | 22              |

|                | TSM               | MSP Three-State  | H10                                                                                                                                                    | 45                  | 24              |

|                | TSL               | LSP Three-State  | C10                                                                                                                                                    | 55                  | 11              |

|                | PREL              | Preload          | H11                                                                                                                                                    | 46                  | 23              |

|                | RND               | Round            | D11                                                                                                                                                    | 54                  | 12              |

|                | TC                | Two's Complement | G11                                                                                                                                                    | 48                  | 21              |

| j              | ACC               | Accumulate       | E11                                                                                                                                                    | 52                  | 14              |

|                | SUB               | Subtract         | D10                                                                                                                                                    | 53                  | 13              |

| No Connects    | NC                | No Connection    | K1, L10, B11, A2                                                                                                                                       | -                   | _               |

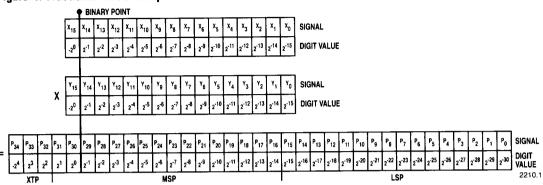

Figure 1. Fractional Two's Complement Notation

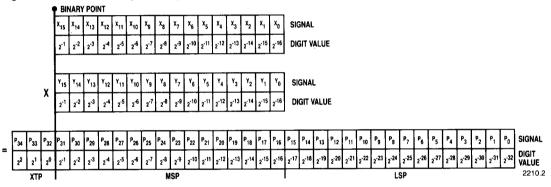

Figure 2. Fractional Unsigned Magnitude Notation

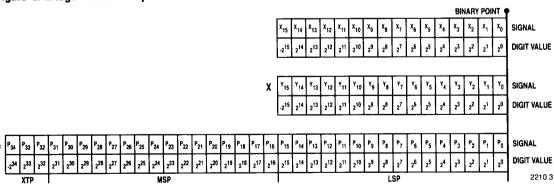

Figure 3. Integer Two's Complement Notation

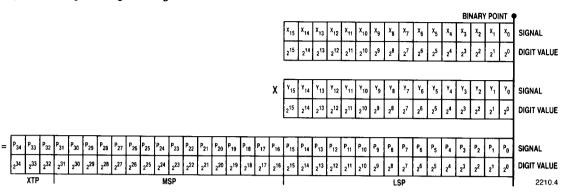

Figure 4. Integer Unsigned Magnitude Notation

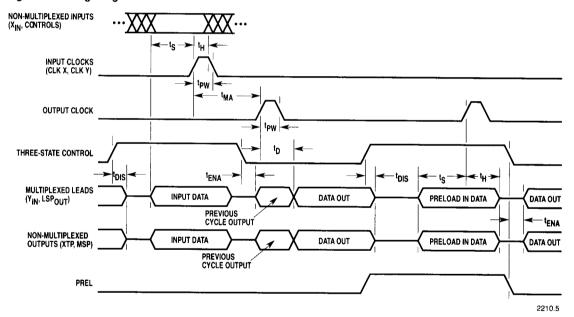

Figure 5. Timing Diagram

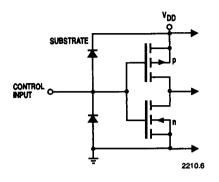

Figure 6. Equivalent Input Circuit

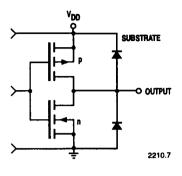

Figure 7. Equivalent Output Circuit

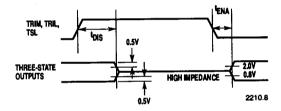

Figure 8. Threshold Levels for Three-State Measurements

## **Preload Truth Table**

| PREL <sup>1, 2</sup> | TSX1 | TSM <sup>1</sup> | TSL <sup>1</sup> | ХТР                   | MSP                   | LSP                   |

|----------------------|------|------------------|------------------|-----------------------|-----------------------|-----------------------|

| 0                    | 0    | 0                | 0                | Register → Output Pin | Register → Output Pin | Register → Output Pin |

| 0                    | 0    | 0                | 1                | Register → Output Pin | Register → Output Pin | Hi-Z                  |

| 0                    | 0    | 1                | 0                | Register → Output Pin | Hi-Z                  | Register → Output Pin |

| 0                    | 0    | 1                | 1                | Register → Output Pin | Hi-Z                  | Hi-Z                  |

| 0                    | 1    | 0                | 0                | Hi-Z                  | Register → Output Pin | Register → Output Pin |

| 0                    | 1    | 0                | 1                | Hi-Z                  | Register → Output Pin | Hi-Z                  |

| 0                    | 1    | 1                | 0                | Hi-Z                  | Hi-Z                  | Register → Output Pin |

| 0                    | 1    | 1                | 1                | Hi-Z                  | Hi-Z                  | Hi-Z                  |

| 1                    | 0    | 0                | 0                | Hi-Z                  | Hi-Z                  | Hi-Z                  |

| 1                    | 0    | 0                | 1                | Hi-Z                  | Hi-Z                  | Hi-Z Preload          |

| 1                    | 0    | 1                | 0                | Hi-Z                  | Hi-Z Preload          | Hi-Z                  |

| 1                    | 0    | 1                | 1                | Hi-Z                  | Hi-Z Preload          | Hi-Z Preload          |

| 1                    | 1    | 0                | 0                | Hi-Z Preload          | Hi-Z                  | Hi-Z                  |

| 1                    | 1    | 0                | 1                | Hi-Z Preload          | Hi-Z                  | Hi-Z Preload          |

| 1                    | 1    | 1                | 0                | Hi-Z Preload          | Hi-Z Preload          | Hi-Z                  |

| 1                    | 1    | 1                | 1                | Hi-Z Preload          | Hi-Z Preload          | Hi-Z Preload          |

Notes:

- 1. PREL, TSX, TSM, and TSL are not registered.

- 2. When PREL is HIGH, any change of output register (for those outputs in which the three-state control is LOW) is inhibited.

# Absolute maximum ratings (beyond which the device may be damaged) 1

4. Current is specified as conventional current flowing into the device.

| Supply V  | oltage                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Input Vol | tage                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Outputs   |                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|           | Applied voltage                                                                                                                                                                                                                    |  |  |  |  |  |  |

|           | Forced current                                                                                                                                                                                                                     |  |  |  |  |  |  |

|           | Short-circuit duration (single output in HIGH state to ground)                                                                                                                                                                     |  |  |  |  |  |  |

| Temperat  |                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|           | Operating, case60 to +130°C                                                                                                                                                                                                        |  |  |  |  |  |  |

|           | junction                                                                                                                                                                                                                           |  |  |  |  |  |  |

|           | Lead, soldering (10 seconds)                                                                                                                                                                                                       |  |  |  |  |  |  |

|           | Storage −65 to +150°C                                                                                                                                                                                                              |  |  |  |  |  |  |

| Notes:    | <ol> <li>Absolute maximum ratings are limiting values applied individually while all other parameters are within specified operating conditions.<br/>Functional operation under any of these conditions is NOT implied.</li> </ol> |  |  |  |  |  |  |

|           | 2. Applied voltage must be current limited to specified range.                                                                                                                                                                     |  |  |  |  |  |  |

|           | 3. Forcing voltage must be limited to specified range.                                                                                                                                                                             |  |  |  |  |  |  |

# **Operating conditions**

|                 |                                | Temperature Range |           |              |      |          |       |       |

|-----------------|--------------------------------|-------------------|-----------|--------------|------|----------|-------|-------|

|                 |                                |                   | Commercia |              |      | Military |       | 1     |

| Parameter       |                                | Min               | Nom       | Max          | Min  | Nom      | Max   | Units |

| V <sub>DD</sub> | Supply Voltage                 | 4.75              | 5.0       | 5.25         | 4.5  | 5.0      | 5.5   | V     |

| V <sub>IL</sub> | Input Voltage, Logic LOW       |                   |           | 0.8          |      |          | 0.8   | ٧     |

| VIH             | Input Voltage, Logic HIGH      | 2.0               |           |              | 2.0  |          |       | V     |

| l <sub>OL</sub> | Output Current, Logic LOW      |                   |           | 4.0          |      |          | 4.0   | mA    |

| I <sub>ОН</sub> | Output Current, Logic HIGH     |                   |           | <b>– 2.0</b> |      |          | - 2.0 | mA    |

| TA              | Ambient Temperature, Still Air | 0                 |           | 70           |      |          |       | °C    |

| T <sub>C</sub>  | Case Temperature               |                   |           |              | - 55 |          | 125   | °C    |

# DC characteristics within specified operating conditions

|                  |                                          |                                                        | Temperature Range |         |     |             |       |

|------------------|------------------------------------------|--------------------------------------------------------|-------------------|---------|-----|-------------|-------|

|                  |                                          |                                                        | Comn              | nercial | Mil | itary       | 1     |

| Param            | eter                                     | Conditions                                             | Min               | Max     | Min | Max         | Units |

| IDDQ             | Supply Current, Quiescent                | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V            |                   |         |     |             |       |

| DDQ              | • • • • • • • • • • • • • • • • • • • •  | All Except                                             |                   | 5       |     | 10          | mΑ    |

|                  |                                          | TMC2210-45, -55, Outputs Open                          |                   | 0.5     |     | 0.5         | mΑ    |

| I <sub>DD0</sub> | Supply Current, Unloaded 1               | V <sub>DD</sub> = Max, TSL, TSM, TSX = 5V              |                   |         |     |             |       |

| 550              |                                          | f = 15MHz                                              |                   | 75      |     | 75          | mΑ    |

|                  |                                          | f = 10MHz                                              |                   | 50      |     | 50          | mΑ    |

|                  |                                          | f = 6.2MHz                                             |                   | 30      |     | 30          | mA    |

| 1 <sub>IL</sub>  | Input Current, Logic LOW                 | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V            |                   |         |     |             |       |

| 11.              |                                          | X <sub>15-0</sub> , Controls, Clocks                   |                   | -10     |     | - 10        | mΑ    |

|                  |                                          | P <sub>15-0</sub> , Y <sub>15-0</sub>                  |                   | 40      |     | -40         | mΑ    |

| I <sub>IH</sub>  | Input Current, Logic HIGH                | $V_{DD} = Max, V_{IN} = V_{DD}$                        |                   |         |     |             | 1     |

|                  |                                          | X <sub>15-0</sub> , Controls, Clocks                   |                   | 10      |     | .10         | mΑ    |

|                  |                                          | P <sub>15-0</sub> , Y <sub>15-0</sub>                  |                   | 40      |     | 40          | mΑ    |

| VOL              | Output Voltage, Logic LOW                | V <sub>DD</sub> = Min, I <sub>OL</sub> = +4.0mA        |                   | 0.4     |     | 0.4         | ٧     |

| V <sub>OH</sub>  | Output Voltage, Logic HIGH               | V <sub>DD</sub> =Min, I <sub>OH</sub> = -400μA         | 2.6               |         | 2.6 |             | ٧     |

| l <sub>OZL</sub> | Hi-Z Output Leakage Current, Output LOW  | V <sub>DD</sub> = Max, V <sub>IN</sub> = 0V            |                   | -40     |     | - 40        | μΑ    |

| I <sub>OZH</sub> | Hi-Z Output Leakage Current, Output HIGH | V <sub>DD</sub> =Max, V <sub>IN</sub> =V <sub>DD</sub> |                   | - 40    |     | - 40        | μΑ    |

| Cl               | Input Capacitance                        | f=1.0MHz, T <sub>A</sub> =25°C                         |                   | 10      |     | 10          | pF    |

| $\overline{c_0}$ | Output Capacitance                       | f=1.0MHz, T <sub>A</sub> =25°C                         |                   | 10      |     | 10          | рF    |

| C <sub>I/O</sub> | I/O Capacitance                          | f=1.0MHz, T <sub>A</sub> =25°C                         |                   | 15      |     | 15          | pF    |

|                  |                                          |                                                        | •                 | •       | •   | <del></del> | •     |

Note: 1. Supply current is proportional to f<sub>CLK</sub>, typically 5mA per MHz.

# AC characteristics within specified operating conditions <sup>1</sup>

|        |                           |            |     | Temperature | Range    | ļ   |       |

|--------|---------------------------|------------|-----|-------------|----------|-----|-------|

|        |                           |            |     | nercial     | Military |     |       |

| Parame | WL Clock Pulse Width, LOW | Conditions | Min | Max         | Min      | Max | Units |

| tma N  | Multiply-Accumulate Time  | TMC2210-95 |     | 95          |          | 95  | ns    |

|        | • •                       | TMC2210-80 |     | 80          |          | 80  | ns    |

|        |                           | TMC2210-65 |     | 65          |          | 65  | ns    |

| tpwi C | Clock Pulse Width, LOW    | TMC2210-95 | 15  |             | 15       |     | ns    |

|        |                           | TMC2210-80 | 15  |             | 15       |     | ns    |

|        |                           | TMC2210-65 | 15  |             | 25       | 1   | ns    |

| tpwH   | Clcok PUlse Width, HIGH   | TMC2210-95 | 15  |             | 15       |     | ns    |

|        |                           | TMC2210-80 | 15  |             | 15       |     | ns    |

|        |                           | TMC2210-65 | 15  |             | 25       |     | ns    |

Notes:

- 1. All transitions are measured at a 1.5V level except tena and tols which are measured as shown in Figure 8.

- 2. V<sub>DD</sub> = Min.

# AC characteristics within specified operating conditions 1(cont.)

|       |                    |                                                   |      | Temperature | Range |      |       |

|-------|--------------------|---------------------------------------------------|------|-------------|-------|------|-------|

|       |                    |                                                   | Comr | nercial     | Mili  | tary |       |

| Parar | neter              | Conditions                                        | Min  | Max         | Min   | Max  | Units |

| ts    | Input Setup Time   | Data, ACC, SUB, RND, TC                           |      |             |       |      |       |

| -     |                    | TMC2210-95                                        | 20   |             | 20    |      | ns    |

|       |                    | TMC2210-80                                        | 20   |             | 20    |      | ns    |

|       |                    | TMC2210-65                                        | 15   |             | 25    |      | ns    |

|       |                    | PREL, TSL, TSM, TSX                               |      | <u> </u>    |       |      |       |

|       |                    | TMC2210-95                                        | 30   |             | 30    | Ì    | ns    |

|       |                    | TMC2210-80                                        | 30   |             | 30    |      | ns    |

|       |                    | TMC2210-65                                        | 30   |             | 25    |      | ns    |

| ŧн    | Input Hold Time    | Data, ACC, SUB, RND, TC                           |      |             |       |      |       |

|       |                    | TMC2210-95                                        | 0    |             | 0     |      | ns    |

|       |                    | TMC2210-80                                        | 0    |             | 0     |      | ns    |

|       |                    | TMC2210-65                                        | 0    |             | 3     |      | ns    |

|       |                    | PREL, TSL, TSM, TSX                               |      |             |       |      |       |

|       |                    | TMC2210-95                                        | 3    | <u> </u>    | 3     |      | ns    |

|       |                    | TMC2210-80                                        | 3    |             | 3     |      | ns    |

|       |                    | TMC2210-65                                        | 3    |             | 3     |      | ns    |

| to    | Output Delay       | V <sub>DD</sub> = Min, C <sub>I OAD</sub> = 40 pf |      | t t         |       |      |       |

| _     | , ,                | TMC2210-95                                        |      | 40          |       | 40   | ns    |

|       |                    | TMC2210-80                                        |      | 35          |       | 35   | ns    |

|       |                    | TMC2210-65                                        |      | 35          |       | 35   | ns    |

| tena  | Three-State Output | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 40 pf  |      |             |       |      |       |

|       | Enable Delay       | TMC2210-95                                        |      | 40          |       | 40   | ns    |

|       | •                  | TMC2210-80                                        |      | 30          |       | 35   | ns    |

|       |                    | TMC2210-65                                        |      | 30          |       | 302  | ns    |

| tDIS  | Three-State Output | V <sub>DD</sub> = Min, C <sub>LOAD</sub> = 40 pf  |      |             |       |      |       |

|       | Disable Delay      | TMC2210-95                                        |      | 35          |       | 35   | ns    |

|       | •                  | TMC2210-80                                        |      | 30          |       | 30   | ns    |

|       |                    | TMC2210-65                                        |      | 30          |       | 302  | ns    |

Notes:

<sup>1.</sup> All transitions are measured at a 1.5V level except tena and tops which are measured as shown in Figure 8.

<sup>2.</sup> V<sub>DD</sub> = Min.

## **Application Discussion**

### Multiplication by a Constant

Multiplication by a constant requires that the constant be loaded into the desired input register and that the register not be loaded again until a new constant is desired. The multiply cycle then consists of loading new data and strobing the output register.

#### Selection of Numeric Format

Essentially, the difference between integer, mixed and fractional notation in system design is only conceptual. For example, there is no difference between this operation:

$$6 \times 2 = 12$$

and this operation:

$(6/8) \times (2/8) = 12/64$ .

The difference lies only in constant scale factors (in this case, a factor of 8 in the multiplier and multiplicand and a factor of 64 in the product). However, these scale factors do have implications for hardware design. Because common good design practice assigns a fixed value to any given line (and input and output signals often share the same line), the scale factors determine the connection of the output pins of any multiplier in a system. As a result, only two choices are normally made: integer and fractional notation. If integer notation is used, the LSBs of the multiplier, multiplicand and product all have the same value. If fractional notation is used, the MSBs of the multiplier, multiplicand and product all have the same value.

### Ordering Information

| Product<br>Number | Multiply/<br>Accumulate<br>Time (ns) | Temperature                       | Screening    | Package                               | Package<br>Marking |

|-------------------|--------------------------------------|-----------------------------------|--------------|---------------------------------------|--------------------|

| TMC2210G8C65      | 65                                   | STD: T <sub>A</sub> = 0 to 70℃    | Commercial   | 68-pin Ceramic Pin Grid Array         | 2210G8C65          |

| TMC2210G8C80      | 80                                   | STD: TA = 0 to 70°C               | Commercial   | 68-pin Ceramic Pin Grid Array         | 2210G8C80          |

| TMC2210G8V65      | 65                                   | EXT: T <sub>C</sub> = -55 to 125℃ | MIL-STD-883C | 68-pin Ceramic Pin Grid Array         | 2210G8V65          |

| TMC2210G8V80      | 80                                   | EXT: T <sub>C</sub> = -55 to 125℃ | MIL-STD-883C | 68-pin Ceramic Pin Grid Array         | 2210G8V80          |

| TMC2210G8V95      | 95                                   | EXT: T <sub>C</sub> = -55 to 125℃ | MIL-STD-883C | 68-pin Ceramic Pin Grid Array         | 2210G8V95          |

| TMC2210H8C65      | 65                                   | STD: T <sub>A</sub> = 0 to 70℃    | Commercial   | 68-pin Plastic Pin Grid Array         | 2210H8C65          |

| TMC2210H8C80      | 80                                   | STD: T <sub>A</sub> = 0 to 70℃    | Commercial   | 68-pin Plastic Pin Grid Array         | 2210H8C80          |

| TMC2210J0V80      | 80                                   | EXT: T <sub>C</sub> = -55 to 125℃ | MIL-STD-883C | 64-pin Hermetic Ceramic DIP           | 2210J0V80          |

| TMC2210J0V95      | 95                                   | EXT: T <sub>C</sub> = -55 to 125℃ | MIL-STD-883C | 64-pin Hermetic Ceramic DIP           | 2210J0V95          |

| TMC2210N0C65      | 65                                   | STD: T <sub>A</sub> = 0 to 70℃    | Commercial   | 64-pin Plastic DIP                    | 2210N0C65          |

| TMC2210N0C80      | 80                                   | STD: T <sub>A</sub> = 0 to 70℃    | Commercial   | 64-pin Plastic DIP                    | 2210N0C80          |

| TMC2210N0C95      | 95                                   | STD: T <sub>A</sub> = 0 to 70℃    | Commercial   | 64-pin Plastic DIP                    | 2210N0C95          |

| TMC2210R1C65      | 65                                   | STD: T <sub>A</sub> = 0 to 70℃    | Commercial   | 68-Lead Plastic J-Leaded Chip Carrier | 2210R1C65          |

| TMC2210R1C80      | 80                                   | STD: T <sub>A</sub> = 0 to 70°C   | Commercial   | 68-Lead Plastic J-Leaded Chip Carrier | 2210R1C65          |

40G02412 Rev E 8/93