### PLL CLOCK MULTIPLIER

### IDT5V80023

# **Description**

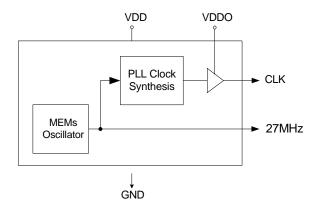

The IDT5V80023 is the most cost effective way to generate a high-quality, high-frequency clock output. The device also features a 27MHz output, making it ideal for systems to replace a high frequency oscillator along with a 1.8V 27MHz crystal.

Using Phase-Locked Loop (PLL) techniques, the device employs IDT's propietary MEMs oscillator technology to produce common output frequencies for consumer, computing, and embedded applications.

### **Features**

- Packaged in a small form factor 16-pin QFN

- Eliminates the need for an external crystal or input clock source

- Max. ±50ppm error on CLK and 27MHz output

- Typical ±75 ps short term cycle-cycle jitter

- Output voltage of 3.3V

- Operating voltage of 1.8V

- Supports industrial temperature range

- Supports output frequency on CLK up to 220MHz

- Advanced, low-power CMOS process

## **Block Diagram**

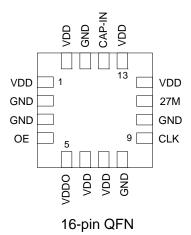

# **Pin Assignment**

# **CLK Output Frequency/Part Number Table**

| Frequency     | Orderable Part Number |

|---------------|-----------------------|

| 11.2896 MHz   | 5V80023-112NLGI       |

| 12 MHz        | 5V80023-012NLGI       |

| 12.288 MHz    | 5V80023-122NLGI       |

| 14.31818 MHz  | 5V80023-143NLGI       |

| 19.2 MHz      | 5V80023-192NLGI       |

| 20 MHz        | 5V80023-020NLGI       |

| 22.5792 MHz   | 5V80023-225NLGI       |

| 24 MHz        | 5V80023-024NLGI       |

| 24.576 MHz    | 5V80023-245NLGI       |

| 25 MHz        | 5V80023-025NLGI       |

| 26 MHz        | 5V80023-026NLGI       |

| 27 MHz        | 5V80023-027NLGI       |

| 33.3333 MHz   | 5V80023-333NLGI       |

| 33.8688 MHz   | 5V80023-338NLGI       |

| 38.864 MHz    | 5V80023-388NLGI       |

| 48 MHz        | 5V80023-048NLGI       |

| 50 MHz        | 5V80023-050NLGI       |

| 61.44MHz      | 5V80023-614NLGI       |

| 66.6666 MHz   | 5V80023-666NLGI       |

| 74.25 MHz     | 5V80023-742NLGI       |

| 74.175824 MHz | 5V80023-741NLGI       |

| 125 MHz       | 5V80023-125NLGI       |

Note: Contact IDT for any other frequencies.

# **Pin Descriptions**

| Pin<br>Number | Pin<br>Name | Pin<br>Type | Pin Description                                                        |

|---------------|-------------|-------------|------------------------------------------------------------------------|

| 1             | VDD         | Power       | Connect to +1.8V.                                                      |

| 2             | GND         | Ground      | Connect this pin to ground.                                            |

| 3             | GND         | Ground      | Connect this pin to ground.                                            |

| 4             | OE          | Input       | Output enable pin for CLK output.                                      |

| 5             | VDDO        | Power       | Connect to +3.3V.                                                      |

| 6             | VDD         | Power       | Connect to +1.8V.                                                      |

| 7             | VDD         | Power       | Connect to +1.8V.                                                      |

| 8             | GND         | Ground      | Connect this pin to ground.                                            |

| 9             | CLK         | Output      | Single-ended clock output.                                             |

| 10            | GND         | Ground      | Connect this pin to ground.                                            |

| 11            | 27M         | Output      | 27MHz reference output at 1.8V.                                        |

| 12            | VDD         | Power       | Connect to +1.8V.                                                      |

| 13            | VDD         | Power       | Connect to +1.8V.                                                      |

| 14            | CAP-IN      | _           | This pin should be connected to GND (pin 15) through a 10µF capacitor. |

| 15            | GND         | Ground      | Connect this pin to ground.                                            |

| 16            | VDD         | Power       | Connect to +1.8V.                                                      |

## **External Components**

### **Decoupling Capacitor**

As with any high-performance mixed-signal IC, the IDT5V80023 must be isolated from system power supply noise to perform optimally.

A decoupling capacitor of 0.01µF must be connected between VDD and GND. It must be connected close to the IDT5V80023 to minimize lead inductance. No external power supply filtering is required for the IDT5V80023.

#### **Series Termination Resistor**

A  $33\Omega$  terminating resistor can be used next to the CLK pin and 27M pin. The total on-chip capacitance is approximately 12 pF.

## **Absolute Maximum Ratings**

Stresses above the ratings listed below can cause permanent damage to the IDT5V80023. These ratings, which are standard values for IDT commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

| Item                                                   | Rating              |

|--------------------------------------------------------|---------------------|

| Supply Voltage, VDD                                    | 5 V                 |

| All Inputs and Outputs                                 | -0.5 V to VDD+0.5 V |

| Ambient Operating Temperature (industrial temperature) | -40 to +85° C       |

| Storage Temperature                                    | -65 to +150° C      |

| Soldering Temperature                                  | 260° C              |

# **Recommended Operation Conditions**

| Parameter                                         | Min.   | Тур. | Max.   | Units |

|---------------------------------------------------|--------|------|--------|-------|

| Ambient Operating Temperature (commercial)        | 0      | _    | +70    | °C    |

| Ambient Operating Temperature (industrial)        | -40    | _    | +85    | °C    |

| Power Supply Voltage (measured in respect to GND) | +1.71  | +1.8 | +1.89  | V     |

| Power Supply Voltage (VDDO)                       | +3.135 | +3.3 | +3.465 | V     |

### **DC Electrical Characteristics**

**VDD=1.8 V \pm 5\%**, **VDDO = 3.3 V,** Ambient temperature -40 to  $+85^{\circ}$  C, unless stated otherwise

| Parameter                    | Symbol          | Conditions                    | Min.     | Тур. | Max.    | Units |

|------------------------------|-----------------|-------------------------------|----------|------|---------|-------|

| Operating Voltage            | VDD             |                               | 1.71     | 1.8  | 1.89    | V     |

| Output Voltage               | VDDO            | CLK                           | 3.135    | 3.3  | 3.465   | V     |

| Input High Voltage           | V <sub>IH</sub> |                               | 0.65     |      |         | V     |

| Input Low Voltage            | V <sub>IL</sub> |                               |          |      | 0.35VDD | V     |

| Output High Voltage*         | V <sub>OH</sub> | $I_{OH} = -2 \text{ mA}, 27M$ | VDD-0.45 |      |         | V     |

| Output Low Voltage*          | V <sub>OL</sub> | I <sub>OL</sub> = 2 mA, 27M   |          |      | 0.45    | V     |

| Output High Voltage*         | V <sub>OH</sub> | I <sub>OH</sub> = -2 mA, CLK  | VDD-0.45 |      |         | V     |

| Output Low Voltage*          | V <sub>OL</sub> | I <sub>OL</sub> = 2 mA, CLK   |          |      | 0.4     | V     |

| IDD Operating Supply Current |                 | No load                       |          | 15   | 22      | mA    |

| Input Capacitance            |                 |                               |          | 4    |         | pF    |

<sup>\*</sup> Note: Guaranteed by design.

# **AC Electrical Characteristics-CLK**

**VDD=1.8 V \pm 5\%, VDDO = 3.3 V**, Ambient Temperature -40 to  $+85^{\circ}$  C, unless stated otherwise

| Parameter                                        | Symbol           | Conditions | Min. | Тур.     | Max. | Units |

|--------------------------------------------------|------------------|------------|------|----------|------|-------|

| Output Frequency                                 | F <sub>OUT</sub> |            | 9    | See Page | 2    | MHz   |

| Frequency Synthesis Error                        |                  |            | -50  |          | 50   | ppm   |

| Output Clock Rise Time                           | t <sub>OR</sub>  | 80% to 20% |      | 1        |      | ns    |

| Output Clock Fall Time                           | t <sub>OF</sub>  | 20% to 80% |      | 1        |      | ns    |

| Output Clock Duty Cycle t <sub>OD</sub>          |                  | VDD/2      | 45   | 50       | 55   | %     |

| Short Term Cycle-to-Cycle Jitter t <sub>ja</sub> |                  | CLK output |      | 75       | 100  | ps    |

| One Sigma Clock Period Jitter                    |                  | CLK output |      | 15       |      | ps    |

| Long Term Jitter                                 |                  | CLK output |      | TBD      |      | ps    |

| Aging                                            |                  | First year |      |          | 5    | ppm   |

| Power-up Time                                    |                  |            |      | 10       | 45   | ms    |

Note: Measured with a 7pF load.

# **AC Electrical Characteristics-27M**

**VDD=1.8 V ±5%,**, Ambient Temperature -40 to +85° C, unless stated otherwise

| Parameter                                        | Symbol           | Conditions | Min. | Тур. | Max. | Units |

|--------------------------------------------------|------------------|------------|------|------|------|-------|

| Output Frequency                                 | F <sub>OUT</sub> |            |      | 27   |      | MHz   |

| Frequency Synthesis Error                        |                  |            | -50  |      | 50   | ppm   |

| Output Clock Rise Time                           | t <sub>OR</sub>  | 80% to 20% |      | 1    |      | ns    |

| Output Clock Fall Time t                         |                  | 20% to 80% |      | 1    |      | ns    |

| Output Clock Duty Cycle t <sub>OD</sub>          |                  | VDD/2      | 45   | 50   | 55   | %     |

| Short Term Cycle-to-Cycle Jitter t <sub>ja</sub> |                  | 27M        |      | 50   | 75   | ps    |

| One Sigma Clock Period Jitter t <sub>is</sub>    |                  | 27M        |      | 15   |      | ps    |

| Long Term Jitter                                 |                  | 27M        |      | TBD  | TBD  | ps    |

| Aging                                            |                  | First year |      |      | TBD  | ppm   |

| Power-up Time                                    |                  |            |      | 10   | 45   | ms    |

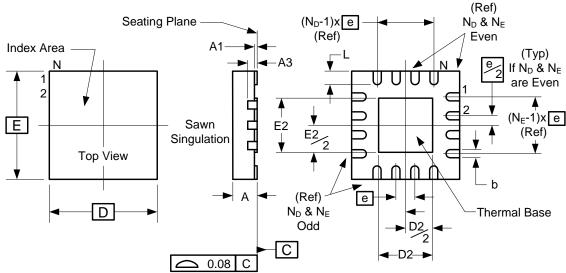

### Package Outline and Package Dimensions (16-pin QFN)

Package dimensions are kept current with JEDEC Publication No. 95

|                | Millin      | neters   |  |

|----------------|-------------|----------|--|

| Symbol         | Min         | Max      |  |

| Α              | 0.80        | 1.00     |  |

| A1             | 0           | 0.05     |  |

| A3             | 0.20 Re     | eference |  |

| b              | 0.18        | 0.30     |  |

| е              | 0.50 BASIC  |          |  |

| N              | 16          |          |  |

| $N_D$          | 4           |          |  |

| N <sub>E</sub> |             | 4        |  |

| D x E BASIC    | 3.00 x 3.00 |          |  |

| D2             | 1.55        | 1.80     |  |

| E2             | 1.55        | 1.80     |  |

| L              | 0.30        | 0.50     |  |

# **Ordering Information**

| Part / Order Number | Marking | Shipping Packaging | Package    | Temperature   |

|---------------------|---------|--------------------|------------|---------------|

| 5V80023-XXXNLG      | TBD     | Tray               | 16-pin QFN | 0 to +70° C   |

| 5V80023-XXXNLG8     |         | Tape and Reel      | 16-pin QFN | 0 to +70° C   |

| 5V80023-XXXNLGI     |         | Tray               | 16-pin QFN | -40 to +85° C |

| 5V80023-XXXNLGI8    |         | Tape and Reel      | 16-pin QFN | -40 to +85° C |

#### See table on page 2 for specific -XXX orderable part numbers.

### "G"after the two-letter package code are the Pb-free configuration and are RoHS compliant.

While the information presented herein has been checked for both accuracy and reliability, Integrated Device Technology (IDT) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by IDT. IDT reserves the right to change any circuitry or specifications without notice. IDT does not authorize or warrant any IDT product for use in life support devices or critical medical instruments.

# **Revision History**

| Rev. | Originator | Date     | Description of Change                                                                                                                                                                                                                                             |

|------|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Α    | K.B.       | 07/12/11 | Initial datasheet release.                                                                                                                                                                                                                                        |

| В    | K.B.       | 10/21/11 | <ol> <li>Added 1.8V to 3.3 VDDO for CLK to Features</li> <li>Added Power Supply Voltage (VDDO) spec to recommended Operating Conditions.</li> <li>Updated DC char table.</li> <li>Updated AC char table for CLK.</li> <li>Added AC char table for 27M.</li> </ol> |

| С    | J.C.       | 02/03/12 | <ol> <li>Updated Features bullets</li> <li>Updated minimum output voltage spec from 1.71V to 3.135V</li> <li>Updated IDD Operating Supply Current Typ. and Max. values</li> <li>Updated Short Term C-C Jitter Typ. and Max. values</li> </ol>                     |

| D    | J.C.       | 02/23/12 | Update "CLK Output Frequency/Part Number Tree" table by removing erroneous/invalid part numbers and updating frequencies                                                                                                                                          |

|      |            |          |                                                                                                                                                                                                                                                                   |

# Innovate with IDT and accelerate your future networks. Contact:

www.IDT.com

For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775 For Tech Support

www.idt.com/go/clockhelp

#### **Corporate Headquarters**

Integrated Device Technology, Inc. www.idt.com