# CrystalFree M Solid-State Oscillator Ultra Low Power Oscillators

3CN

# PRELIMINARY DATA SHEET

#### **Features**

■ Frequency Range: 4 to 133 MHz Output Type: **CMOS** • Frequency Tolerance: ± 100 ppm Supply Voltage: 1.8 to 3.3 V Power Consumption: 1.9 mA (1.8 V)

Standby Current: < 1 uA

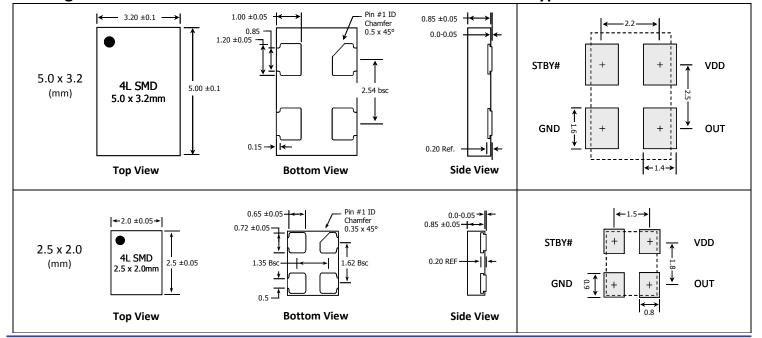

■ Standard Package: 5.0 x 3.2 x 0.85 mm

2.5 x 2.0 x 0.85 mm

Operating Temperature: 0 to 70 °C,  $\,$  -20 to 70 °C

# **Specification**

| Parameter                    | Symbol                           | Specifications                         |                 | Conditions |                                                                          |                                                                        |         |    |        |    |       |        |          |

|------------------------------|----------------------------------|----------------------------------------|-----------------|------------|--------------------------------------------------------------------------|------------------------------------------------------------------------|---------|----|--------|----|-------|--------|----------|

| Supply Voltage               | VDD                              | 1.8 V± 5%                              | 2.5 V±10%       | 3.3 V±10%  | Nom                                                                      | Nominal ± tolerance                                                    |         |    |        |    |       |        |          |

| Frequency Stability          | F <sub>STB</sub>                 |                                        | ± 100 ppm       |            | Total                                                                    | Total Frequency Stability*                                             |         |    |        |    |       |        |          |

| Supply Current               | IDD                              | 1.9 mA                                 | 2.0 mA          | 2.2 mA     | Typic                                                                    | Typical; No load condition; 75 MHz                                     |         |    |        |    |       |        |          |

| Quiescent Current            | I <sub>STBY</sub>                |                                        | 1 uA            |            | Maxi                                                                     | Maximum; STBY# = GND                                                   |         |    |        |    |       |        |          |

| Input LOW/HIGH level         | V <sub>IL</sub> /V <sub>IH</sub> | 0.3 VDD (max) /0.7 VDD (min)           |                 |            | At STBY# pin                                                             |                                                                        |         |    |        |    |       |        |          |

| Output LOW/HIGH level        | $V_{OL}$                         | 0.1 VD                                 | D (max) / 0.9 V | DD (min)   | I <sub>OL</sub> = -                                                      | I <sub>OL</sub> = -1 mA / I <sub>OH</sub> = 1 mA                       |         |    |        |    |       |        |          |

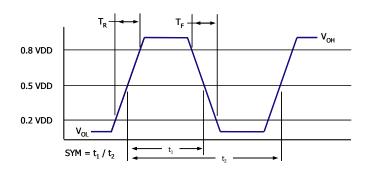

| Rise/Fall Time               | $T_R/T_F$                        | 1.6 ns                                 | 1.2 ns          | 1.0 ns     | Maxi                                                                     | Maximum; 20% to 80% x VDD; Output load (C <sub>L</sub> ) = 4 pF        |         |    |        |    |       |        |          |

| Cumama at mi                 | SYM                              | 45% / 55%                              |                 |            | Worst case; output frequencies ≤ 100 MHz                                 |                                                                        |         |    |        |    |       |        |          |

| Symmetry                     | 31101                            | 40% / 60%                              |                 |            | Worst case; output frequencies > 100 MHz                                 |                                                                        |         |    |        |    |       |        |          |

| Start-up time                | T <sub>ST</sub>                  | 400 us (max)                           |                 |            | Output valid time after VDD meets the specified range & STBY# transition |                                                                        |         |    |        |    |       |        |          |

| Period Jitter RMS            | $PJ_{RMS}$                       | 17 ps                                  | 6 ps            | 5 ps       | Outp                                                                     | Output load (C <sub>L</sub> ) = 4 pF; 75 MHz; measured over 10K cycles |         |    |        |    |       |        |          |

| Cycle to Cycle Jitter(Pk-Pk) | $CCJ_{PP}$                       | 120 ps                                 | 50 ps           | 40 ps      | Outp                                                                     | Output load (C <sub>L</sub> ) = 4 pF; 75 MHz; measured over 1K cycles  |         |    |        |    |       |        |          |

|                              |                                  |                                        |                 |            |                                                                          |                                                                        |         |    |        |    |       |        |          |

|                              | F <sub>OUT</sub>                 | 4                                      | 4.096           | 5          | 6                                                                        | 6.144                                                                  | 7.3728  | 8  | 10     | 12 | 12.5  | 12.288 | 14.31818 |

| Output Frequency             |                                  | 15                                     | 16              | 18.432     | 19.44                                                                    | 20                                                                     | 22.5972 | 24 | 24.576 | 25 | 30    | 33     | 33.333   |

|                              |                                  | 36                                     | 37.5            | 40         | 48                                                                       | 49.152                                                                 | 50      | 60 | 62.5   | 66 | 66.66 | 72     | 74.25    |

|                              |                                  | 75                                     | 80              | 98.304     | 100                                                                      | 125                                                                    | 133     |    |        |    |       |        |          |

|                              |                                  | Contact IDT for additional frequencies |                 |            |                                                                          |                                                                        |         |    |        |    |       |        |          |

Note: Above specifications are typical at room temperature (25°C) unless otherwise specified.

## **Package Outline and Dimensions**

## **Typical PCB Land Pattern**

<sup>\*</sup> Inclusive of initial frequency accuracy, operating temperature range, supply variation, load variation, 3 times solder reflow, shock, vibration and 10 years aging at 25°C.

## **Absolute Maximum Ratings**

Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these or under any condition beyond those listed in the operating specifications is not implied. Exposure to absolute maximum rated conditions may affect product reliability.

| Item                | Maximum Absolute Rating |  |  |  |

|---------------------|-------------------------|--|--|--|

| VDD                 | 4.6 V                   |  |  |  |

| STBY#               | -0.5 V to VDD + 0.5 V   |  |  |  |

| OUT                 | -0.5 V to VDD + 0.5 V   |  |  |  |

| Storage Temperature | -65°C to 150°C          |  |  |  |

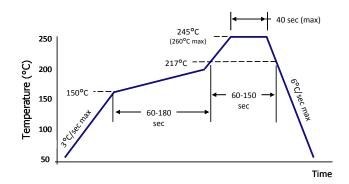

### **Solder Reflow Profile**

# **Pin Descriptions**

| Pin#                                                     | Name             | Description                                     |  |  |  |  |

|----------------------------------------------------------|------------------|-------------------------------------------------|--|--|--|--|

| 1                                                        | STBY#            | Standby Mode <sup>1</sup> (0 = Output Disabled) |  |  |  |  |

| 2                                                        | GND              | Ground                                          |  |  |  |  |

| 3                                                        | OUT <sup>2</sup> | CMOS Output                                     |  |  |  |  |

| 4 VDD                                                    |                  | Power                                           |  |  |  |  |

| Pulled high internally                                   |                  |                                                 |  |  |  |  |

| 2. Weak pull down to GND during STBY# enable and startup |                  |                                                 |  |  |  |  |

#### **Output Waveform**

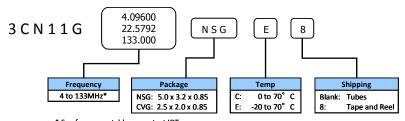

# **Ordering Information**

| Package | Minimum Orde | er Quantity (MOQ) | Factory Order Increment (FOI) |                 |  |  |

|---------|--------------|-------------------|-------------------------------|-----------------|--|--|

| Suffix  | T & R        | Bulk              | T & R                         | Bulk            |  |  |

| NSG     | 2500         | 1260 (18 Tubes)   | 2500                          | 1260 (18 Tubes) |  |  |

| CVG     | 3000         | 1250 (Canister)   | 3000                          | 1250 (Canister) |  |  |

|         |              |                   |                               |                 |  |  |

<sup>\*</sup> See frequency table or contact IDT

6024 Silver Creek Valley Road San Jose, California 95138

#### Sales

800-345-7015 (inside USA) +1 408-284-8200 (outside USA) Fax: 408-284-2775

#### **Technical Support**

crystalfreetechsupport@idt.com +1 408-360-5656

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications described herein at any time and at IDT's sole discretion. All information in this document, including descriptions of product features and performance, is subject to change without notice. Performance specifications and the operating parameters of the described products are determined in the independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's product are not intended for use in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are registered trademarks of IDT. Other trademarks and service marks used herein, including protected names, logos and designs, are the property of IDT or their respective third party owners.

Copyright 2010, 2011. All rights reserved.