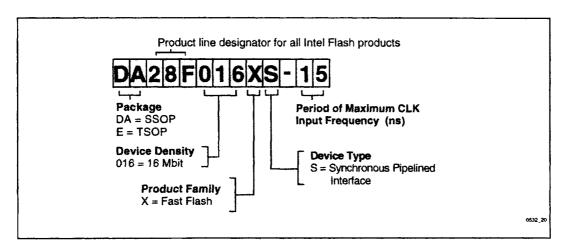

# 28F016XS 16-MBIT (1 MBIT x 16, 2 MBIT x 8) SYNCHRONOUS FLASH MEMORY

- Effective Zero Wait-State Performance up to 33 MHz

- Synchronous Pipelined Reads

- SmartVoltage Technology

- User-Selectable 3.3V or 5V V<sub>CC</sub>

- User-Selectable 5V or 12V V<sub>PP</sub>

- 0.33 MB/sec Write Transfer Rate

- Configurable x8 or x16 Operation

- 56-Lead TSOP and SSOP Type I Package

- Backwards-Compatible with 28F008SA Command-Set

- 2 µA Typical Deep Power-Down

- 1 mA Typical Active I<sub>CC</sub> Current in Static Mode

- 16 Separately-Erasable/Lockable

128-Kbyte Blocks

- 1 Million Erase Cycles per Block

- State-of-the-Art 0.6 µm ETOX<sup>™</sup> IV Flash Technology

Intel's 28F016XS 16-Mbit flash memory is a revolutionary architecture which is the ideal choice for designing truly revolutionary high-performance products. Combining very high read performance with the intrinsic nonvolatility of flash memory, the 28F016XS eliminates the traditional redundant memory paradigm of shadowing code from a slow nonvolatile storage source to a faster execution memory, such as DRAM, for improved system performance. The innovative capabilities of the 28F016XS enable the design of direct-execute code and mass storage data/file flash memory systems.

The 28F016XS is the highest performance high-density nonvolatile read/program flash memory solution available today. Its synchronous pipelined read interface, flexible  $V_{\rm CC}$  and  $V_{\rm PP}$  voltages, extended cycling, fast program and read performance, symmetrically-blocked architecture, and selective block locking provide a highly flexible memory component suitable for resident flash component arrays on the system board or SIMMs. The synchronous pipelined interface and x8/x16 architecture of the 28F016XS allow easy interface with minimal glue logic to a wide range of processors/buses, providing effective zero wait-state read performance up to 33 MHz. The 28F016XS's dual read voltage allows the same component to operate at either 3.3V or 5.0V  $V_{\rm CC}$ . Programming voltage at 5V  $V_{\rm PP}$  inimizes external circuitry in minimal-chip, space critical designs, while the 12.0V  $V_{\rm PP}$  option maximizes program/erase performance. Its high read performance combined with flexible block locking enable both storage and execution of operating systems/application software and fast access to large data tables. The 28F016XS is manufactured on Intel's 0.6  $\mu$ m ETOX IV process technology.

November 1996

Order Number: 290532-004

|  | , |  |  |

|--|---|--|--|

|  |   |  |  |

### **REVISION HISTORY**

| Number | Description                                                                                                                                                                                                                                                                                                               |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -001   | Original Version                                                                                                                                                                                                                                                                                                          |

| -002   | Removed support of the following features:  • All page buffer operations (read, write, programming, Upload Device Information)  • Command queuing  • Software Sleep and Abort  • Erase all Unlocked Blocks and Two-Byte Write  • RY/BY# Configuration as part of the Device Configuration command                         |

|        | Changed definition of "NC." Removed "No internal connection to die" from description.                                                                                                                                                                                                                                     |

|        | Added "xx" to Upper Byte of Command (Data) Definition in Sections 4.3 and 4.4.                                                                                                                                                                                                                                            |

|        | Modified parameters "V" and "I" of Section 5.1 to apply to "NC" pins.                                                                                                                                                                                                                                                     |

|        | Increased I <sub>PPR</sub> (V <sub>PP</sub> Read Current) for V <sub>PP</sub> > $V_{CC}$ to 200 $\mu$ A at $V_{CC}$ = 3.3V/5.0V.                                                                                                                                                                                          |

|        | Changed $V_{CC}$ = 5.0V DC Characteristics (Section 5.5) marked with Note 1 to indicate that these currents are specified for a CMOS rise/fall time (10% to 90%) of <5 ns and a TTL rise/fall time of <10 ns.                                                                                                             |

|        | Corrected t <sub>PHCH</sub> (RP# High to CLK) to be a "Min" specification at V <sub>CC</sub> = 3.3V/5.0V.                                                                                                                                                                                                                 |

|        | Corrected the graphical representation of twhCH and teHCH in Figures 15 and 16.                                                                                                                                                                                                                                           |

|        | Increased Typical "Byte/Word Program Times" ( $t_{WHRH1A}/t_{WHRH1B}$ ) for $V_{PP}$ = 5.0V (Sec. 5.13): $t_{WHRH1A}$ from 16.5 $\mu$ s to 29.0 $\mu$ s and $t_{WHRH1B}$ from 24.0 $\mu$ s to 35.0 $\mu$ s at $V_{CC}$ = 3.3V                                                                                             |

|        | twhRH1A from 11.0 $\mu$ s to 20.0 $\mu$ s and twHRH1B from 16.0 $\mu$ s to 25.0 $\mu$ s at $V_{CC}$ = 5.0V.                                                                                                                                                                                                               |

|        | Increased Typical "Block Program Times" ( $t_{WHRH2}/t_{WHRH3}$ ) for V <sub>PP</sub> = 5.0V (Section 5.13): $t_{WHRH2}$ from 2.2 sec to 3.8 sec and $t_{WHRH3}$ from 1.6 sec to 2.4 sec at V <sub>CC</sub> = 3.3V $t_{WHRH2}$ from 1.6 sec to 2.8 sec and $t_{WHRH3}$ from 1.2 sec to 1.7 sec at V <sub>CC</sub> = 5.0V. |

|        | Changed "Time from Erase Suspend Command to WSM Ready" spec name to "Erase Suspend Latency Time to Read;" Modified typical values and Added Min/Max values at V <sub>CC</sub> =3.3/5.0V and V <sub>PP</sub> =5.0/12.0V (Section 5.13).                                                                                    |

|        | Minor cosmetic changes throughout document.                                                                                                                                                                                                                                                                               |

| -003   | Added 3/5# pin to Pinout Configuration (Figure 2), Product Overview (Section 1.1) and Lead Descriptions (Section 2.1)                                                                                                                                                                                                     |

|        | Modified Block Diagram (Figure 1): Removed Address Counter; Added 3/5# pin                                                                                                                                                                                                                                                |

|        | Added 3/5# pin to Test Conditions of Icos Specifications                                                                                                                                                                                                                                                                  |

|        | Added 3/5# pin (Y) to Timing Nomenclature (Section 5.6)                                                                                                                                                                                                                                                                   |

|        | Removed Note 7 of Section 5.7                                                                                                                                                                                                                                                                                             |

|        | Modified Device Configuration Code: Incorporated RY/BY# Configuration (Level Mode support ONLY)                                                                                                                                                                                                                           |

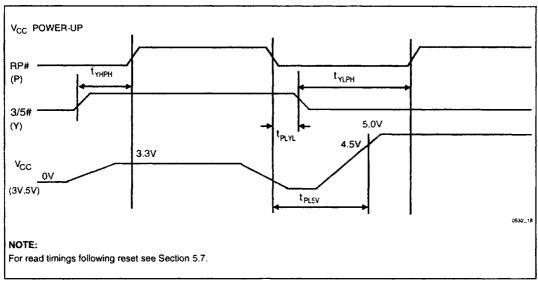

|        | Modified Power-Up and Reset Timings (Section 5.10) to include 3/5# pin: Removed t <sub>5VPH</sub> and t <sub>3VPH</sub> specifications; Added t <sub>PLYL</sub> , t <sub>PLYH</sub> , t <sub>YLPH</sub> , and t <sub>YHPH</sub> specifications                                                                            |

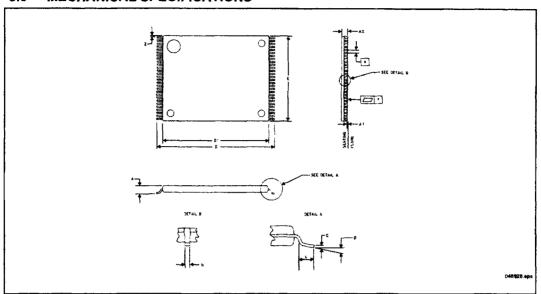

|        | Added SSOP pinout (Figure 2) and Mechanical Specifications                                                                                                                                                                                                                                                                |

|        | Corrected TSOP Mechanical Specification A1 from 0.50 mm to 0.050 mm (Section 6.0)                                                                                                                                                                                                                                         |

|        | Minor cosmetic changes throughout document.                                                                                                                                                                                                                                                                               |

### **REVISION HISTORY** (Continued)

| Number | Description                                                                   | iption |  |  |  |  |  |

|--------|-------------------------------------------------------------------------------|--------|--|--|--|--|--|

| -004   | Require all V <sub>CC</sub> Tolerences to be within 5% of Operational Voltage |        |  |  |  |  |  |

|        | IPPES Is Pushed to 200 µA from 50 Max                                         |        |  |  |  |  |  |

|        | I <sub>CCD</sub> Is Pushed to 10 μA from 5 Max                                |        |  |  |  |  |  |

|        | Updated tayay at 3.3V                                                         |        |  |  |  |  |  |

|        | Updated teleh at 3.3V and 5.0V                                                |        |  |  |  |  |  |

#### 1.0 INTRODUCTION

The documentation of the Intel 28F016XS Flash memory device includes this datasheet, a detailed user's manual, a number of application notes and design tools, all of which are referenced in Appendix B.

The datasheet is intended to give an overview of the chip feature-set and of the operating AC/DC specifications. The 16-Mbit Flash Product Family User's Manual provides complete descriptions of the user modes, system interface examples and detailed descriptions of all principles of operation. It also contains the full list of software algorithm flowcharts, and a brief section on compatibility with the Intel 28F008SA.

Significant 28F016XS feature revisions occurred between datasheet revisions 290532-001 and 290532-002. These revisions center around removal of the following features:

- All page buffer operations (read, write, programming, Upload Device Information)

- Command queuing

- Software Sleep and Abort

- · Erase all Unlocked Blocks and Two-Byte Write

- RY/BY# Configuration options

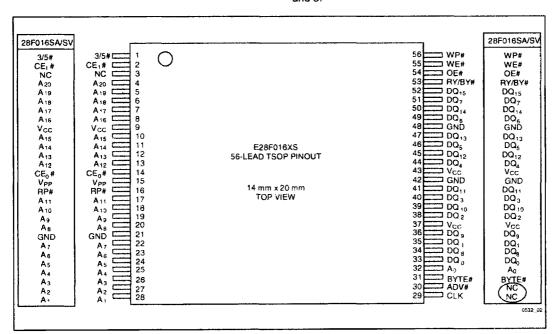

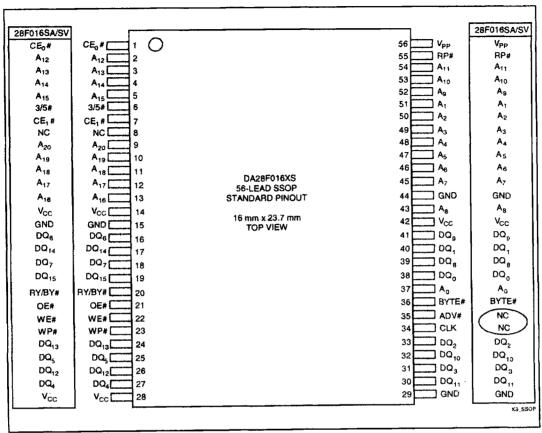

In addition, a significant 28F016XS change occurred between datasheet revisions 290532-002 and 290532-003. This change centers around the addition of a 3/5# pin to the device's pinout configuration. Figures 2 and 3 show the 3/5# pin assignment for the TSOP and SSOP Type I packages.

Intel recommends that all customers obtain the latest revisions of 28F016XS documentation.

#### 1.1 Product Overview

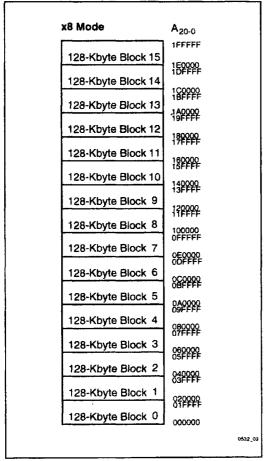

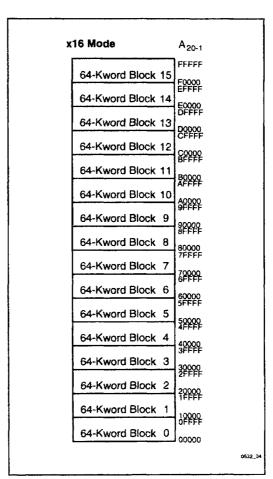

The 28F016XS is a high-performance, 16-Mbit (16,777,216-bit) block erasable nonvolatile random access memory organized as either 1 Mword x 16 or 2 Mbyte x 8, subdivided into even and odd banks. Address  $A_1$  makes the bank selection. The 28F016XS includes sixteen 128-Kbyte (131,072 byte) blocks or sixteen 64-Kword (65,536 word) blocks. Chip memory maps for x8 and x16 modes are shown in Figures 4 and 5.

The implementation of a new architecture, with many enhanced features, will improve the device operating characteristics and result in greater product reliability and ease-of-use as compared to other flash memories. Significant features of the 28F016XS as compared to previous asynchronous flash memories include:

- Synchronous Pipelined Read Interface

- Significantly Improved Read and Program Performance

- SmartVoltage Technology

- Selectable 3.3V or 5.0 V<sub>CC</sub>

- Selectable 5.0V or 12.0 Vpp

- Block Program/Erase Protection

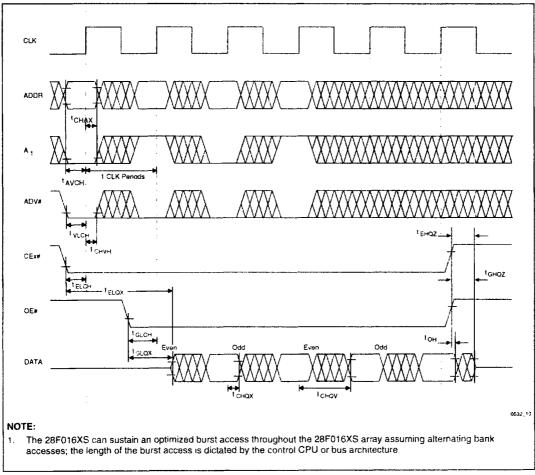

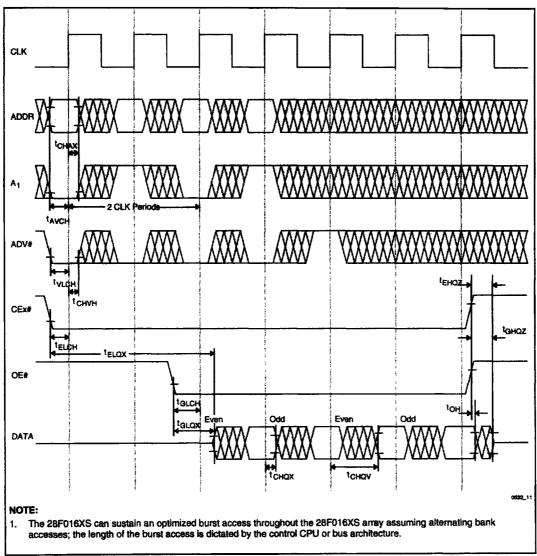

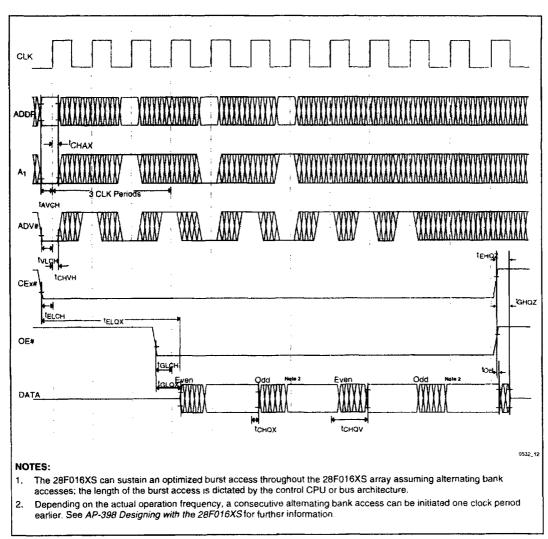

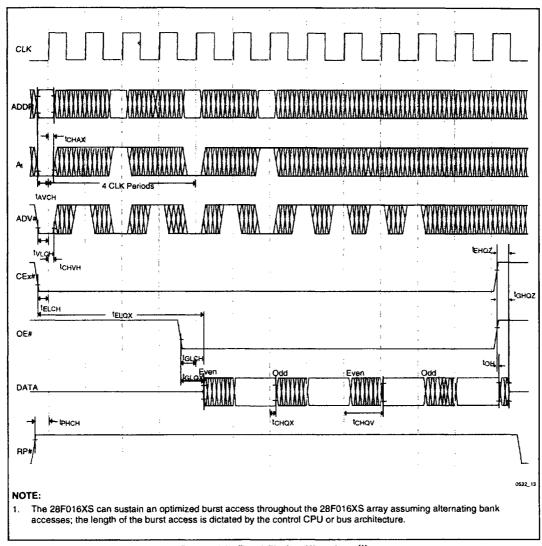

The 28F016XS's synchronous pipelined interface dramatically raises read performance far beyond previously attainable levels. Addresses are synchronously latched and data is read from a 28F016XS bank every 30 ns (5V Vcc, SFI Configuration = 2). This capability translates to zero wait-state reads at clock rates up to 33 MHz at 5V V<sub>CC</sub>, after an initial address pipeline fill delay and assuming even and odd banks within the flash memory are alternately accessed. Data is latched and driven valid 20 ns (t<sub>CHQV</sub>) after a rising CLK edge. The 28F016XS is capable of operating up to 50 MHz (5V  $V_{\rm CC}$ ); its programmable SFI Configuration enables system design flexibility, optimizing the 28F016XS to a specific system clock frequency. See Section 4.9, SFI Configuration Table, for specific SFI Configurations for given operating frequencies.

The SFI Configuration optimizes the 28F016XS for a wide range of system operating frequencies. The default SFI Configuration is 4, which allows system boot from the 28F016XS at any frequency up to 50 MHz at 5V V<sub>CC</sub>. After initiating an access, data is latched and begins driving on the data outputs after a CLK count corresponding to the SFI Configuration has elapsed. The 28F016XS will hold data valid until CE# or OE# is deactivated or a CLK count corresponding to the SFI Configuration for a subsequent access has elapsed.

The CLK and ADV# inputs, new to the 28F016XS in comparison to previous flash memories, control address latching and device synchronization during read operations. The CLK input controls the device latencies, times out the SFI Configuration counter and synchronizes data outputs. ADV# indicates the presence of a valid address on the 28F016XS

address inputs. During read operations, addresses are latched and accesses are initiated on a rising CLK edge in conjunction with ADV# low. Both CLK and ADV# are ignored by the 28F016XS during command/data write sequences.

28F016XS The incorporates SmartVoltage technology, providing  $V_{CC}$  operation at both 3.3V and 5.0V and program and erase capability at  $V_{PP} = 12.0V$  or 5.0V. Operating at  $V_{CC} = 3.3V$ , the 28F016XS consumes less than one half the power consumption at 5.0V  $V_{CC}$ , while 5.0V  $V_{CC}$  provides highest read performance capability. VPP operation at 5.0V eliminates the need for a separate 12.0V converter, while the V<sub>PP</sub> = 12.0V option maximizes program/erase performance. In addition to the flexible program and erase voltages, the dedicated V<sub>PP</sub> gives complete code protection with V<sub>PP</sub> ≤ V<sub>PPLK</sub>.

A 3/5# input pin configures the device's internal circuitry for optimal 3.3V or 5.0V read/program operation

A Command User Interface (CUI) serves as the system interface between the microprocessor or microcontroller and the internal memory operation.

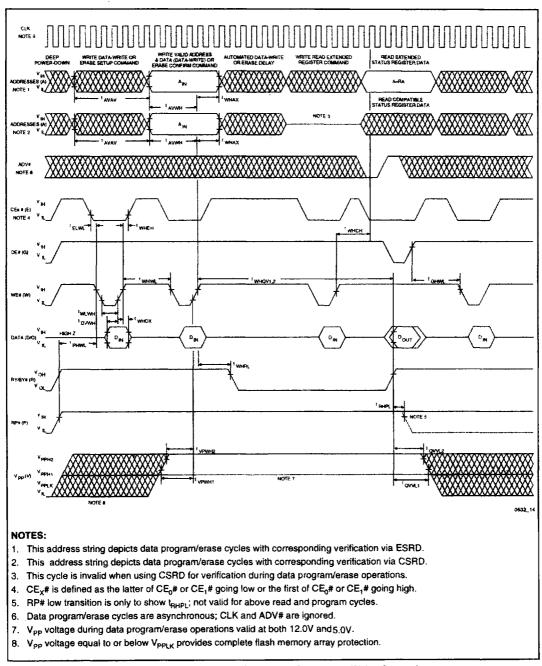

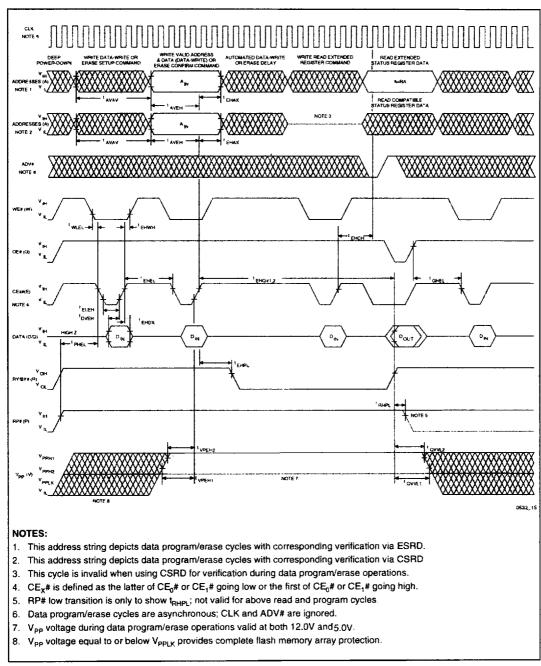

Internal Algorithm Automation allows program and block erase operations to be executed using a Two-Write command sequence to the CUI in the same way as the 28F008SA 8-Mbit FlashFile<sup>TM</sup> memory.

Software locking of memory blocks is an added feature of the 28F016XS as compared to the 28F008SA. The 28F016XS provides selectable block locking to protect code or data such as direct-executable operating systems or application code. Each block has an associated nonvolatile lock-bit which determines the lock status of the block. In addition, the 28F016XS has a master Write Protect pin (WP#) which prevents any modifications to memory blocks whose lock-bits are set.

Writing of memory data is performed in either byte or word increments, typically within 6  $\mu$ s at 12.0V  $V_{pp}$ , which is a 33% improvement over the 28F008SA. A block erase operation erases one of the 16 blocks in typically 1.2 sec, independent of the other blocks.

Each block can be written and erased a minimum of '00,000 cycles. Systems can achieve one million

Block Erase Cycles by providing wear-leveling algorithms and graceful block retirement. These techniques have already been employed in many flash file systems and hard disk drive designs.

All operations are started by a sequence of Write commands to the device. Three Status Registers (described in detail later in this datasheet) and a RY/BY# output pin provide information on the progress of the requested operation.

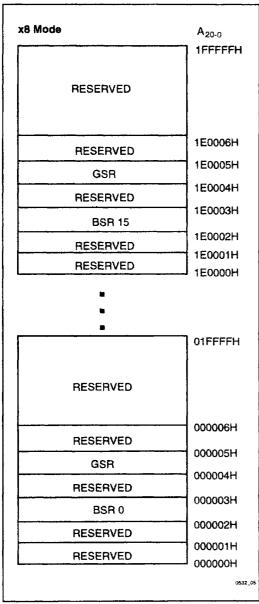

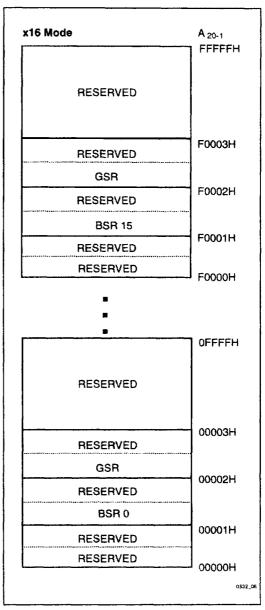

The following Status Registers are used to provide device and WSM operation information to the user:

- A Compatible Status Register (CSR) which is 100% compatible with the 28F008SA FlashFile memory Status Register. The CSR, when used alone, provides a straightforward upgrade capability to the 28F016XS from a 28F008SAbased design.

- A Global Status Register (GSR) which also informs the system of overall Write State Machine (WSM) status.

- 16 Block Status Registers (BSRs) which provide block-specific status information such as the block lock-bit status.

The GSR and BSR memory maps for Byte-Wide and Word-Wide modes are shown in Figures 5 and 6.

The 28F016XS incorporates an open drain RY/BY# output pin. This feature allows the user to OR-tie many RY/BY# pins together in a multiple memory configuration such as a Resident Flash Array.

The 28F016XS also incorporates a dual chipenable function with two input pins, CE<sub>0</sub># and CE<sub>1</sub>#. These pins have exactly the same functionality as the regular chip-enable pin, CE#, on the 28F008SA. For minimum chip designs, CE<sub>1</sub># may be tied to ground and system logic may use CE<sub>0</sub># as the chip enable input. The 28F016XS uses the logical combination of these two signals to enable or disable the entire chip. Both CE<sub>0</sub># and CE<sub>1</sub># must be active low to enable the device. If either one becomes inactive, the chip will be disabled. This feature, along with the open drain RY/BY# pin, allows the system designer to reduce the number of control pins used in a large array of 16-Mbit devices.

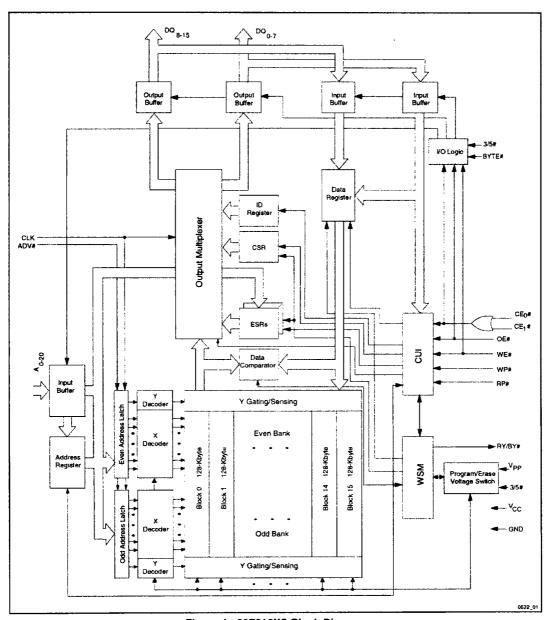

Figure 1. 28F016XS Block Diagram

Architectural Evolution Includes Synchronous Pipelined Read Interface,

SmartVoltage Technology, and Extended Status Registers

The BYTE# pin allows either x8 or x16 read/programs to the 28F016XS. BYTE# at logic low selects 8-bit mode with address  $A_0$  selecting between low byte and high byte. On the other hand, BYTE# at logic high enables 16-bit operation with address  $A_0$  becoming the lowest order address and address  $A_0$  is not used (don't care). A device block diagram is shown in Figure 1.

The 28F016XS incorporates an Automatic Power Saving (APS) feature, which substantially reduces the active current when the device is in static mode of operation (addresses not switching). In APS mode, the typical I<sub>CC</sub> current is 1 mA at 5.0V (3 mA at 3.3V).

A deep power-down mode of operation is invoked when the RP# (called PWD# on the 28F008SA) pin transitions low. This mode brings the device power consumption to less than 2.0  $\mu$ A, typically, and provides additional write protection by acting as a device reset pin during power transitions. A reset time of 300 ns (5V Vcc) is required from RP# switching high before latching an address into the

28F016XS. In the deep power-down state, the WSM is reset (any current operation will abort) and the CSR, GSR and BSR registers are cleared.

A CMOS standby mode of operation is enabled when either CE $_0$ # or CE $_1$ # transitions high and RP# stays high with all input control pins at CMOS levels. In this mode, the device typically draws an  $I_{CC}$  standby current of 70  $\mu$ A at 5V  $V_{CC}$ .

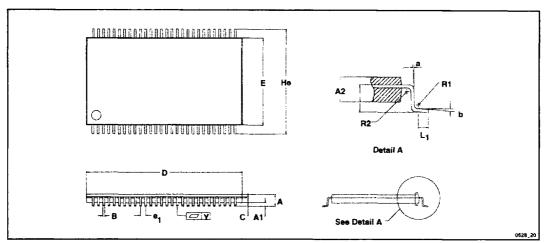

The 28F016XS is available in 56-Lead, 1.2 mm thick, 14 mm x 20 mm TSOP and 1.8 mm thick, 16 mm x 23.7 mm SSOP Type I packages. The form factor and pinout of these two packages allow for very high board layout densities.

#### 2.0 DEVICE PINOUT

The 28F016XS is pinout compatible with the 28F016SA/SV 16-Mbit FlashFile memory components, providing a performance upgrade path to the 28F016XS. The 28F016XS 56-Lead TSOP and SSOP pinout configurations are shown in Figures 2 and 3.

Figure 2. 28F016XS 56-Lead TSOP Pinout Configuration Shows Compatibility with the 28F016SA/SV, Allowing for Easy Performance Upgrades from Existing 16-Mbit Designs

Figure 3. 28F016XS 56-Lead SSOP Pinout Configuration Shows Compatibility with the 28F016SA/SV, Allowing for Easy Performance Upgrades from Existing 16-Mbit Designs

# 2.1 Lead Descriptions

| Symbol                               | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ao                                   | INPUT            | BYTE-SELECT ADDRESS: Selects between high and low byte when device is in x8 mode. This address is latched in x8 data programs and ignored in x16 mode (i.e., the A <sub>0</sub> input buffer is turned off when BYTE# is high).                                                                                                                                                                                                                                                                                   |

| Α1                                   | INPUT            | <b>BANK-SELECT ADDRESS:</b> Selects an even or odd bank in a selected block. A 128-Kbyte block is subdivided into an even and odd bank. $A_1 = 0$ selects the even bank and $A_1 = 1$ selects the odd bank, in both byte-wide mode and wordwide mode device configurations.                                                                                                                                                                                                                                       |

| A <sub>2</sub> -A <sub>16</sub>      | INPUT            | <b>WORD-SELECT ADDRESSES:</b> Select a word within one 128-Kbyte block. Address $A_1$ and $A_{7-16}$ select 1 of 2048 rows, and $A_{2-6}$ select 16 of 512 columns. These addresses are latched during both data reads and programs.                                                                                                                                                                                                                                                                              |

| A <sub>17</sub> A <sub>20</sub>      | INPUT            | BLOCK-SELECT ADDRESSES: Select 1 of 16 erase blocks. These addresses are latched during data programs, erase and lock-block operations.                                                                                                                                                                                                                                                                                                                                                                           |

| DQ <sub>0</sub> DQ <sub>7</sub>      | INPUT/<br>OUTPUT | LOW-BYTE DATA BUS: Inputs data and commands during CUI write cycles. Outputs array, identifier or status data in the appropriate read mode. Floated when the chip is de-selected or the outputs are disabled.                                                                                                                                                                                                                                                                                                     |

| DQ <sub>8</sub> -DQ <sub>15</sub>    | INPUT/<br>OUTPUT | HIGH-BYTE DATA BUS: Inputs data during x16 data program operations. Outputs array or identifier data in the appropriate read mode; not used for Status Register reads. Outputs floated when the chip is de-selected, the outputs are disabled (OE# = V <sub>IH</sub> ) or BYTE# is driven active.                                                                                                                                                                                                                 |

| CE <sub>0</sub> #, CE <sub>1</sub> # | INPUT            | CHIP ENABLE INPUTS: Activate the device's control logic, input buffers, decoders and sense amplifiers. With either CE <sub>0</sub> # or CE <sub>1</sub> # high, the device is de-selected and power consumption reduces to standby levels upon completion of any current data program or erase operations. Both CE <sub>0</sub> # and CE <sub>1</sub> # must be low to select the device.                                                                                                                         |

|                                      |                  | All timing specifications are the same for both signals. Device Selection occurs with the latter falling edge of $CE_0\#$ or $CE_1\#$ . The first rising edge of $CE_0\#$ or $CE_1\#$ disables the device.                                                                                                                                                                                                                                                                                                        |

| RP#                                  | INPUT            | RESET/POWER-DOWN: RP# low places the device in a deep power-down state. All circuits that consume static power, even those circuits enabled in standby mode, are turned off. When returning from deep power-down, a recovery time of tphch is required to allow these circuits to power-up. When RP# goes low, the current WSM operation is terminated, and the device is reset. All Status Registers return to ready, clearing all status flags. Exit from deep power-down places the device in read array mode. |

| OE#                                  | INPUT            | <b>OUTPUT ENABLE:</b> Drives device data through the output buffers when low. The outputs float to tri-state off when OE# is high. CE <sub>x</sub> # overrides OE#, and OE# overrides WE#.                                                                                                                                                                                                                                                                                                                        |

| WE#                                  | INPUT            | WRITE ENABLE: Controls access to the CUI, Data Register and Address Latch. WE# is active low, and latches both address and data (command or array) on its rising edge.                                                                                                                                                                                                                                                                                                                                            |

# 2.1 Lead Descriptions (Continued)

| Symbol          | Type                    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK             | INPUT                   | CLOCK: Provides the fundamental timing and internal operating frequency. CLK latches input addresses in conjunction with ADV#, times out the desired output SFI Configuration as a function of the CLK period, and synchronizes device outputs. CLK can be slowed or stopped with no loss of data or synchronization. CLK is ignored during program operations.                                                                |

| ADV#            | INPUT                   | ADDRESS VALID: Indicates that a valid address is present on the address inputs. ADV# low at the rising edge of CLK latches the address on the address inputs into the flash memory and initiates a read access to the even or odd bank depending on the state of A <sub>1</sub> . ADV# is ignored during program operations.                                                                                                   |

| RY/BY#          | OPEN<br>DRAIN<br>OUTPUT | <b>READY/BUSY:</b> Indicates status of the internal WSM. When low, it indicates that the WSM is busy performing an operation. RY/BY# high indicates that the WSM is ready for new operations, erase is suspended, or the device is in deep power-down mode. This output is always active (i.e., not floated to tri-state off when OE# or CE <sub>0</sub> #, CE <sub>1</sub> # are high).                                       |

| WP#             | INPUT                   | WRITE PROTECT: Erase blocks can be locked by writing a nonvolatile lock-bit for each block. When WP# is low, those locked blocks as reflected by the Block-Lock Status bits (BSR.6), are protected from inadvertent data programs or erases. When WP# is high, all blocks can be written or erased regardless of the state of the lock-bits. The WP# input buffer is disabled when RP# transitions low (deep power-down mode). |

| BYTE#           | INPUT                   | BYTE ENABLE: BYTE# low places device in x8 mode. All data is then input or output on DQ $_{0-7}$ , and DQ $_{8-15}$ float. Address A $_0$ selects between the high and low byte. BYTE# high places the device in x16 mode, and turns off the A $_0$ input buffer. Address A $_1$ then becomes the lowest order address.                                                                                                        |

| 3/5#            | INPUT                   | 3.3/5.0 VOLT SELECT: 3/5# high configures internal circuits for 3.3V operation. 3/5# low configures internal circuits for 5.0V operation.  NOTE:  Reading the array with 3/5# high in a 5.0V system could damage the device. Reference the power-up and reset timings (Section 5.10) for 3/5# switching delay to valid data.                                                                                                   |

| V <sub>PP</sub> | SUPPLY                  | PROGRAM/ERASE POWER SUPPLY (12.0V ± 0.6V, 5.0V ± 0.5V): For erasing memory array blocks or writing words/bytes into the flash array.  V <sub>PP</sub> = 5.0V ± 0.5V eliminates the need for a 12.0V converter, while the 12.0V ± 0.6V option maximizes program/erase performance.                                                                                                                                              |

|                 |                         | Successful completion of program and erase attempts is inhibited with $V_{PP}$ at or below 1.5V. Program and erase attempts with $V_{PP}$ between 1.5V and 4.5V, between 5.5V and 11.4V, and above 12.6V produce spurious results and should not be attempted.                                                                                                                                                                 |

| V <sub>CC</sub> | SUPPLY                  | DEVICE POWER SUPPLY (3.3V ± 5%, 5.0V ± 5%): To switch 3.3V to 5.0V (or vice versa), first ramp V <sub>CC</sub> down to GND, and then power to the new V <sub>CC</sub> voltage. Do not leave any power pins floating.                                                                                                                                                                                                           |

### 2.1 Lead Descriptions (Continued)

| Symbol | Туре   | Name and Function                                                         |  |

|--------|--------|---------------------------------------------------------------------------|--|

| GND    | SUPPLY | GROUND FOR ALL INTERNAL CIRCUITRY: Do not leave any ground pins floating. |  |

| NC     |        | NO CONNECT: Lead may be driven or left floating.                          |  |

#### 3.0 MEMORY MAPS

Figure 4. 28F016XS Memory Map (Byte-Wide Mode)

Figure 5. 28F016XS Memory Map (Word-Wide Mode)

### 3.1 Extended Status Register Memory Map

Figure 6. Extended Status Register Memory Map (Byte-Wide Mode)

Figure 7. Extended Status Register Memory Map (Word-Wide Mode)

### 4.0 BUS OPERATIONS, COMMANDS AND STATUS REGISTER DEFINITIONS

### 4.1 Bus Operations for Word-Wide Mode (BYTE# = V<sub>IH</sub>)

| Mode                                | Notes   | RP#             | CE <sub>0-1</sub> # | OE#             | WE#             | ADV#            | CLK | A <sub>1</sub>  | DQ <sub>0-15</sub> | RY/BY#          |

|-------------------------------------|---------|-----------------|---------------------|-----------------|-----------------|-----------------|-----|-----------------|--------------------|-----------------|

| Latch Read<br>Address               | 1,9,10  | V <sub>iH</sub> | V <sub>IL</sub>     | Х               | V <sub>IH</sub> | V <sub>IL</sub> | 1   | Х               | х                  | х               |

| Inhibit<br>Latching<br>Read Address | 1,9     | V <sub>IH</sub> | V <sub>IL</sub>     | Х               | V <sub>iH</sub> | V <sub>IH</sub> | 1   | Х               | х                  | ×               |

| Read                                | 1,2,7,9 | V <sub>IH</sub> | V <sub>IL</sub>     | V <sub>IL</sub> | V <sub>IH</sub> | Х               | 1   | Х               | D <sub>OUT</sub>   | X               |

| Output<br>Disable                   | 1,6,7,9 | V <sub>IH</sub> | V <sub>IL</sub>     | V <sub>IH</sub> | V <sub>IH</sub> | Х               | X   | Х               | High Z             | ×               |

| Standby                             | 1,6,7,9 | V <sub>iH</sub> | V <sub>IL</sub>     | Х               | Х               | Х               | Х   | Х               | High Z             | X               |

| Deep<br>Power-Down                  | 1,3     | V <sub>IL</sub> | ×                   | Х               | х               | х               | Х   | Х               | High Z             | V <sub>OH</sub> |

| Manufacturer<br>ID                  | 1,4,9   | V <sub>iH</sub> | V <sub>IL</sub>     | V <sub>IL</sub> | V <sub>IH</sub> | х               | 1   | V <sub>IL</sub> | 0089H              | V <sub>OH</sub> |

| Device ID                           | 1,4,8,9 | V <sub>IH</sub> | V <sub>IL</sub>     | V <sub>IL</sub> | VIH             | Х               | 1   | V <sub>IH</sub> | 66A8H              | V <sub>OH</sub> |

| Write                               | 1.5,6,9 | V <sub>IH</sub> | V <sub>iL</sub>     | V <sub>IH</sub> | V <sub>IL</sub> | Х               | Х   | Х               | D <sub>iN</sub>    | ×               |

- X can be V<sub>IH</sub> or V<sub>IL</sub> for address or control pins except for RY/BY#, which is either V<sub>OL</sub> or V<sub>OH</sub>, or High Z or D<sub>OUT</sub> for data pins depending on whether or not OE# is active.

- RY/BY# output is open drain. When the WSM is ready, Erase is suspended, or the device is in deep power-down mode, RY/BY# will be at V<sub>OH</sub> if it is tied to V<sub>CC</sub> through a resistor. RY/BY# at V<sub>OH</sub> is independent of OE# while a WSM operation is in progress.

- 3. RP# at GND  $\pm$  0.2V ensures the lowest deep power-down current.

- A<sub>0</sub> and A<sub>1</sub> at V<sub>IL</sub> provide device manufacturer codes in x8 and x16 modes respectively. A<sub>0</sub> and A<sub>1</sub> at V<sub>IH</sub> provide device ID codes in x8 and x16 modes respectively. All other addresses are set to zero.

- Commands for erase, data program, or lock-block operations can only be completed successfully when V<sub>PP</sub> = V<sub>PPH1</sub> or V<sub>PP</sub> = V<sub>PPH2</sub>.

- While the WSM is running, RY/BY# stays at V<sub>OL</sub> until all operations are complete. RY/BY# goes to V<sub>OH</sub> when the WSM is not busy or in erase suspend mode.

- RY/BY# may be at V<sub>OL</sub> while the WSM is busy performing various operations (for example, a Status Register read during a write operation).

- 8. The 28F016XS shares an identical device identifier with the 28F016XD.

- 9. CE<sub>0-1</sub># at V<sub>IL</sub> is defined as both CE<sub>0</sub># and CE<sub>1</sub># low, and CE<sub>0-1</sub># at V<sub>IH</sub> is defined as either CE<sub>0</sub># or CE<sub>1</sub># high.

- 10. Addresses are latched on the rising edge of CLK in conjunction with ADV# low. Address A<sub>1</sub> = 0 selects the even bank and A<sub>1</sub> = 1 selects the odd bank, in both byte-wide mode and word-wide mode device configurations.

### 4.2 Bus Operations for Byte-Wide Mode (BYTE# = V<sub>IL</sub>)

| Mode                                | Notes   | RP#             | CE <sub>0-1</sub> # | OE#             | WE#             | ADV#            | CLK | Ao              | DQ <sub>0-7</sub> | RY/BY#          |

|-------------------------------------|---------|-----------------|---------------------|-----------------|-----------------|-----------------|-----|-----------------|-------------------|-----------------|

| Latch Read<br>Address               | 1,9,10  | V <sub>IH</sub> | V <sub>IL</sub>     | Х               | V <sub>IH</sub> | V <sub>IL</sub> | 1   | Х               | ×                 | х               |

| Inhibit<br>Latching<br>Read Address | 1,9     | V <sub>IH</sub> | V <sub>IL</sub>     | Х               | V <sub>IH</sub> | V <sub>iH</sub> | 1   | х               | х                 | ×               |

| Read                                | 1,2,7,9 | V <sub>iH</sub> | V <sub>IL</sub>     | V <sub>IL</sub> | V <sub>IH</sub> | х               | Î   | Х               | D <sub>OUT</sub>  | Х               |

| Output<br>Disable                   | 1,6,7,9 | V <sub>IH</sub> | V <sub>IL</sub>     | V <sub>iH</sub> | V <sub>IH</sub> | х               | Х   | Х               | High Z            | х               |

| Standby                             | 1,6,7,9 | V <sub>IH</sub> | V <sub>IH</sub>     | X               | х               | Х               | Х   | Х               | High Z            | х               |

| Deep<br>Power-Down                  | 1,3     | V <sub>IL</sub> | х                   | Х               | Х               | х               | Х   | Х               | High Z            | V <sub>OH</sub> |

| Manufacturer<br>ID                  | 1,4,9   | V <sub>IH</sub> | V <sub>IL</sub>     | V <sub>IL</sub> | V <sub>iH</sub> | х               | 1   | V <sub>IL</sub> | 89H               | V <sub>OH</sub> |

| Device ID                           | 1,4,8,9 | V <sub>IH</sub> | V <sub>IL</sub>     | V <sub>IL</sub> | V <sub>IH</sub> | Х               | 1   | V <sub>IH</sub> | A8H               | V <sub>OH</sub> |

| Write                               | 1,5,6,9 | V <sub>IH</sub> | V <sub>IL</sub>     | V <sub>iH</sub> | V <sub>IL</sub> | Х               | Х   | Х               | D <sub>IN</sub>   | х               |

- X can be V<sub>IH</sub> or V<sub>IL</sub> for address or control pins except for RY/BY#, which is either V<sub>OL</sub> or V<sub>OH</sub>, or High Z or D<sub>OUT</sub> for data pins depending on whether or not OE# is active.

- RY/BY# output is open drain. When the WSM is ready, Erase is suspended, or the device is in deep power-down mode, RY/BY# will be at V<sub>OH</sub> if it is tied to V<sub>CC</sub> through a resistor. RY/BY# at V<sub>OH</sub> is independent of OE# while a WSM operation is in progress.

- 3. RP# at GND ± 0.2V ensures the lowest deep power-down current.

- A<sub>0</sub> and A<sub>1</sub> at V<sub>IL</sub> provide device manufacturer codes in x8 and x16 modes respectively. A<sub>0</sub> and A<sub>1</sub> at V<sub>IH</sub> provide device ID codes in x8 and x16 modes respectively. All other addresses are set to zero.

- Commands for erase, data program, or lock-block operations can only be completed successfully when V<sub>PP</sub> = V<sub>PPH1</sub> or V<sub>PP</sub> = V<sub>PPH2</sub>.

- While the WSM is running, RY/BY# stays at Vot until all operations are complete. RY/BY# goes to VoH when the WSM is not busy or in erase suspend mode.

- RY/BY# may be at VoL while the WSM is busy performing various operations (for example, a Status Register read during a program operation).

- 8. The 28F016XS shares an identical device identifier with the 28F016XD.

- 9. CE<sub>0-1</sub># at V<sub>IL</sub> is defined as both CE<sub>0</sub># and CE<sub>1</sub># low, and CE<sub>0-1</sub># at V<sub>IH</sub> is defined as either CE<sub>0</sub># or CE<sub>1</sub># high.

- 10. Addresses are latched on the rising edge of CLK in conjunction with ADV# low. Address A<sub>1</sub> = 0 selects the even bank and A<sub>1</sub> = 1 selects the odd bank, in both byte-wide mode and word-wide mode device configurations.

## 4.3 28F008SA—Compatible Mode Command Bus Definitions

|                                 |       | Fi    | st Bus C | ycle                | Second Bus Cycle |      |                     |

|---------------------------------|-------|-------|----------|---------------------|------------------|------|---------------------|

| Command                         | Notes | Oper  | Addr     | Data <sup>(4)</sup> | Oper             | Addr | Data <sup>(4)</sup> |

| Read Array                      |       | Write | х        | xxFFH               | Read             | AA   | AD                  |

| Intelligent Identifier          | 1     | Write | х        | xx90H               | Read             | IA   | D                   |

| Read Compatible Status Register | 2     | Write | ×        | хх70Н               | Read             | Х    | CSRD                |

| Clear Status Register           | 3     | Write | х        | xx50H               |                  |      |                     |

| Program                         |       | Write | х        | xx40H               | Write            | PA   | PD                  |

| Alternate Program               |       | Write | х        | xx10H               | Write            | PA   | PD                  |

| Block Erase/Confirm             |       | Write | ×        | xx20H               | Write            | BA   | xxD0H               |

| Erase Suspend/Resume            |       | Write | Х        | ххВ0Н               | Write            | ×    | xxD0H               |

ADDRESS

DATA

AA = Array Address

BA = Block Address

CSRD = CSR Data

IA = Identifier Address

ID = Identifier Data

PA = Program Address

PD = Program Data

X = Don't Care

- 1. Following the Intelligent Identifier command, two read operations access the manufacturer and device signature codes.

- 2. The CSR is automatically available after device enters data program, erase, or suspend operations.

- Clears CSR.3, CSR.4 and CSR.5. Also clears GSR.5 and all BSR.5, BSR.4 and BSR.2 bits. See Status Register definitions.

- 4. The upper byte of the data bus (D<sub>8-15</sub>) during command writes is a "Don't Care" in x16 operation of the device.

#### 4.4 28F016XS—Enhanced Command Bus Definitions

|                               |       | Fi    | rst Bus C | ycle                | Second Bus Cycle |      |                     |

|-------------------------------|-------|-------|-----------|---------------------|------------------|------|---------------------|

| Command                       | Notes | Oper  | Addr      | Data <sup>(4)</sup> | Oper             | Addr | Data <sup>(4)</sup> |

| Read Extended Status Register | 1     | Write | Х         | xx71H               | Read             | RA   | GSRD<br>BSRD        |

| Lock Block/Confirm            |       | Write | ×         | xx77H               | Write            | BA   | xxD0H               |

| Upload Status Bits/Confirm    | 2     | Write | ×         | xx97H               | Write            | Х    | xxD0H               |

| Device Configuration          | 3     | Write | Х         | хх96Н               | Write            | Х    | DCCD                |

**ADDRESS**

DATA

BA = Block Address

AD = Array Data

RA = Extended Register Address

BSRD = BSR Data

PA = Program Address

GSRD = GSR Data

X = Don't Care

DCCD = Device Configuration Code Data

- 1. RA can be the GSR address or any BSR address. See Figures 5 and 6 for Extended Status Register memory maps.

- Upon device power-up, all BSR lock-bits come up locked. The Upload Status Bits command must be written to reflect the actual lock-bit status.

- 3. This command sets the SFI Configuration allowing the device to be optimized for the specific sytem operating frequency.

- 4. The upper byte of the Data bus (D<sub>B-15</sub>) during command writes is a "Don't Care" in x16 operation of the device.

#### 4.5 **Compatible Status Register**

| WSMS | ESS | ES | DWS | VPPS | R | R | R |

|------|-----|----|-----|------|---|---|---|

| 7    | 6   | 5  | 4   | 3    | 2 | 1 | 0 |

#### NOTES:

CSR.7 = WRITE STATE MACHINE STATUS

1 = Ready

0 = Busy

RY/BY# output or WSMS bit must be checked to determine completion of an operation (erase, erase suspend, or data program) before the appropriate Status bit (ESS, ES or DWS) is checked for success.

CSR.6 = ERASE-SUSPEND STATUS

1 = Erase Suspended

0 = Erase In Progress/Completed

CSR.5 = ERASE STATUS

1 = Error in Block Erasure

0 = Successful Block Erase

If DWS and ES are set to "1" during an erase attempt, an improper command sequence was entered. Clear the CSR and attempt the operation again.

CSR.4 = DATA WRITE STATUS

1 = Error in Data Program

0 = Data Program Successful

$\begin{aligned} \text{CSR.3} &= \text{V}_{\text{PP}} \text{ STATUS} \\ & 1 &= \text{V}_{\text{PP}} \text{ Error Detect, Operation Abort} \end{aligned}$

$0 = V_{pp} OK$

The VPPS bit, unlike an A/D converter, does not provide continuous indication of VPP level. The WSM interrogates V<sub>PP</sub>'s level only after the Data Program or Erase command sequences have been entered, and informs the system if Vpp has not been switched on. VPPS is not guaranteed to report accurate feedback between V<sub>PPLK</sub>(max) and V<sub>PPH1</sub>(min), between V<sub>PPH1</sub>(max) and V<sub>PPH2</sub>(min), and above V<sub>PPH2</sub>(max).

CSR.2-0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use; mask them out when polling the CSR.

### 4.6 Global Status Register

| WSMS | oss | DOS | R | R | R | R | R |

|------|-----|-----|---|---|---|---|---|

| 7    | 6   | 5   | 4 | 3 | 2 | 1 | 0 |

#### NOTES:

GSR.7 = WRITE STATE MACHINE STATUS

1 = Ready

0 = Busy

RY/BY# output or WSMS bit must be checked to determine completion of an operation (block lock, suspend, Upload Status Bits, erase or data program) before the appropriate Status bit (OSS or DOS) is checked for success.

GSR.6 = OPERATION SUSPEND STATUS

1 = Operation Suspended

0 = Operation in Progress/Completed

GSR.5 = DEVICE OPERATION STATUS

1 = Operation Unsuccessful

0 = Operation Successful or Currently Running

GSR.4-0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use; mask them out when polling the GSR.

### 4.7 Block Status Register

| BS | BLS | BOS | R | R | VPPS | VPPL | R |

|----|-----|-----|---|---|------|------|---|

| 7  | 6   | 5   | 4 | 3 | 2    | 1    | 0 |

#### NOTES:

BSR.7 = BLOCK STATUS

1 = Ready

0 = Busy

RY/BY# output or BS bit must be checked to determine completion of an operation (block lock, suspend, erase or data program) before the appropriate Status bits (BOS, BLS) is checked for success.

BSR.6 = BLOCK LOCK STATUS

1 = Block Unlocked for Program/Erase

0 = Block Locked for Program/Erase

BSR.5 = BLOCK OPERATION STATUS

1 = Operation Unsuccessful

0 = Operation Successful or Currently Running

$BSR.2 = V_{PP} STATUS$

1 = V<sub>PP</sub> Error Detect, Operation Abort

$0 = V_{PP} OK$

BSR.1 = VPP LEVEL

$1 = V_{PP}$  Detected at 5.0V ± 10%

$0 = V_{PP}$  Detected at 12.0V  $\pm 5\%$

BSR.1 is not guaranteed to report accurate feedback between the  $V_{PPH1}$  and  $V_{PPH2}$  voltage ranges. Programs and erases with  $V_{PP}$  between  $V_{PPLK}(\text{max})$  and  $V_{PPH1}$  (min), between  $V_{PPH1}(\text{max})$  and  $V_{PPH2}(\text{min})$ , and above  $V_{PPH2}(\text{max})$  produce spurious results and should

not be attempted.

BSR.4,3,0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use; mask them out when polling the BSRs.

### 4.8 Device Configuration Code

| R | R | SFI2 | SFI1 | SFI0 | R | R | RB |

|---|---|------|------|------|---|---|----|

| 7 | 6 | 5    | 4    | 3    | 2 | 1 | 0  |

#### NOTES:

DCC.5-DCC.3 = SFI CONFIGURATION

(SFI2-SFI0)

001 = SFI Configuration 1

010 = SFI Configuration 2 011 = SFI Configuration 3

100 = SFI Configuration 4

(Default)

Default SFI Configuration on power-up or return from deep power-down mode is 4, allowing system boot from the 28F016XS at any frequency up to the device's maximum frequency. Undocumented combinations of SFI2-SFI0 are reserved by Intel Corporation for future implementations and should not be used.

DCC.0 = RY/BY# CONFIGURATION

(RB)

1 = Level Mode (Default)

Undocumented combinations of RB are reserved by Intel Corporation for future implementations

and should not be used.

DCC.7-DCC.6, DCC.2-DCC.1 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use. Set these bits to "0" when modifying the Device Configuration Code.

### 4.9 SFI Configuration Table

| SFI<br>Configuration | Notes | 28F016XS-15<br>Frequency (MHz) | 28F016XS-20<br>Frequency (MHz) | 28F016XS-25<br>Frequency (MHz) |

|----------------------|-------|--------------------------------|--------------------------------|--------------------------------|

| 4                    | 1     | 50 (and below)                 | 50 (and below)                 | 40 (and below)                 |

| 3                    |       | 50 (and below)                 | 37.5 (and below)               | 30 (and below)                 |

| 2                    |       | 33 (and below)                 | 25 (and below)                 | 20 (and below)                 |

| 1                    |       | 16.7 (and below)               | 12.5 (and below)               | 10 (and below)                 |

<sup>1.</sup> Default SFI Configuration after power-up or return from deep power-down mode via RP#low.

#### 5.0 ELECTRICAL SPECIFICATIONS

### 5.1 Absolute Maximum Ratings\*

Temperature Under Bias ......0°C to +80°C Storage Temperature ......65°C to +125°C NOTICE: This is a production datasheet. The specifications are subject to change without notice. Verify with your local Intel Sales office that you have the latest datasheet before finalizing a design.

"WARNING: Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

$V_{CC} = 3.3V \pm 5\%$  Systems

| Symbol           | Parameter                                                                         | Notes | Min  | Max                      | Units | Test Conditions     |

|------------------|-----------------------------------------------------------------------------------|-------|------|--------------------------|-------|---------------------|

| TA               | Operating Temperature, Commercial                                                 | 1     | 0    | 70                       | °C    | Ambient Temperature |

| V <sub>CC</sub>  | V <sub>CC</sub> with Respect to GND                                               | 2     | -0.2 | 7.0                      | ٧     |                     |

| V <sub>PP</sub>  | V <sub>PP</sub> Supply Voltage with Respect to GND                                | 2,3   | -0.2 | 14.0                     | ٧     |                     |

| ٧                | Voltage on any Pin (except V <sub>CC</sub> ,V <sub>PP</sub> ) with Respect to GND | 2,5   | -0.5 | V <sub>CC</sub><br>+ 0.5 | ٧     |                     |

| 1                | Current into any Non-Supply Pin                                                   | 5     |      | ± 30                     | mA    |                     |

| l <sub>out</sub> | Output Short Circuit Current                                                      | 4     |      | 100                      | mA    |                     |

### $V_{CC} = 5.0V \pm 5\%$ Systems

| Symbol          | Parameter                                                                         | Notes | Min  | Max  | Units | Test Conditions     |

|-----------------|-----------------------------------------------------------------------------------|-------|------|------|-------|---------------------|

| TA              | Operating Temperature, Commercial                                                 | 1     | 0    | 70   | °C    | Ambient Temperature |

| V <sub>CC</sub> | V <sub>CC</sub> with Respect to GND                                               | 2     | -0.2 | 7.0  | ٧     |                     |

| V <sub>PP</sub> | V <sub>PP</sub> Supply Voltage with Respect to GND                                | 2,3   | -0.2 | 14.0 | ٧     |                     |

| ٧               | Voltage on any Pin (except V <sub>CC</sub> ,V <sub>PP</sub> ) with Respect to GND | 2,5   | -2.0 | 7.0  | ٧     |                     |

| 1               | Current into any Non-Supply Pin                                                   | 5     |      | ± 30 | mA    |                     |

| lout            | Output Short Circuit Current                                                      | 4     |      | 100  | mA    |                     |

- 1. Operating temperature is for commercial product defined by this specification.

- 2. Minimum DC voltage is -0.5V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <20 ns. Maximum DC voltage on input/output pins is  $V_{CC} + 0.5V$  which may overshoot to  $V_{CC} + 2.0V$  for periods <20 ns.

- 3. Maximum DC voltage on V<sub>PP</sub> may overshoot to +14.0V for periods <20 ns.

- 4. Output shorted for no more than one second. No more than one output shorted at a time.

- 5. This specification also applies to pins marked "NC."

## 5.2 Capacitance

For a 3.3V ± 5% System:

|                   |                                                                 |       |     |     |       | , · · · · · · · · · · · · · · · · · · ·   |

|-------------------|-----------------------------------------------------------------|-------|-----|-----|-------|-------------------------------------------|

| Symbol            | Parameter                                                       | Notes | Тур | Max | Units | Test Conditions                           |

| C <sub>IN</sub>   | Capacitance Looking into an Address/Control Pin                 | 1     | 6   | 8   | pF    | T <sub>A</sub> = +25°C, f = 1.0 MHz       |

| C <sub>OUT</sub>  | Capacitance Looking into an<br>Output Pin                       | 1     | 8   | 12  | pF    | $T_A = +25^{\circ}C, f = 1.0 \text{ MHz}$ |

| C <sub>LOAD</sub> | Load Capacitance Driven by<br>Outputs for Timing Specifications | 1, 2  |     | 50  | pF    | For the 28F016XS-20 and 28F016XS-25       |

For 5.0V ± 5% System:

| Symbol            | Parameter                                                       | Notes | Тур | Max | Units | Test Conditions                     |

|-------------------|-----------------------------------------------------------------|-------|-----|-----|-------|-------------------------------------|

| C <sub>IN</sub>   | Capacitance Looking into an Address/Control Pin                 | 1     | 6   | 8   | рF    | T <sub>A</sub> = +25°C, f = 1.0 MHz |

| C <sub>OUT</sub>  | Capacitance Looking into an<br>Output Pin                       | 1     | 8   | 12  | pF    | T <sub>A</sub> = +25°C, f = 1.0 MHz |

| C <sub>LOAD</sub> | Load Capacitance Driven by<br>Outputs for Timing Specifications | 1, 2  |     | 100 | pF    | For the 28F016XS-20                 |

|                   |                                                                 |       |     | 30  | ρF    | For the 28F016XS-15                 |

- 1. Sampled, not 100% tested. Guaranteed by design.

- 2. To obtain iBIS models for the 28F016XS, please contact your local Intel/Distribution Sales Office.

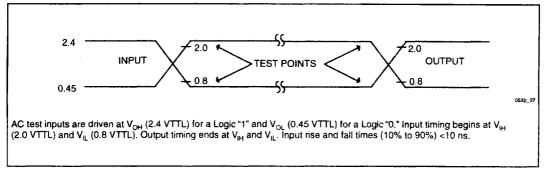

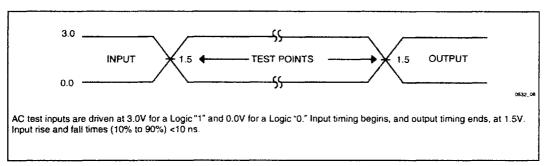

### 5.3 Transient Input/Output Reference Waveforms

Figure 8. Transient input/Output Reference Waveform ( $V_{CC}$  = 5.0V  $\pm$  5%) for Standard Testing Configuration<sup>(1)</sup>

Figure 9. Transient Input/Output Reference Waveform ( $V_{CC}$  = 3.3V ± 5%) High Speed Reference Waveform<sup>(2)</sup> ( $V_{CC}$  = 5.0V ± 5%)

- 1. Testing characteristics for 28F016XS-20 at 5V  $\rm V_{CC}$

- 2. Testing characteristics for 28F016XS-15 at 5V  $V_{CC}$  and 28F016XS-20/28F016XS-25 at 3.3V  $V_{CC}$ .

## 5.4 DC Characteristics

$V_{CC}$  = 3.3V ± 5%,  $T_A$  = 0°C to +70°C 3/5# = Pin Set High for 3.3V Operations

| Symbol            | Parameter                                     | Notes       | Min | Тур | Max  | Units | Test Conditions                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------|-----------------------------------------------|-------------|-----|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lu                | Input Load Current                            | 1           |     |     | ± 1  | μA    | $V_{CC} = V_{CC} Max$<br>$V_{IN} = V_{CC} \text{ or GND}$                                                                                                                                                                                                                                                                                                                                                                                |

| I <sub>LO</sub>   | Output Leakage<br>Current                     | 1           |     |     | ± 10 | μΑ    | $V_{CC} = V_{CC} Max$<br>$V_{OUT} = V_{CC} \text{ or GND}$                                                                                                                                                                                                                                                                                                                                                                               |

| locs              | V <sub>CC</sub> Standby<br>Current            | 1,5         |     | 70  | 130  | μА    | $V_{CC} = V_{CC}$ Max<br>$CE_0$ #, $CE_1$ #, $RP$ # = $V_{CC}$ ±<br>0.2V<br>BYTE#, WP#, 3/5# = $V_{CC}$ ±<br>0.2V or GND ± 0.2V                                                                                                                                                                                                                                                                                                          |

|                   |                                               |             |     | 1   | 4    | mA    | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE <sub>0</sub> #, CE <sub>1</sub> #, RP# = V <sub>IH</sub><br>BYTE#, WP#, 3/5# = V <sub>IH</sub> or<br>V <sub>IL</sub>                                                                                                                                                                                                                                                                         |

| I <sub>CCD</sub>  | V <sub>CC</sub> Deep<br>Power-Down<br>Current | 1           |     | 2   | 5    | μА    | $RP\# = GND \pm 0.2V$ $BYTE\# = V_{CC} \pm 0.2V \text{ or}$ $GND \pm 0.2V$                                                                                                                                                                                                                                                                                                                                                               |

| Iccn <sup>1</sup> | V <sub>CC</sub> Word/Byte<br>Read Current     | 1,4,5       |     | 65  | 85   | mA    | $\begin{split} &V_{CC} = V_{CC} \text{ Max} \\ &C\text{MOS: } CE_0\# \text{ ,}CE_1\# = \text{GND} \\ &\pm 0.2\text{V, BYTE}\# = \text{GND} \pm \\ &0.2\text{V or } V_{CC} \pm 0.2\text{V,} \\ &\text{Inputs = GND} \pm 0.2\text{V or} \\ &V_{CC} \pm 0.2\text{V} \\ &\text{4-Location Access} \\ &\text{Sequence: } 3\text{-}1\text{-}1\text{-}1 \\ &\text{(clocks)} \\ &\text{f} = 25 \text{ MHz, } I_{OUT} = 0 \text{ mA} \end{split}$ |

| Iccn <sup>2</sup> | V <sub>CC</sub> Word/Byte<br>Read Current     | 1,4,<br>5,6 |     | 60  | 75   | mA    | $V_{CC} = V_{CC} \text{ Max}$ $CMOS: CE_0\#, CE_1\# = GND \pm 0.2V, BYTE\# = GND \pm 0.2V \text{ or } V_{CC} \pm 0.2V,$ $Inputs = GND \pm 0.2V \text{ or } V_{CC} \pm 0.2V$ $4-\text{Location Access}$ $Sequence: 3-1-1-1 \text{ (clocks)}$ $f = 16 \text{ MHz}, I_{OUT} = 0 \text{ mA}$                                                                                                                                                 |

### 5.4 DC Characteristics (Continued)

$V_{CC}$  = 3.3V ± 5%,  $T_A$  = 0°C to +70°C 3/5# = Pin Set High for 3.3V Operations

| Symbol            | Parameter                                   | Notes | Min                     | Тур | Max                     | Units | Test Conditions                                                                 |

|-------------------|---------------------------------------------|-------|-------------------------|-----|-------------------------|-------|---------------------------------------------------------------------------------|

| Iccw              | V <sub>CC</sub> Program<br>Current          | 1,6   |                         | 8   | 12                      | mA    | V <sub>PP</sub> = 12.0V ± 5%<br>Program in Progress                             |

|                   |                                             |       |                         | 8   | 17                      | mA    | V <sub>PP</sub> = 5.0V ± 10%<br>Program in Progress                             |

| ICCE              | V <sub>CC</sub> Block Erase<br>Current      | 1,6   |                         | 6   | 12                      | mA    | V <sub>PP</sub> = 12.0V ± 5%<br>Block Erase in Progress                         |

|                   |                                             |       |                         | 9   | 17                      | mA    | V <sub>PP</sub> = 5.0V ± 10%<br>Block Erase in Progress                         |

| CCES              | V <sub>CC</sub> Erase<br>Suspend Current    | 1,2   |                         | 3   | 6                       | mA    | CE <sub>0</sub> #, CE <sub>1</sub> # = V <sub>IH</sub><br>Block Erase Suspended |

| I <sub>PPS</sub>  | V <sub>PP</sub> Standby/Read                | 1     |                         | ± 1 | ± 10                    | μA    | $V_{PP} \leq V_{CC}$                                                            |

| I <sub>PPR</sub>  | Current                                     |       |                         | 30  | 200                     | μA    | V <sub>PP</sub> > V <sub>CC</sub>                                               |

| I <sub>PPD</sub>  | V <sub>PP</sub> Deep Power-<br>Down Current | 1     |                         | 0.2 | 5                       | μΑ    | RP# = GND ± 0.2V                                                                |

| I <sub>PPW</sub>  | V <sub>PP</sub> Program<br>Current          | 1,6   |                         | 10  | 15                      | mA    | V <sub>PP</sub> = 12.0V ± 5%<br>Program in Progress                             |

|                   |                                             |       |                         | 15  | 25                      | mA    | Program in Progress                                                             |

| I <sub>PPE</sub>  | V <sub>PP</sub> Erase Current               | 1,6   |                         | 4   | 10                      | mA    | V <sub>PP</sub> = 12.0V ± 5%<br>Block Erase in Progress                         |

|                   |                                             |       |                         | 14  | 20                      | mA    | V <sub>PP</sub> = 5.0V ± 10%<br>Block Erase in Progress                         |

| I <sub>PPES</sub> | V <sub>PP</sub> Erase<br>Suspend Current    | 1     |                         | 30  | 200                     | μΑ    | V <sub>PP</sub> = V <sub>PPH1</sub> or V <sub>PPH2</sub> Block Erase Suspended  |

| V <sub>IL</sub>   | Input Low Voltage                           | 6     | -0.3                    |     | 0.8                     | ٧     |                                                                                 |

| V <sub>iH</sub>   | Input High Voltage                          | 6     | 2.0                     |     | V <sub>CC</sub><br>+0.3 | ٧     |                                                                                 |

| V <sub>OL</sub>   | Output Low<br>Voltage                       | 6     |                         |     | 0.4                     | ٧     | V <sub>CC</sub> = V <sub>CC</sub> Min<br>I <sub>OL</sub> = 4 mA                 |

| V <sub>OH</sub> 1 | Output High<br>Voltage                      | 6     | 2.4                     |     |                         | ٧     | $V_{CC} = V_{CC} Min$<br>$I_{OH} = -2.0 mA$                                     |

| V <sub>OH</sub> 2 |                                             |       | V <sub>CC</sub><br>-0.2 |     |                         | V     | V <sub>CC</sub> = V <sub>CC</sub> Min<br>I <sub>OH</sub> = -100 μA              |

### 5.4 DC Characteristics (Continued)

$V_{CC}$  = 3.3V ± 5%,  $T_A$  = 0°C to +70°C 3/5# = Pin Set High for 3.3V Operations

| Symbol            | Parameter                                             | Notes | Min  | Тур  | Max  | Units | <b>Test Conditions</b> |

|-------------------|-------------------------------------------------------|-------|------|------|------|-------|------------------------|

| V <sub>PPLK</sub> | V <sub>PP</sub><br>Erase/Program<br>Lock Voltage      | 3,6   | 0.0  |      | 1.5  | V     |                        |

| V <sub>PPH1</sub> | V <sub>PP</sub> during<br>Program/Erase<br>Operations | 3     | 4.5  | 5.0  | 5.5  | V     |                        |

| V <sub>PPH2</sub> | V <sub>PP</sub> during<br>Program/Erase<br>Operations | 3     | 11.4 | 12.0 | 12.6 | V     |                        |

| V <sub>LKO</sub>  | V <sub>CC</sub><br>Erase/Program<br>Lock Voltage      |       | 2.0  |      |      | ٧     |                        |

- All currents are in RMS unless otherwise noted. Typical values at V<sub>CC</sub> = 3.3V, V<sub>PP</sub> = 12.0V or 5.0V, T = +25°C. These currents are valid for all product versions (package and speeds).

- I<sub>CCES</sub> is specified with the device de-selected. If the device is read while in erase suspend mode, current draw is the sum of I<sub>CCES</sub> and I<sub>CCR</sub>.

- Block erases, programs and lock block operations are inhibited when V<sub>PP</sub> ≤ V<sub>PPLK</sub> and not guaranteed in the ranges between V<sub>PPLK</sub>(max) and V<sub>PPH1</sub>(min), between V<sub>PPH1</sub> (max) and V<sub>PPH2</sub>(min) and above V<sub>PPH2</sub>(max).

- 4. Automatic Power Savings (APS) reduces  $I_{CCR}$  to 3 mA typical in static operation.

- 5. CMOS inputs are either  $V_{CC} \pm 0.2V$  or GND  $\pm 0.2V$ . TTL inputs are either  $V_{IL}$  or  $V_{IH}$ .

- 6. Sampled, but not 100% tested. Guaranteed by design.

### 5.5 DC Characteristics

$V_{CC}$  = 5.0V ± 5%,  $T_A$  = 0°C to +70°C 3/5# = Pin Set Low for 5.0V Operations

| Symbol            | Parameter                                   | Notes       | Min | Тур | Max  | Units      | Test Conditions                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------|---------------------------------------------|-------------|-----|-----|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>LI</sub>   | Input Load Current                          | 1           |     |     | ± 1  | μА         | $V_{CC} = V_{CC} Max$<br>$V_{IN} = V_{CC} \text{ or GND}$                                                                                                                                                                                                                                                                                                                                  |

| I <sub>LO</sub>   | Output Leakage<br>Current                   | 1           |     |     | ± 10 | μА         | V <sub>CC</sub> = V <sub>CC</sub> Max<br>V <sub>OUT</sub> = V <sub>CC</sub> or GND                                                                                                                                                                                                                                                                                                         |

| Iccs              | V <sub>CC</sub> Standby<br>Current          | 1,5         |     | 70  | 130  | μА         | $V_{CC} = V_{CC}$ Max<br>$CE_0$ #, $CE_1$ #, $RP$ # = $V_{CC}$ ±<br>0.2V<br>BYTE#, WP#, 3/5# = $V_{CC}$ ±<br>0.2V or GND ± 0.2V                                                                                                                                                                                                                                                            |

|                   |                                             |             |     | 2   | 4    | mA         | V <sub>CC</sub> = V <sub>CC</sub> Max<br>CE <sub>0</sub> #, CE <sub>1</sub> #, RP# = V <sub>IH</sub><br>BYTE#, WP#, 3/5# = V <sub>IH</sub> or<br>V <sub>IL</sub>                                                                                                                                                                                                                           |

| Icco              | V <sub>CC</sub> Deep Power-<br>Down Current | 1           |     | 2   | 5    | μΑ         | $RP\# = GND \pm 0.2V$ $BYTE\# = V_{CC} \pm 0.2V \text{ or}$ $GND \pm 0.2V$                                                                                                                                                                                                                                                                                                                 |

| ICCR1             | V <sub>CC</sub> Read Current                | 1,4,5       |     | 120 | 175  | mA         | $\begin{split} &V_{CC} = V_{CC} \text{ Max} \\ &CMOS: CE_0\#, CE_1\# = GND \\ &\pm 0.2V, \text{ BYTE}\# = GND \pm \\ &0.2V \text{ or } V_{CC} \pm 0.2V, \\ &\text{ Inputs} = GND \pm 0.2V \text{ or } \\ &V_{CC} \pm 0.2V \\ &\text{ 4-Location Access} \\ &\text{ Sequence: } 3\text{-1-1-1} \\ &\text{ (clocks)} \\ &\text{ f} = 33 \text{ MHz, } I_{OUT} = 0 \text{ mA} \end{split}$    |

| ICCH <sup>2</sup> | V <sub>CC</sub> Read Current                | 1,4,<br>5,6 |     | 105 | 150  | m <b>A</b> | $\begin{split} &V_{CC}=V_{CC}\text{ Max}\\ &C\text{MOS: }CE_0\#, CE_1\#=\text{GND}\\ &\pm 0.2\text{V, BYTE}\#=\text{GND}\pm\\ &0.2\text{V, or }V_{CC}\pm 0.2\text{V,}\\ &\text{Inputs}=\text{GND}\pm 0.2\text{V or}\\ &V_{CC}\pm 0.2\text{V}\\ &\text{4-Location Access}\\ &\text{Sequence: }3\text{-1-1-1}\\ &\text{(clocks)}\\ &\text{f}=20\text{ MHz, }I_{OUT}=0\text{ mA} \end{split}$ |

# 5.5 DC Characteristics (Continued)

$V_{CC}$  = 5.0V ± 5%,  $T_A$  = 0°C to +70°C 3/5# = Pin Set Low for 5.0V Operations

| Symbol            | Parameter                                   | Notes | Min                     | Тур | Max                     | Units | Test Conditions                                                                   |

|-------------------|---------------------------------------------|-------|-------------------------|-----|-------------------------|-------|-----------------------------------------------------------------------------------|

| Iccw              | V <sub>CC</sub> Program<br>Current          | 1,6   |                         | 25  | 35                      | mA    | V <sub>PP</sub> = 12.0V ± 5%<br>Program in Progress                               |

|                   |                                             |       |                         | 25  | 40                      | mA    | V <sub>PP</sub> = 5.0V ± 10%<br>Program in Progress                               |

| ICCE              | V <sub>CC</sub> Erase<br>Suspend Current    | 1,6   |                         | 18  | 25                      | mA    | V <sub>PP</sub> = 12.0V ± 5%<br>Block Erase in Progress                           |