# AMD Extensions to the 3DNow!™ and MMX™ Instruction Sets

# Manual

Downloaded from: https://www.datasheetcatalog.com/

#### © 2000 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

#### Trademarks

AMD, the AMD logo, AMD Athlon, and combinations thereof, and 3DNow! are trademarks, and AMD-K6 is a registered trademark of Advanced Micro Devices, Inc.

MMX is a trademark of Intel Corporation.

Other product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

### Contents

|   | Revision History vii                                  |

|---|-------------------------------------------------------|

| 1 | Extensions to the 3DNow!™ and MMX™ Instruction Sets 1 |

|   | Introduction 1                                        |

| 2 | Extensions to the 3DNow!™ Instruction Set 3           |

|   | PF2IW                                                 |

|   | PFNACC                                                |

|   | PFPNACC                                               |

|   | PI2FW                                                 |

|   | PSWAPD                                                |

| 3 | Extensions to the MMX <sup>™</sup> Instruction Set 11 |

|   | MASKMOVQ 12                                           |

|   | MOVNTQ                                                |

|   | PAVGB                                                 |

|   | PAVGW                                                 |

|   | PEXTRW                                                |

|   | PINSRW                                                |

|   | PMAXSW                                                |

|   | PMAXUB                                                |

|   | PMINSW 24                                             |

|   | PMINUB 25                                             |

|   | PMOVMSKB 27                                           |

|   | PMULHUW                                               |

|   | PREFETCHNTA - PREFETCHT0 - PREFETCHT1 -<br>PREFETCHT2 |

|   | PSADBW                                                |

|   | PSHUFW                                                |

|   | SFENCE                                                |

####

AMD Extensions to the 3DNow!<sup>™</sup> and MMX<sup>™</sup> Instruction Sets

### **List of Tables**

| Table 1. | 3DNow! <sup>TM</sup> Technology DSP Extensions 2     |

|----------|------------------------------------------------------|

| Table 2. | MMX <sup>TM</sup> Instruction Set Extensions 2       |

| Table 3. | Numerical Range for the PF2IW Instruction 5          |

| Table 4. | Locality References for the Prefetch Instructions 30 |

####

AMD Extensions to the 3DNow!<sup>™</sup> and MMX<sup>™</sup> Instruction Sets

22466D/0-March 2000

22466D/0-March 2000

AMD Extensions to the 3DNow!<sup>™</sup> and MMX<sup>™</sup> Instruction Sets

### **Revision History**

| Date             | Rev | Description                                                                                                                                                                                                                                                          |  |  |  |  |  |

|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| August 1999      | В   | Initial public release                                                                                                                                                                                                                                               |  |  |  |  |  |

| February<br>2000 | С   | <ul> <li>Clarification of PSWAPD operation on page 9.</li> <li>Clarification of PINSRW description and operation on page 20.</li> <li>Clarification of PSHUFW description and operation on page 33.</li> <li>Clarification of SFENCE encoding on page 35.</li> </ul> |  |  |  |  |  |

| March 2000       | D   | <ul> <li>Clarification of PFNACC operation on page 6.</li> <li>Clarification of PFPNACC operation on page 7.</li> </ul>                                                                                                                                              |  |  |  |  |  |

####

AMD Extensions to the 3DNow!<sup>™</sup> and MMX<sup>™</sup> Instruction Sets

# 1

## Extensions to the 3DNow!™ and MMX<sup>™</sup> Instruction Sets

### Introduction

With the advent of the AMD Athlon<sup>TM</sup> processor, AMD has taken 3DNow!<sup>TM</sup> Technology to the next level of performance and functionality. The AMD Athlon processor adds 24 new instructions to the existing 3DNow! and MMX<sup>TM</sup> instruction sets. Along with the new instructions, the AMD Athlon processor implements additional microarchitecture enhancements that enable more efficient operation of all these instructions, and programming may be simplified because there are fewer coding restrictions.

3DNow! technology enabled fast frame rates on high-resolution 3D rendered scenes, amazing physical modeling of real-world environments, sharp and detailed 3D imaging, smooth video playback, and theater-quality audio. The new enhanced 3DNow! technology implemented in the AMD Athlon processor adds streaming and digital signal processing (DSP) technologies, which allow faster, more accurate speech recognition, DVD-quality audio and video, and streaming audio and video for a rich Internet experience.

The instructions described in this document are extensions to the instruction sets described in the *3DNow*!<sup>TM</sup> *Technology Manual*, order# 21928 and the *Multimedia Technology Manual*, order# 20726. The five new 3DNow! technology DSP extensions

Chapter 1

are summarized in Table 1 and fully described in Chapter 2. The 19 new instructions augmenting existing MMX technology are summarized in Table 2 and fully described in Chapter 3.

#### Table 1. 3DNow!<sup>™</sup> Technology DSP Extensions

| Operation | Function                                                          | Opcode / imm8 |

|-----------|-------------------------------------------------------------------|---------------|

| PF2IW     | Packed Floating-Point to Integer Word Conversion with Sign Extend | 0Fh 0Fh / 1Ch |

| PFNACC    | Packed Floating-Point Negative Accumulate                         | 0Fh 0Fh / 8Ah |

| PFPNACC   | Packed Floating-Point Mixed Positive-Negative Accumulate          | 0Fh 0Fh / 8Eh |

| PI2FW     | Packed Integer Word to Floating-Point Conversion                  | 0Fh 0Fh / 0Ch |

| PSWAPD    | Packed Swap Doubleword                                            | 0Fh 0Fh / BBh |

#### Table 2. MMX<sup>™</sup> Instruction Set Extensions

| Operation   | Function                                                  | Opcode / imm8 |

|-------------|-----------------------------------------------------------|---------------|

| MASKMOVQ    | Streaming (Cache Bypass) Store Using Byte Mask            | 0Fh F7h       |

| MOVNTQ      | Streaming (Cache Bypass) Store                            | 0Fh E7h       |

| PAVGB       | Packed Average of Unsigned Byte                           | 0Fh E0h       |

| PAVGW       | Packed Average of Unsigned Word                           | 0Fh E3h       |

| PEXTRW      | Extract Word into Integer Register                        | 0Fh C5h       |

| PINSRW      | Insert Word from Integer Register                         | 0Fh C4h       |

| PMAXSW      | Packed Maximum Signed Word                                | 0Fh EEh       |

| PMAXUB      | Packed Maximum Unsigned Byte                              | 0Fh DEh       |

| PMINSW      | Packed Minimum Signed Word                                | 0Fh EAh       |

| PMINUB      | Packed Minimum Unsigned Byte                              | 0Fh DAh       |

| PMOVMSKB    | Move Byte Mask to Integer Register                        | 0Fh D7h       |

| PMULHUW     | Packed Multiply High Unsigned Word                        | 0Fh E4h       |

| PREFETCHNTA | Move Data Closer to the Processor Using the NTA Reference | 0Fh 18h 0*    |

| PREFETCHT0  | Move Data Closer to the Processor Using the TO Reference  | 0Fh 18h 1*    |

| PREFETCHT1  | Move Data Closer to the Processor Using the T1 Reference  | 0Fh 18h 2*    |

| PREFETCHT2  | Move Data Closer to the Processor Using the T2 Reference  | 0Fh 18h 3*    |

| PSADBW      | Packed Sum of Absolute Byte Differences                   | 0Fh F6h       |

| PSHUFW      | Packed Shuffle Word                                       | 0Fh 70h       |

| SFENCE      | Store Fence                                               | 0Fh AEh / 7h  |

# 2

## Extensions to the 3DNow!™ Instruction Set

This chapter describes the five new DSP instructions added to the 3DNow! instruction set first defined in the 3DNow!<sup>TM</sup> Technology Manual, order# 21928. The five instructions enhance the performance of communications applications, including soft modems, soft ADSL, MP3, and Dolby Digital and Surround sound processing.

Programmers should check bit 30 of the Extended Feature Flags in the EDX register after executing extended function 8000\_0001h of the CPUID instruction. If bit 30 is set, the AMD processor supports these five instructions. For more information, refer to the AMD Processor Recognition Application Note, order# 20734.

Instruction definitions are in alphabetical order according to the instruction mnemonics.

AMD Extensions to the 3DNow!™ and MMX™ Instruction Sets

#### PF2IW

| mnemonic                                   |      |         | opcode / imm8 |                                                                                        | 3 description                                                                                                                                                  |  |

|--------------------------------------------|------|---------|---------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PF2IW mmreg1, mmreg2<br>PF2IW mmreg, mem64 |      |         | 0Fh 0Fh /     | 1Ch                                                                                    | Packed floating-point to integer word conversion with sign extend                                                                                              |  |

| Privilege:                                 |      |         | none          |                                                                                        |                                                                                                                                                                |  |

| Registers Affected:                        |      |         | MMX           |                                                                                        |                                                                                                                                                                |  |

| Flags Affected:                            |      |         | none          |                                                                                        |                                                                                                                                                                |  |

| <b>Exceptions Generated</b>                |      |         |               |                                                                                        |                                                                                                                                                                |  |

|                                            |      | Virtual |               |                                                                                        |                                                                                                                                                                |  |

| Exception                                  | Real | 8086    | Protected     | Descrip                                                                                | tion                                                                                                                                                           |  |

| Invalid opcode (6)                         | Х    | Х       | Х             | The emulate instruction bit (EM) of the control register (CR0) is set to 1.            |                                                                                                                                                                |  |

| Device not available (7)                   | Х    | Х       | Х             | The task switch bit (TS) of the control register (CR0) is set to 1.                    |                                                                                                                                                                |  |

| Stack exception (12)                       |      |         | Х             | During i                                                                               | nstruction execution, the stack segment limit was exceeded.                                                                                                    |  |

| General protection (13)                    |      |         | Х             |                                                                                        | nstruction execution, the effective address of one of the segment s used for the operand points to an illegal memory location.                                 |  |

| Segment overrun (13)                       | Х    | Х       |               | One of the instruction data operands falls outside the address range 00000h to 0FFFFh. |                                                                                                                                                                |  |

| Page fault (14)                            |      | Х       | Х             | A page fault resulted from the execution of the instruction.                           |                                                                                                                                                                |  |

| Floating-point exception pending (16)      | Х    | X       | Х             | An exception is pending due to the floating-point execution unit.                      |                                                                                                                                                                |  |

| Alignment check (17)                       |      | X       | Х             | and the                                                                                | igned memory reference resulted from the instruction execution,<br>alignment mask bit (AM) of the control register (CR0) is set to 1.<br>ected Mode, CPL = 3.) |  |

PF2IW converts a register containing single-precision floating-point operands to 16-bit signed integers using truncation. Arguments outside the range representable by signed 16-bit integers are saturated to the largest and smallest 16-bit integer, depending on their sign. All results are sign-extended to 32-bits. Table 3 on page 5 shows the numerical range of the PF2IW instruction.

22466D/0-March 2000

AMD Extensions to the 3DNow!™ and MMX™ Instruction Sets

"PF2IW mmreg1, mmreg2" performs the following operations:

```

IF (mmreg2[31:0] >= 2<sup>15</sup>)

THEN mmreg1[31:0] = 0x0000_7FFF

ELSE IF (mmreg2[31:0] <= -2<sup>15</sup>)

THEN mmreg1[31:0] = 0xFFFF_8000

ELSE mmreg1[31:0] = int(mmreg2[31:0])

IF (mmreg2[63:32] >= 2<sup>15</sup>)

THEN mmreg1[63:32] = 0x0000_7FFF

ELSE IF (mmreg2[63:32] <= -2<sup>15</sup>)

THEN mmreg1[63:32] = 0xFFFF_8000

ELSE mmreg1[63:32] = int(mmreg2[63:32])

```

"PF2IW mmreg, mem64" performs the following operations:

```

IF (mem64[31:0] >= 2<sup>15</sup>)

THEN mmreg[31:0] = 0x0000_7FFF

ELSE IF (mem64[31:0] <= -2<sup>15</sup>)

THEN mmreg[31:0] = 0xFFFF_8000

ELSE mmreg[31:0] = int(mem64[31:0])

```

```

IF (mem64[63:32] >= 2<sup>15</sup>)

THEN mmreg[63:32] = 0x0000_7FFF

ELSE IF (mem64[63:32] <= -2<sup>15</sup>)

THEN mmreg[63:32] = 0xFFFF_8000

ELSE mmreg[63:32] = int(mem64[63:32])

```

| Source 2                        | Source 1 and Destination |  |  |  |  |  |  |  |

|---------------------------------|--------------------------|--|--|--|--|--|--|--|

| 0                               | 0                        |  |  |  |  |  |  |  |

| Normal, abs(Source 1) <1        | 0                        |  |  |  |  |  |  |  |

| Normal, -32768 < Source 1 <= -1 | round to zero (Source 1) |  |  |  |  |  |  |  |

| Normal, 1 <= Source 1< 32768    | round to zero (Source 1) |  |  |  |  |  |  |  |

| Normal, Source 1 >= 32768       | 0x0000_7FFF              |  |  |  |  |  |  |  |

| Normal, Source 1 <= -32768      | 0xFFFF_8000              |  |  |  |  |  |  |  |

| Unsupported                     | Undefined                |  |  |  |  |  |  |  |

#### Table 3. Numerical Range for the PF2IW Instruction

**Related Instructions** See the PF2ID, PI2FW, and PI2FD instructions.

#### PFNACC

| mnemonic                               |      |         | opcode    | /imm8 description                                                                                                                                                                  |  |  |

|----------------------------------------|------|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PFNACC mmreg1, mn<br>PFNACC mmreg, men | 0    |         | 0Fh 0Fh   | n / 8Ah Packed floating-point negative accumulate                                                                                                                                  |  |  |

| Privilege:                             |      |         | none      |                                                                                                                                                                                    |  |  |

| Registers Affected:                    |      |         | MMX       |                                                                                                                                                                                    |  |  |

| Flags Affected:                        |      |         | none      |                                                                                                                                                                                    |  |  |

| <b>Exceptions Generated</b>            | :    |         |           |                                                                                                                                                                                    |  |  |

|                                        |      | Virtual |           |                                                                                                                                                                                    |  |  |

| Exception                              | Real | 8086    | Protected | Description                                                                                                                                                                        |  |  |

| Invalid opcode (6)                     | Х    | Х       | Х         | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                        |  |  |

| Device not available (7)               | Х    | Х       | Х         | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                                |  |  |

| Stack exception (12)                   |      |         | Х         | During instruction execution, the stack segment limit was exceeded.                                                                                                                |  |  |

| General protection (13)                |      |         | X         | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location.                                     |  |  |

| Segment overrun (13)                   | Х    | Х       |           | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                                                             |  |  |

| Page fault (14)                        |      | Х       | Х         | A page fault resulted from the execution of the instruction.                                                                                                                       |  |  |

| Floating-point exception pending (16)  | Х    | X       | X         | An exception is pending due to the floating-point execution unit.                                                                                                                  |  |  |

| Alignment check (17)                   |      | X       | Х         | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, $CPL = 3$ .) |  |  |

PFNACC performs negative accumulation of the two doublewords of the destination operand and the source operand. PFNACC then stores the results in the low and high words of the destination operand, respectively. Both operands are single-precision, floating-point operands with 24-bit significands.

"PFNACC mmreg1, mmreg2" performs the following operations:

```

temp = mmreg2

mmreg1[31:0] = mmreg1[31:0] - mmreg1[63:32]

mmreg1[63:32] = temp[31:0] - temp[63:32]

```

"PFNACC mmreg, mem64" performs the following operations:

mmreg[31:0] = mmreg[31:0] - mmreg[63:32]

mmreg[63:32] = mem64[31:0] - mem64[63:32]

**Related Instructions** See the PFACC and PFPNACC instructions.

#### PFPNACC

| mnemonic                               |      |                 | opcode / imm8 |                                                                                                                                                | description                                                                                                                                              |  |

|----------------------------------------|------|-----------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PFPNACC mmreg1, m<br>PFPNACC mmreg, me | 2    | 0Fh 0Fh         | n / 8Eh       | Packed floating-point mixed positive-negative accumulate                                                                                       |                                                                                                                                                          |  |

| Privilege:                             |      |                 | none          |                                                                                                                                                |                                                                                                                                                          |  |

| Registers Affected:                    |      |                 | MMX           |                                                                                                                                                |                                                                                                                                                          |  |

| Flags Affected:                        |      |                 | none          |                                                                                                                                                |                                                                                                                                                          |  |

| <b>Exceptions Generated</b>            |      |                 |               |                                                                                                                                                |                                                                                                                                                          |  |

| Exception                              | Real | Virtual<br>8086 | Protected     | Descriptio                                                                                                                                     | on                                                                                                                                                       |  |

| Invalid opcode (6)                     | Х    | Х               | Х             | The emula                                                                                                                                      | te instruction bit (EM) of the control register (CR0) is set to 1.                                                                                       |  |

| Device not available (7)               | Х    | Х               | Х             | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                            |                                                                                                                                                          |  |

| Stack exception (12)                   |      |                 | Х             | During ins                                                                                                                                     | truction execution, the stack segment limit was exceeded.                                                                                                |  |

| General protection (13)                |      |                 | X             | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location. |                                                                                                                                                          |  |

| Segment overrun (13)                   | Х    | Х               |               | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                         |                                                                                                                                                          |  |

| Page fault (14)                        |      | Х               | Х             | A page fault resulted from the execution of the instruction.                                                                                   |                                                                                                                                                          |  |

| Floating-point exception pending (16)  | Х    | Х               | X             | An exception is pending due to the floating-point execution unit.                                                                              |                                                                                                                                                          |  |

| Alignment check (17)                   |      | X               | Х             | and the ali                                                                                                                                    | ned memory reference resulted from the instruction execution,<br>ignment mask bit (AM) of the control register (CR0) is set to 1.<br>ied Mode, CPL = 3.) |  |

PFPNACC performs mixed negative and positive accumulation of the two doublewords of the destination operand and the source operand. PFPNACC then stores the results in the low and high words of the destination operand, respectively. Both operands are single-precision, floating-point operands with 24-bit significands.

"PFPNACC mmreg1, mmreg2" performs the following operations:

```

temp = mmreg2

mmreg1[31:0] = mmreg1[31:0] - mmreg1[63:32]

mmreg1[63:32] = temp[31:0] + temp[63:32]

```

"PFPNACC mmreg, mem64" performs the following operations:

mmreg[31:0] = mmreg[31:0] - mmreg[63:32]

mmreg[63:32] = mem64[31:0] + mem64[63:32]

**Related Instructions** See the PFACC and PFNACC instructions.

#### PI2FW

| mnemonic                               |      | opcode/         | imm8 description |                                                                                                                                                                                    |  |  |

|----------------------------------------|------|-----------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pl2FW mmreg1, mmr<br>Pl2FW mmreg, mem6 | •    |                 | 0Fh 0Fh /        | 0Ch Packed 16-bit integer to floating-point conversion                                                                                                                             |  |  |

| Privilege:                             |      |                 | none             |                                                                                                                                                                                    |  |  |

| Registers Affected:                    |      |                 | MMX              |                                                                                                                                                                                    |  |  |

| Flags Affected:                        |      |                 | none             |                                                                                                                                                                                    |  |  |

| <b>Exceptions Generated</b>            |      |                 |                  |                                                                                                                                                                                    |  |  |

| Exception                              | Real | Virtual<br>8086 | Protected        | Description                                                                                                                                                                        |  |  |

| Invalid opcode (6)                     | Х    | Х               | Х                | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                        |  |  |

| Device not available (7)               | Х    | Х               | Х                | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                                |  |  |

| Stack exception (12)                   |      |                 | Х                | During instruction execution, the stack segment limit was exceeded.                                                                                                                |  |  |

| General protection (13)                |      |                 | Х                | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location.                                     |  |  |

| Segment overrun (13)                   | Х    | X               |                  | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                                                             |  |  |

| Page fault (14)                        |      | Х               | Х                | A page fault resulted from the execution of the instruction.                                                                                                                       |  |  |

| Floating-point exception pending (16)  | Х    | X               | Х                | An exception is pending due to the floating-point execution unit.                                                                                                                  |  |  |

| Alignment check (17)                   |      | X               | Х                | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, $CPL = 3$ .) |  |  |

PI2FW converts a register containing signed, 16-bit integers to single-precision, floating-point operands.

"PI2FW mmreg1, mmreg2" performs the following operations:

mmreg1[31:0] = float(mmreg2[15:0])

mmreg1[63:32] = float(mmreg2[47:32])

"PI2FW mmreg, mem64" performs the following operations:

mmreg[31:0] = float(mem64[15:0])

mmreg[63:32] = float(mem64[47:32])

**Related Instructions** See the PI2FD, PF2IW, and PF2ID instructions.

#### **PSWAPD**

| mnemonic                               |      |                 | орсо      | de / imm8 description                                                                                                                                                           |  |  |

|----------------------------------------|------|-----------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PSWAPD mmreg1, mr<br>PSWAPD mmreg, mer | •    |                 | 0Fh C     | Fh / BBh Packed swap doubleword                                                                                                                                                 |  |  |

| Privilege:                             |      |                 | none      |                                                                                                                                                                                 |  |  |

| Registers Affected:                    |      |                 | MMX       |                                                                                                                                                                                 |  |  |

| Flags Affected:                        |      |                 | none      |                                                                                                                                                                                 |  |  |

| <b>Exceptions Generated</b>            |      |                 |           |                                                                                                                                                                                 |  |  |

| Exception                              | Real | Virtual<br>8086 | Protected | Description                                                                                                                                                                     |  |  |

| Invalid opcode (6)                     | Х    | Х               | Х         | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                     |  |  |

| Device not available (7)               | Х    | Х               | Х         | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                             |  |  |

| Stack exception (12)                   |      |                 | Х         | During instruction execution, the stack segment limit was exceeded.                                                                                                             |  |  |

| General protection (13)                |      |                 | X         | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location.                                  |  |  |

| Segment overrun (13)                   | Х    | Х               |           | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                                                          |  |  |

| Page fault (14)                        |      | Х               | Х         | A page fault resulted from the execution of the instruction.                                                                                                                    |  |  |

| Floating-point exception pending (16)  | Х    | Х               | X         | An exception is pending due to the floating-point execution unit.                                                                                                               |  |  |

| Alignment check (17)                   |      | X               | Х         | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, CPL = 3.) |  |  |

The PSWAPD instruction swaps or reverses the upper and lower doublewords of the source operand.

"PSWAPD mmreg1, mmreg2" performs the following operations:

temp = mmreg2

mmreg1[63:32] = temp[31:0]

mmreg1[31:0] = temp[63:32]

"PSWAPD mmreg, mem64" performs the following operations:

mmreg[63:32] = mem64[31:0] mmreg[31:0] = mem64[63:32]

####

AMD Extensions to the 3DNow!<sup>™</sup> and MMX<sup>™</sup> Instruction Sets

AMD Extensions to the 3DNow!™ and MMX™ Instruction Sets

# 3

## Extensions to the MMX<sup>™</sup> Instruction Set

This chapter describes 19 new instructions added to the MMX instruction set defined in the  $AMD-K6^{\textcircled{m}}MMX^{TM}$  Enhanced Processor Multimedia Technology Manual, order# 20726. Twelve of the instructions improve multimedia-enhanced integer math calculations used in such applications as speech recognition and high-quality video processing. Seven instructions are dedicated to efficiently moving multimedia data into and out of the processor.

Programmers should check bit 22 of the Extended Feature Flags in the EDX register after executing extended function 8000\_0001h of the CPUID instruction. If bit 22 is set, the AMD processor supports these 19 instructions. See the *AMD Processor Recognition Application Note*, order# 20734 for more information.

Instruction definitions are in alphabetical order according to the instruction mnemonics.

#### MASKMOVQ

| mnemonic                              |       |                 |           | pcode                                                                                                                                          | description                                                                                                                                    |  |

|---------------------------------------|-------|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MASKMOVQ mmreg1                       | , mmr | eg2 (edi        | ) 0       | Fh F7h                                                                                                                                         | Streaming (cache bypass) store using byte mask                                                                                                 |  |

| Privilege:                            |       |                 | none      |                                                                                                                                                |                                                                                                                                                |  |

| Registers Affected:                   |       |                 | MMX       |                                                                                                                                                |                                                                                                                                                |  |

| Flags Affected:                       |       |                 | none      |                                                                                                                                                |                                                                                                                                                |  |

| <b>Exceptions Generated</b>           | :     |                 |           |                                                                                                                                                |                                                                                                                                                |  |

| Exception                             | Real  | Virtual<br>8086 | Protected | Description                                                                                                                                    |                                                                                                                                                |  |

| Invalid opcode (6)                    | Х     | Х               | Х         | The emulate inst                                                                                                                               | ruction bit (EM) of the control register (CR0) is set to 1.                                                                                    |  |

| Device not available (7)              | Х     | Х               | Х         | The task switch                                                                                                                                | bit (TS) of the control register (CR0) is set to 1.                                                                                            |  |

| Stack exception (12)                  |       |                 | Х         | During instructi                                                                                                                               | on execution, the stack segment limit was exceeded.                                                                                            |  |

| General protection (13)               |       |                 | X         | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location. |                                                                                                                                                |  |

| Segment overrun (13)                  | Х     | Х               |           | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                         |                                                                                                                                                |  |

| Page fault (14)                       |       | Х               | Х         | A page fault res                                                                                                                               | ulted from the execution of the instruction.                                                                                                   |  |

| Floating-point exception pending (16) | Х     | Х               | Х         | An exception is                                                                                                                                | pending due to the floating-point execution unit.                                                                                              |  |

| Alignment check (17)                  |       | X               | Х         |                                                                                                                                                | nemory reference resulted from the instruction execution,<br>ent mask bit (AM) of the control register (CR0) is set to 1.<br>ode, $CPL = 3$ .) |  |

The MASKMOVQ instruction conditionally stores individual bytes of an MMX register to a memory location specified by the edi register, while using the byte mask in a second MMX register. The MASKMOVQ instruction acts as a streaming store to minimize cache pollution. It is used to store data without first reading in old data (no write allocate).

#### "MASKMOVQ mmreg1, mmreg2 (edi)" performs the following operations:

```

memory[edi][63:56] = mmreg2[63] ? mmreg1[63:56] : memory[edi][63:56]

memory[edi][55:48] = mmreg2[55] ? mmreg1[55:48] : memory[edi][55:48]

memory[edi][47:40] = mmreg2[47] ? mmreg1[47:40] : memory[edi][47:40]

memory[edi][39:32] = mmreg2[39] ? mmreg1[39:32] : memory[edi][39:32]

memory[edi][31:24] = mmreg2[31] ? mmreg1[31:24] : memory[edi][31:24]

memory[edi][23:16] = mmreg2[23] ? mmreg1[23:16] : memory[edi][23:16]

memory[edi][15:8] = mmreg2[15] ? mmreg1[15:8] : memory[edi][15:8]

memory[edi][7:0] = mmreg2[7] ? mmreg1[7:0] : memory[edi][7:0]

```

#### MOVNTQ

| mnemonic                                                                     | opcod |                 | pcode               | description                                                                                                                                                                     |                                                                                                                |  |  |

|------------------------------------------------------------------------------|-------|-----------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| MOVNTQ mem64, mr                                                             | nreg  |                 | 0                   | Fh E7h                                                                                                                                                                          | Streaming (cache bypass) store                                                                                 |  |  |

| Privilege:<br>Registers Affected:<br>Flags Affected:<br>Exceptions Generated | :     |                 | none<br>MMX<br>none |                                                                                                                                                                                 |                                                                                                                |  |  |

| Exception                                                                    | Real  | Virtual<br>8086 | Protected           | Description                                                                                                                                                                     |                                                                                                                |  |  |

| Invalid opcode (6)                                                           | Х     | Х               | Х                   | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                     |                                                                                                                |  |  |

| Device not available (7)                                                     | Х     | Х               | Х                   | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                             |                                                                                                                |  |  |

| Stack exception (12)                                                         |       |                 | Х                   | During instructi                                                                                                                                                                | on execution, the stack segment limit was exceeded.                                                            |  |  |

| General protection (13)                                                      |       |                 | X                   |                                                                                                                                                                                 | on execution, the effective address of one of the segment or the operand points to an illegal memory location. |  |  |

| Segment overrun (13)                                                         | Х     | Х               |                     | One of the instr<br>to 0FFFFh.                                                                                                                                                  | uction data operands falls outside the address range 00000h                                                    |  |  |

| Page fault (14)                                                              |       | Х               | Х                   | A page fault res                                                                                                                                                                | ulted from the execution of the instruction.                                                                   |  |  |

| Floating-point exception pending (16)                                        | Х     | Х               | X                   | An exception is                                                                                                                                                                 | pending due to the floating-point execution unit.                                                              |  |  |

| Alignment check (17)                                                         |       | X               | Х                   | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, CPL = 3.) |                                                                                                                |  |  |

The MOVNTQ instruction stores individual bytes of an MMX register to memory. The MOVNTQ instruction acts as a streaming store to minimize cache pollution. It is used to store data without first reading in old data (no write allocate).

"MOVNTQ mem64, mmreg" performs the following operations:

mem64[63:0] = mmreg

#### PAVGB

| mnemonic                               |      |                 | opcode    | description                                                                                                                                                                        |

|----------------------------------------|------|-----------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAVGB mmreg1, mmr<br>PAVGB mmreg, meme | •    |                 | 0Fh E0ł   | n Packed average of unsigned byte                                                                                                                                                  |

| Privilege:                             |      |                 | none      |                                                                                                                                                                                    |

| <b>Registers Affected:</b>             |      |                 | MMX       |                                                                                                                                                                                    |

| Flags Affected:                        |      |                 | none      |                                                                                                                                                                                    |

| <b>Exceptions Generated</b>            | :    |                 |           |                                                                                                                                                                                    |

| Exception                              | Real | Virtual<br>8086 | Protected | Description                                                                                                                                                                        |

| Invalid opcode (6)                     | Х    | Х               | Х         | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                        |

| Device not available (7)               | Х    | Х               | Х         | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                                |

| Stack exception (12)                   |      |                 | Х         | During instruction execution, the stack segment limit was exceeded.                                                                                                                |

| General protection (13)                |      |                 | Х         | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location.                                     |

| Segment overrun (13)                   | Х    | Х               |           | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                                                             |

| Page fault (14)                        |      | Х               | Х         | A page fault resulted from the execution of the instruction.                                                                                                                       |

| Floating-point exception pending (16)  | Х    | X               | Х         | An exception is pending due to the floating-point execution unit.                                                                                                                  |

| Alignment check (17)                   |      | Х               | Х         | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, $CPL = 3$ .) |

The PAVGB instruction produces the rounded up averages of the eight unsigned 8-bit integer values in the source operand (an MMX register or a 64-bit memory location) and the eight corresponding unsigned 8-bit integer values in the destination operand (an MMX register). It does so by adding the source and destination byte values to get a 9-bit unsigned intermediate value. The intermediate value is then incremented by one and finally shifted to the right by one bit position. The eight unsigned 8-bit results are stored in the MMX register specified as the destination operand.

The PAVGB instruction is identical to the 3DNow! PAVGUSB instruction and can be used for pixel averaging in MPEG-2 motion compensation and video scaling operations.

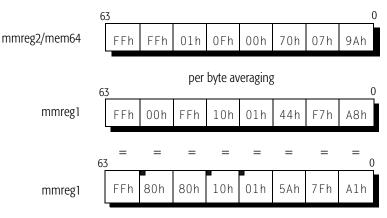

#### Functional Illustration of the PAVGB Instruction

Indicates a value that was rounded-up

The following list explains the functional illustration of the PAVGB instruction:

- The rounded byte average of FFh and FFh is FFh.

- The rounded byte average of FFh and 00h is 80h.

- The rounded byte average of 01h and FFh is also 80h.

- The rounded byte average of 0Fh and 10h is 10h.

- The rounded byte average of 00h and 01h is 01h.

- The rounded byte average of 70h and 44h is 5Ah.

- The rounded byte average of 07h and F7h is 7Fh.

- The rounded byte average of 9Ah and A8h is A1h.

#### "PAVGB mmreg1, mmreg2" performs the following operations:

```

mmreg1[7:0] = (mmreg1[7:0] + mmreg2[7:0] + 1) >> 1

mmreg1[15:8] = (mmreg1[15:8] + mmreg2[15:8] + 1) >> 1

mmreg1[23:16] = (mmreg1[23:16] + mmreg2[23:16] + 1) >> 1

mmreg1[31:24] = (mmreg1[31:24] + mmreg2[31:24] + 1) >> 1

mmreg1[39:32] = (mmreg1[39:32] + mmreg2[39:32] + 1) >> 1

mmreg1[47:40] = (mmreg1[47:40] + mmreg2[47:40] + 1) >> 1

mmreg1[55:48] = (mmreg1[55:48] + mmreg2[55:48] + 1) >> 1

mmreg1[63:56] = (mmreg1[63:56] + mmreg2[63:56] + 1) >> 1

```

#### "PAVGB mmreg, mem64" performs the following operations:

| mmreg[7:0]   | = | (mmreg[7:0]   | + | mem64[7:0]   | + | 1) > | >> | 1 |

|--------------|---|---------------|---|--------------|---|------|----|---|

| mmreg[15:8]  | = | (mmreg[15:8]  | + | mem64[15:8]  | + | 1) > | >> | 1 |

| mmreg[23:16] | = | (mmreg[23:16] | + | mem64[23:16] | + | 1) > | >> | 1 |

| mmreg[31:24] | = | (mmreg[31:24] | + | mem64[31:24] | + | 1) > | >> | 1 |

| mmreg[39:32] | = | (mmreg[39:32] | + | mem64[39:32] | + | 1) > | >> | 1 |

| mmreg[47:40] | = | (mmreg[47:40] | + | mem64[47:40] | + | 1) > | >> | 1 |

| mmreg[55:48] | = | (mmreg[55:48] | + | mem64[55:48] | + | 1) > | >> | 1 |

| mmreg[63:56] | = | (mmreg[63:56] | + | mem64[63:56] | + | 1) > | >> | 1 |

**Related Instructions** See the PAVGW instruction.

#### PAVGW

| mnemonic                              |      |         | opcode    | description                                                                                                                                                                        |

|---------------------------------------|------|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAVGW mmreg1, mm<br>PAVGW mmreg, mem  | •    |         | 0Fh E3h   | n Packed average of unsigned word                                                                                                                                                  |

| Privilege:                            |      |         | none      |                                                                                                                                                                                    |

| Registers Affected:                   |      |         | MMX       |                                                                                                                                                                                    |

| Flags Affected:                       |      |         | none      |                                                                                                                                                                                    |

| <b>Exceptions Generated</b>           | :    |         |           |                                                                                                                                                                                    |

|                                       |      | Virtual |           |                                                                                                                                                                                    |

| Exception                             | Real | 8086    | Protected | Description                                                                                                                                                                        |

| Invalid opcode (6)                    | Х    | Х       | Х         | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                        |

| Device not available (7)              | Х    | Х       | Х         | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                                |

| Stack exception (12)                  |      |         | Х         | During instruction execution, the stack segment limit was exceeded.                                                                                                                |

| General protection (13)               |      |         | X         | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location.                                     |

| Segment overrun (13)                  | Х    | Х       |           | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                                                             |

| Page fault (14)                       |      | Х       | Х         | A page fault resulted from the execution of the instruction.                                                                                                                       |

| Floating-point exception pending (16) | Х    | Х       | X         | An exception is pending due to the floating-point execution unit.                                                                                                                  |

| Alignment check (17)                  |      | Х       | X         | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, $CPL = 3$ .) |

The PAVGW instruction is the same as the PAVGB instruction, except it operates on packed unsigned words instead. PAVGW produces the rounded up averages of the four unsigned 16-bit integer values in the source operand (an MMX register or a 64-bit memory location) and the four corresponding unsigned 16-bit integer values in the destination operand (an MMX register). It does so by adding the source and destination byte values to get a 17-bit unsigned intermediate value. The intermediate value is then incremented by one and finally shifted to the right by one bit position. The four unsigned 16-bit results are stored in the MMX register specified as the destination operand.

"PAVGW mmreg1, mmreg2" performs the following operations:

```

mmreg1[15:0] = (mmreg1[15:0] + mmreg2[15:0] + 1) >> 1

mmreg1[31:16] = (mmreg1[31:16] + mmreg2[31:16] + 1) >> 1

mmreg1[47:32] = (mmreg1[47:32] + mmreg2[47:32] + 1) >> 1

mmreg1[63:48] = (mmreg1[63:48] + mmreg2[63:48] + 1) >> 1

```

AMD Extensions to the 3DNow!™ and MMX™ Instruction Sets

#### "PAVGW mmreg, mem64" performs the following operations:

mmreg[15:0] = (mmreg[15:0] + mem64[15:0] + 1) >> 1

mmreg[31:16] = (mmreg[31:16] + mem64[31:16] + 1) >> 1

mmreg[47:32] = (mmreg[47:32] + mem64[47:32] + 1) >> 1

mmreg[63:48] = (mmreg[63:48] + mem64[63:48] + 1) >> 1

**Related Instructions** See the PAVGB instruction.

#### PEXTRW

| mnemonic                                                                     |      |                 | opcode              | description                                                                                                                                                                        |  |  |  |

|------------------------------------------------------------------------------|------|-----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PEXTRW reg32, mmreg, imm8                                                    |      |                 | 0Fh C5l             | h Extract word into integer register                                                                                                                                               |  |  |  |

| Privilege:<br>Registers Affected:<br>Flags Affected:<br>Exceptions Generated | :    |                 | none<br>MMX<br>none |                                                                                                                                                                                    |  |  |  |

| Exception                                                                    | Real | Virtual<br>8086 | Protected           | Description                                                                                                                                                                        |  |  |  |

| Invalid opcode (6)                                                           | Х    | Х               | Х                   | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                        |  |  |  |

| Device not available (7)                                                     | Х    | Х               | Х                   | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                                |  |  |  |

| Stack exception (12)                                                         |      |                 | Х                   | During instruction execution, the stack segment limit was exceeded.                                                                                                                |  |  |  |

| General protection (13)                                                      |      |                 | X                   | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location.                                     |  |  |  |

| Segment overrun (13)                                                         | Х    | Х               |                     | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                                                             |  |  |  |

| Page fault (14)                                                              |      | Х               | Х                   | A page fault resulted from the execution of the instruction.                                                                                                                       |  |  |  |

| Floating-point exception pending (16)                                        | Х    | Х               | Х                   | An exception is pending due to the floating-point execution unit.                                                                                                                  |  |  |  |

| Alignment check (17)                                                         |      | Х               | Х                   | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, $CPL = 3$ .) |  |  |  |

The PEXTRW instruction extracts one of the four words pointed to by imm8 from an MMX register and stores that into the least significant word of a 32-bit integer register.

"PEXTRW reg32, mmreg, imm8" performs the following operations:

```

index = imm8[1:0] * 16

reg32[31:16] = 0

reg32[15:0] = mmreg[index+15:index]

```

**Related Instructions** See the PINSRW instruction.

AMD Extensions to the 3DNow!™ and MMX™ Instruction Sets

#### PINSRW

| mnemonic                                                                     |      | оро     | code description    |                                                                                                                                                                                    |  |  |  |

|------------------------------------------------------------------------------|------|---------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PINSRW mmreg, reg32, imm8<br>PINSRW mmreg, mem16, imm8                       |      |         | 0Fł                 | C4h Insert word from integer register                                                                                                                                              |  |  |  |

| Privilege:<br>Registers Affected:<br>Flags Affected:<br>Exceptions Generated | :    |         | none<br>MMX<br>none |                                                                                                                                                                                    |  |  |  |

|                                                                              | -    | Virtual |                     |                                                                                                                                                                                    |  |  |  |

| Exception                                                                    | Real | 8086    | Protected           | Description                                                                                                                                                                        |  |  |  |

| Invalid opcode (6)                                                           | Х    | Х       | Х                   | The emulate instruction bit (EM) of the control register (CR0) is set to 1.                                                                                                        |  |  |  |

| Device not available (7)                                                     | Х    | Х       | Х                   | The task switch bit (TS) of the control register (CR0) is set to 1.                                                                                                                |  |  |  |

| Stack exception (12)                                                         |      |         | Х                   | During instruction execution, the stack segment limit was exceeded.                                                                                                                |  |  |  |

| General protection (13)                                                      |      |         | Х                   | During instruction execution, the effective address of one of the segment registers used for the operand points to an illegal memory location.                                     |  |  |  |

| Segment overrun (13)                                                         | Х    | X       |                     | One of the instruction data operands falls outside the address range 00000h to 0FFFFh.                                                                                             |  |  |  |

| Page fault (14)                                                              |      | Х       | Х                   | A page fault resulted from the execution of the instruction.                                                                                                                       |  |  |  |

| Floating-point exception pending (16)                                        | Х    | X       | X                   | An exception is pending due to the floating-point execution unit.                                                                                                                  |  |  |  |

| Alignment check (17)                                                         |      | X       | Х                   | An unaligned memory reference resulted from the instruction execution, and the alignment mask bit (AM) of the control register (CR0) is set to 1. (In Protected Mode, $CPL = 3$ .) |  |  |  |

The PINSRW instruction inserts the least significant word of the source operand (an integer register or a 16-bit memory location) into one of the four words of the destination operand (an MMX register).

"PINSRW mmreg, reg32, imm8" performs the following operations:

```

index = imm8[1:0] * 16

temp1 = 0

temp1[index+15:index] = reg32[15:0]

temp2 = mmreg

temp2[index+15:index] = 0

mmreg = temp1 | temp2

```

"PINSRW mmreg, mem16, imm8" performs the following operations:

```

index = imm8[1:0] * 16

temp1 = 0

temp1[index+15:index] = mem16[15:0]

temp2 = mmreg

temp2[index+15:index] = 0

mmreg = temp1 | temp2

```

**Related Instructions** See the PEXTRW instruction.

20

#### **PMAXSW**

| mnemonic                               |      |         | opcode    | description                                                                                                                                                                        |

|----------------------------------------|------|---------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMAXSW mmreg1, mi<br>PMAXSW mmreg, mei | •    |         | 0Fh EEf   | n Packed maximum signed word                                                                                                                                                       |

| Privilege:                             |      |         | none      |                                                                                                                                                                                    |