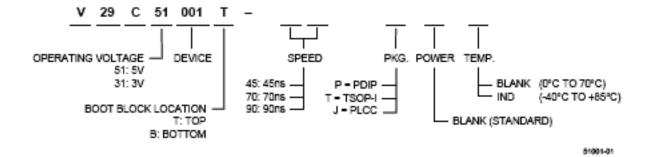

## F29C51001T/F29C51001B 1 MEGABIT (131,072 x 8 BIT) 5 VOLT CMOS FLASH MEMORY

#### Features

- 128Kx8-bit Organization

- Address Access Time: 45, 70, 90 ns

- Single 5V ± 10% Power Supply

- Sector Erase Mode Operation

- 8KB Boot Block (lockable)

- 512 bytes per Sector, 256 Sectors

- Sector-Erase Cycle Time: 10ms (Max)

- Byte-Program Cycle Time: 20μs (Max)

- Minimum 10,000 Erase-Program Cycles

- Low power dissipation

- Active Read Current: 20mA (Typ)

- Active Program Current: 30mA (Typ)

- Standby Current: 100µA (Max)

- Hardware Data Protection

- Low V<sub>CC</sub> Program Inhibit Below 3.2V

- Self-timed program/erase operations with endof-cycle detection

- DATA Polling

- Toggle Bit

- CMOS and TTL Interface

- Available in two versions

- F29C51001T (Top Boot Block)

- F29C51001B (Bottom Boot Block)

- Packages:

- 32-pin Plastic DIP

- 32-pin TSOP-I

- 32-pin PLCC

### Description

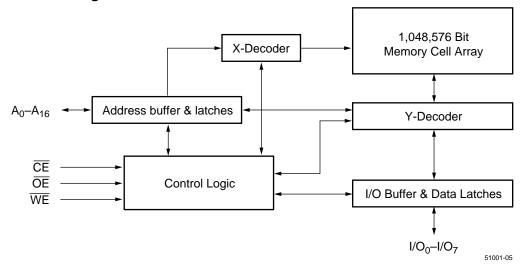

The F29C51001T/F29C51001B is a high speed 131,072 x 8 bit CMOS flash memory. Programming or erasing the device is done with a single 5 Volt power supply. The device has separate chip enable CE, program enable WE, and output enable OE controls to eliminate bus contention.

The F29C51001T/F29C51001B offers a combination of features: Boot Block with Sector Erase Mode. The end of program/erase cycle is detected by DATA Polling of I/O<sub>7</sub> or by the Toggle Bit I/O<sub>6</sub>.

The F29C51001T/F29C51001B features a sector erase operation which allows each sector to be erased and reprogrammed without affecting data stored in other sectors. The device also supports full chip erase.

Boot block architecture enables the device to boot from a protected sector loaded either at the top (F29C51001T) or the bottom (F29C51001B) sector. All inputs and outputs are CMOS and TTL compatible.

The F29C51001T/F29C51001B is ideal for applications that require updatable code and data storage.

## Device Usage Chart

| Operating            | Pac | ckage Outl | ine | Acc | cess Time | (ns) | Power | Tomporatura         |

|----------------------|-----|------------|-----|-----|-----------|------|-------|---------------------|

| Temperature<br>Range | Р   | Т          | J   | 45  | 70        | 90   | Std.  | Temperature<br>Mark |

| 0°C to 70°C          |     |            |     |     |           |      |       | Blank               |

| -40°C to +85°C       |     |            |     | -   |           |      |       | I                   |

### F29C51001T/F29C51001B

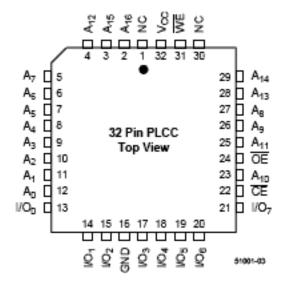

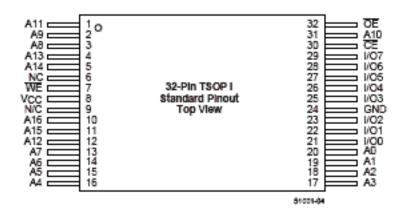

### Pin Configurations

|      |             |    | _    |      |       |   |      |

|------|-------------|----|------|------|-------|---|------|

| N/C  | ₫1          |    |      | _    | 32    | Þ | Voc  |

| A16  | <b>d</b> 2  |    |      |      | 31    | Þ | WE   |

| A15  | ₫3          |    |      |      | 30    | Þ | NC   |

| A12  | ₫4          |    |      |      | 29    | Þ | A14  |

| A7   | ₫5          |    |      |      | 28    | Þ | A13  |

| A6   | ₫6          |    |      |      | 27    | þ | A8   |

| A5   | ₫7          | 32 | Pin  | PDIP | 26    | Þ | A9   |

| A4   | ₫8          | 1  | Гор\ | ∕iew | 25    | Þ | A11  |

| A3   | ₫9          |    |      |      | 24    | Ь | Œ    |

| A2   | <b>d</b> 1  | 0  |      |      | 23    | Ь | A10  |

| A1   | d1          | 1  |      |      | 22    | Ь | CE   |

| AD   | <b>d</b> 13 | 2  |      |      | 21    | Ь | I/O7 |

| 1/00 | <b>d</b> 13 | 3  |      |      | 20    | Ь | 1/06 |

| 1/01 | <b>d</b> 1  | 4  |      |      | 19    | Ь | 1/05 |

| 1/02 | <b>d</b> 18 | 5  |      |      | 18    | Ь | I/O4 |

| GND  | <b>d</b> 1  | 6  |      |      | 17    | þ | 1/03 |

|      | _           |    |      | 5100 | 01-02 |   |      |

#### Pin Names

| A <sub>0</sub> -A <sub>16</sub>    | Address Inputs        |

|------------------------------------|-----------------------|

| I/O <sub>0</sub> -I/O <sub>7</sub> | Data Input/Output     |

| CE                                 | Chip Enable           |

| ŌĒ                                 | Output Enable         |

| WE                                 | Program Enable        |

| V <sub>cc</sub>                    | 5V ± 10% Power Supply |

| GND                                | Ground                |

| NC                                 | No Connect            |

#### F29C51001T/F29C51001B

#### Functional Block Diagram

### Capacitance (1,2)

| Symbol           | Parameter               | Test mSetup          | Тур. | Max. | Units |

|------------------|-------------------------|----------------------|------|------|-------|

| C <sub>IN</sub>  | Input Capacitance       | V <sub>IN</sub> = 0  | 6    | 8    | pF    |

| C <sub>OUT</sub> | Output Capacitance      | V <sub>OUT</sub> = 0 | 8    | 12   | pF    |

| C <sub>IN2</sub> | Control Pin Capacitance | V <sub>IN</sub> = 0  | 8    | 10   | pF    |

#### NOTE:

- 1. Capacitance is sampled and not 100% tested.

- 2.  $T_A = 25$ °C,  $V_{CC} = 5V \pm 10$ %, f = 1 MHz.

## Latch Up Characteristics<sup>(1)</sup>

| Parameter                                                                    | Min. | Max.                | Unit |

|------------------------------------------------------------------------------|------|---------------------|------|

| Input Voltage with Respect to GND on A <sub>9</sub> , $\overline{\text{OE}}$ | -1   | +13                 | V    |

| Input Voltage with Respect to GND on I/O, address or control pins            | -1   | V <sub>CC</sub> + 1 | V    |

| V <sub>CC</sub> Current                                                      | -100 | +100                | mA   |

#### NOTE:

1. Includes all pins except  $V_{CC}$ . Test conditions:  $V_{CC} = 5V$ , one pin at a time.

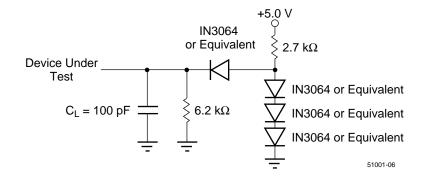

#### AC Test Load

#### F29C51001T/F29C51001B

## Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Parameter                                                   | Commercial   | Extended     | Unit |

|------------------|-------------------------------------------------------------|--------------|--------------|------|

| V <sub>IN</sub>  | Input Voltage (input or I/O pins)                           | -2 to +7     | -2 to +7     | V    |

| V <sub>IN</sub>  | Input Voltage (A <sub>9</sub> pin, $\overline{\text{OE}}$ ) | -2 to +13    | -2 to +13    | V    |

| V <sub>CC</sub>  | Power Supply Voltage                                        | -0.5 to +5.5 | -0.5 to +5.5 | V    |

| T <sub>STG</sub> | Storage Temerpature (Plastic)                               | -65 to +125  | -65 to +150  | °C   |

| T <sub>OPR</sub> | Operating Temperature                                       | 0 to +70     | -40 to + 125 | °C   |

| I <sub>OUT</sub> | Short Circuit Current <sup>(2)</sup>                        | 200 (Max.)   | 200 (Max.)   | mA   |

#### NOTE:

#### DC Electrical Characteristics

(over the commercial operating range)

| Parameter<br>Name | Parameter                            | Test Conditions                                                                                                                                                                                                                                                                                                       | Min. | Max. | Unit |

|-------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>IL</sub>   | Input LOW Voltage                    | V <sub>CC</sub> = V <sub>CC</sub> Min.                                                                                                                                                                                                                                                                                | _    | 0.8  | V    |

| V <sub>IH</sub>   | Input HIGH Voltage                   | V <sub>CC</sub> = V <sub>CC</sub> Max.                                                                                                                                                                                                                                                                                | 2    | _    | V    |

| I <sub>IL</sub>   | Input Leakage Current                | $V_{IN} = GND$ to $V_{CC}$ , $V_{CC} = V_{CC}$ Max.                                                                                                                                                                                                                                                                   | _    | ±1   | μΑ   |

| I <sub>OL</sub>   | Output Leakage Current               | $V_{OUT} = GND$ to $V_{CC}$ , $V_{CC} = V_{CC}$ Max.                                                                                                                                                                                                                                                                  | _    | ±1   | μΑ   |

| V <sub>OL</sub>   | Output LOW Voltage                   | V <sub>CC</sub> = V <sub>CC</sub> Min., I <sub>OL</sub> = 2.1mA                                                                                                                                                                                                                                                       | _    | 0.4  | V    |

| V <sub>OH</sub>   | Output HIGH Voltage                  | V <sub>CC</sub> = V <sub>CC</sub> Min, I <sub>OH</sub> = -400μA                                                                                                                                                                                                                                                       | 2.4  | _    | V    |

| I <sub>CC1</sub>  | Read Current                         | $\overline{\text{CE}} = \overline{\text{OE}} = \text{V}_{\text{IL}}, \overline{\text{WE}} = \text{V}_{\text{IH}}, \text{ all I/Os open},$ Address input = $\text{V}_{\text{IL}}/\text{V}_{\text{IH}}, \text{ at f} = \text{1/t}_{\text{RC}} \text{ Min.},$ $\text{V}_{\text{CC}} = \text{V}_{\text{CC}} \text{ Max.}$ | _    | 40   | mA   |

| I <sub>CC2</sub>  | Program Current                      | $\overline{CE} = \overline{WE} = VIL, \overline{OE} = V_{IH}, V_{CC} = V_{CC} Max.$                                                                                                                                                                                                                                   | _    | 50   | mA   |

| I <sub>SB</sub>   | TTL Standby Current                  | $\overline{CE} = \overline{OE} = \overline{WE} = V_{IH}, V_{CC} = V_{CC} Max.$                                                                                                                                                                                                                                        | _    | 2    | mA   |

| I <sub>SB1</sub>  | CMOS Standby Current                 | $\overline{CE} = \overline{OE} = \overline{WE} = V_{CC} - 0.3V, V_{CC} = V_{CC} Max.$                                                                                                                                                                                                                                 | _    | 100  | μΑ   |

| V <sub>H</sub>    | Device ID Voltage for A <sub>9</sub> | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$                                                                                                                                                                                                                                                      | 11.5 | 12.5 | V    |

| I <sub>H</sub>    | Device ID Current for A <sub>9</sub> | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}, A9 = V_{H} Max.$                                                                                                                                                                                                                                     | _    | 50   | μΑ   |

<sup>1.</sup> Stress greater than those listed unders "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>2.</sup> No more than one output maybe shorted at a time and not exceeding one second long.

## AC Electrical Characteristics

(over all temperature ranges)

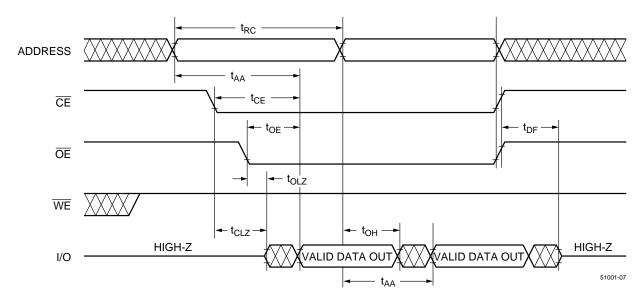

### **Read Cycle**

| Parameter        |                                                   | -4   | <b>4</b> 5 | -70  |      | -90  |      |      |

|------------------|---------------------------------------------------|------|------------|------|------|------|------|------|

| Name             | Parameter                                         | Min. | Max.       | Min. | Max. | Min. | Max. | Unit |

| t <sub>RC</sub>  | Read Cycle Time                                   | 45   | _          | 70   | _    | 90   | _    | ns   |

| t <sub>AA</sub>  | Address Access Time                               | _    | 45         | _    | 70   | _    | 90   | ns   |

| t <sub>ACS</sub> | Chip Enable Access Time                           | _    | 45         | _    | 70   | _    | 90   | ns   |

| t <sub>OE</sub>  | Output Enable Access Time                         | _    | 25         | _    | 35   | _    | 45   | ns   |

| t <sub>CLZ</sub> | CE Low to Output Active                           | 0    | _          | 0    | _    | 0    | _    | ns   |

| t <sub>OLZ</sub> | OE Low to Output Active                           | 0    | _          | 0    | _    | 0    | _    | ns   |

| t <sub>DF</sub>  | Output Enable or Chip Disable to Output in High Z | 0    | 15         | 0    | 20   | 0    | 30   | ns   |

| t <sub>OH</sub>  | Output Hold from Address Change                   | 0    | _          | 0    | _    | 0    | _    | ns   |

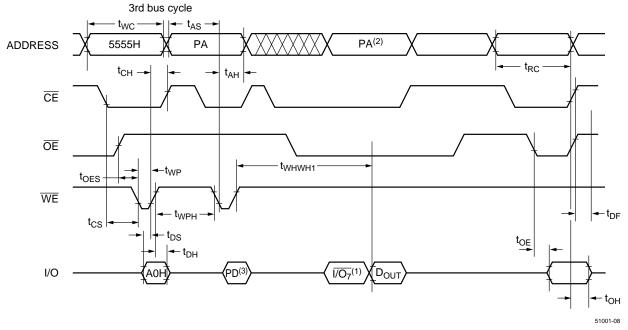

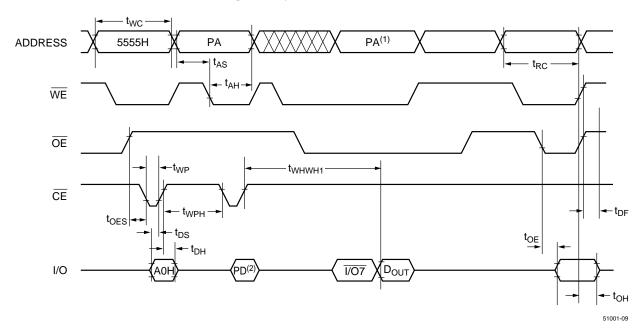

#### Program (Erase/Program) Cycle

| Parameter          |                     |      | -45  |      |      | -70  |      | -90  |      |      |      |

|--------------------|---------------------|------|------|------|------|------|------|------|------|------|------|

| Name               | Parameter           | Min. | Тур. | Max. | Min. | Тур. | Max. | Min. | Тур. | Max. | Unit |

| t <sub>WC</sub>    | Program Cycle Time  | 45   | _    | _    | 70   | _    | _    | 90   | _    | _    | ns   |

| t <sub>AS</sub>    | Address Setup Time  | 0    | _    | _    | 0    | _    | _    | 0    |      | _    | ns   |

| t <sub>AH</sub>    | Address Hold Time   | 35   | _    | _    | 45   | _    | _    | 45   | _    | _    | ns   |

| t <sub>CS</sub>    | CE Setup Time       | 0    | _    | _    | 0    | _    | _    | 0    |      | _    | ns   |

| t <sub>CH</sub>    | CE Hold Time        | 0    | _    | _    | 0    | _    | _    | 0    |      | _    | ns   |

| t <sub>OES</sub>   | OE Setup Time       | 0    | _    | _    | 0    | _    | _    | 0    |      | _    | ns   |

| t <sub>OEH</sub>   | OE High Hold Time   | 0    | _    | _    | 0    | _    | _    | 0    |      | _    | ns   |

| t <sub>WP</sub>    | WE Pulse Width      | 25   | _    | _    | 35   | _    | _    | 45   |      | _    | ns   |

| t <sub>WPH</sub>   | WE Pulse Width High | 20   | _    | _    | 35   | _    | _    | 38   |      | _    | ns   |

| t <sub>DS</sub>    | Data Setup Time     | 20   | _    | _    | 25   | _    | _    | 30   | -    | _    | ns   |

| t <sub>DH</sub>    | Data Hold Time      | 0    | _    | _    | 0    | _    | _    | 0    |      | _    | ns   |

| t <sub>WHWH1</sub> | Programming Cycle   | _    | _    | 20   | _    | _    | 20   | _    |      | 20   | μs   |

| t <sub>WHWH2</sub> | Sector Erase Cycle  | _    | _    | 10   | _    | _    | 10   | _    | _    | 10   | ms   |

| t <sub>WHWH3</sub> | Chip Erase Cycle    | _    | 500  | _    | _    | 500  | _    | _    | 500  | _    | ms   |

#### F29C51001T/F29C51001B

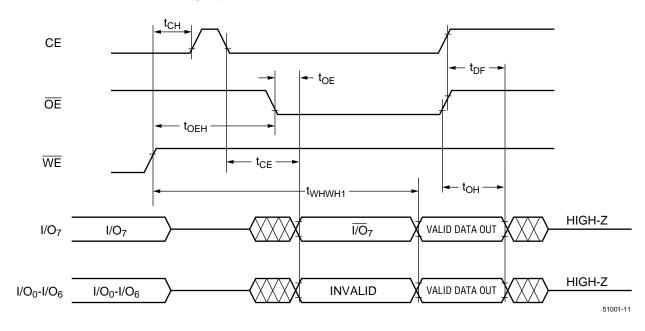

### Waveforms of Read Cycle

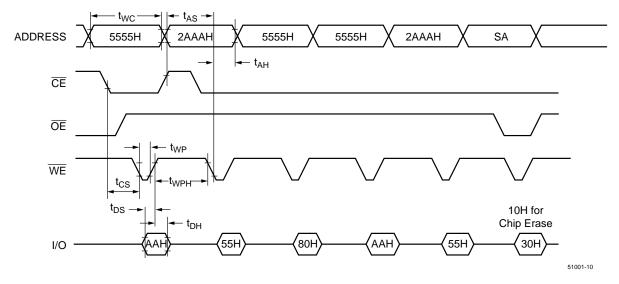

### Waveforms of WE Controlled-Program Cycle

#### NOTES:

- 1. I/O<sub>7</sub>: The output is the complement of the data written to the device.

- 2. PA: The address of the memory location to be programmed.

- 3. PD: The data at the byte address to be programmed.

## Waveforms of CE Controlled-Program Cycle

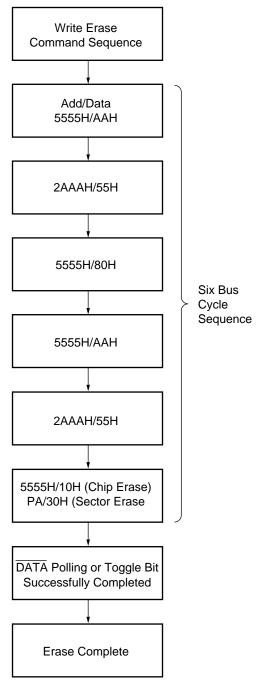

## Waveforms of Erase Cycle<sup>(1)</sup>

#### NOTES:

- 1. PA: The address of the memory location to be programmed.

- 2. PD: The data at the byte address to be programmed.

- 3. SA: The sector address for Sector Erase. Address = don't care for Chip Erase.

### F29C51001T/F29C51001B

## Waveforms of DATA Polling Cycle

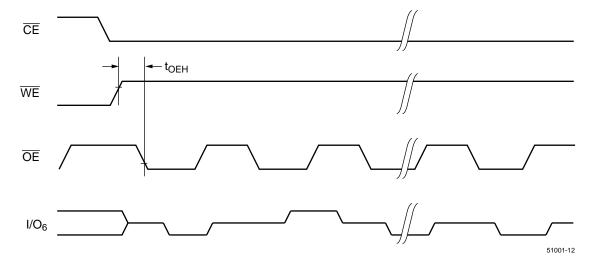

## Waveforms of Toggle Bit Cycle

#### F29C51001T/F29C51001B

#### Functional Description

The F29C51001T/F29C51001B consists of 256 equally-sized sectors of 512 bytes each. The 8 KB lockable Boot Block is intended for storage of the system BIOS boot code. The boot code is the first piece of code executed each time the system is powered on or rebooted.

The F29C51001 is available in two versions: the F29C51001T with the Boot Block address starting from 1E000H to 1FFFFH, and the F29C51001B with the Boot Block address starting from 00000H to 1FFFFH.

#### Read Cycle

A read cycle is performed by holding both CE and OE signals LOW. Data Out becomes valid only when these conditions are met. During a read cycle WE must be HIGH prior to CE and OE going LOW. WE must remain HIGH during the read operation for the read to complete (see Table 1).

#### **Output Disable**

Returning OE or CE HIGH, whichever occurs first will terminate the read operation and place the I/O pins in the HIGH-Z state.

#### Standby

The device will enter standby mode when the CE signal is HIGH. The I/O pins are placed in the HIGH-Z, independent of the OE signal.

#### Byte Program Cycle

The F29C51001T/F29C51001B is programmed on a byte-by-byte basis. The byte program operation is initiated by using a specific four-buscycle sequence: two unlock program cycles, a program setup command and program data program cycles (see Table 2).

| F29C51001T     |                  |                  | F29C51001B     |

|----------------|------------------|------------------|----------------|

| 8KB Boot Block | 1FFFFH<br>1E000H |                  | 512            |

| 512            | 1200011          |                  | 512            |

| 512            |                  |                  | •              |

|                |                  |                  | •              |

| •              |                  |                  | •              |

| •              |                  |                  | 512            |

| 512            |                  |                  | 512            |

| 512            | 00000H           | 01FFFH<br>00000H | 8KB Boot Block |

51001-13

8KB Boot Block = 16 Sectors

During the byte program cycle, addresses are latched on the falling edge of either  $\overline{CE}$  or  $\overline{WE}$ . whichever is last. Data is latched on the rising edge of CE or WE, whichever is first. The byte program cycle can be  $\overline{\text{CE}}$  controlled or  $\overline{\text{WE}}$  controlled.

#### Sector Erase Cycle

The F29C51001T/F29C51001B features a sector erase operation which allows each sector to be erased and reprogrammed without affecting data stored in other sectors. Sector erase operation is initiated by using a specific six-bus-cycle sequence: Two unlock program cycles, a setup command, two additional unlock program cycles, and the sector erase command (see Table 2). A sector must be first erased before it can be reprogrammed. While in the internal erase mode, the device ignores any program attempt into the device. The internal erase completion can be determined via DATA polling or toggle bit.

The F29C51001T/F29C51001B is shipped with pre-erased sectors (all bits = 1).

Table 1. Operation Modes Decoding

| Decoding Mode                       | CE              | ŌĒ              | WE              | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>9</sub> | I/O    |

|-------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|----------------|--------|

| Read                                | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>9</sub> | READ   |

| Byte Write                          | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>9</sub> | PD     |

| Standby                             | V <sub>IH</sub> | Х               | х               | Х               | X               | Х              | HIGH-Z |

| Autoselect Device ID                | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>H</sub> | CODE   |

| Autoselect Manufacture ID           | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>H</sub> | CODE   |

| Enabling Boot Block Protection Lock | V <sub>IL</sub> | V <sub>H</sub>  | V <sub>IL</sub> | Х               | Х               | V <sub>H</sub> | Х      |

### F29C51001T/F29C51001B

| Decoding Mode                        | CE       | ŌĒ              | WE              | A <sub>0</sub> | A <sub>1</sub> | A <sub>9</sub> | I/O    |

|--------------------------------------|----------|-----------------|-----------------|----------------|----------------|----------------|--------|

| Disabling Boot Block Protection Lock | $V_{H}$  | V <sub>H</sub>  | V <sub>IL</sub> | Х              | Х              | V <sub>H</sub> | Х      |

| Output Disable                       | $V_{IL}$ | V <sub>IH</sub> | V <sub>IH</sub> | Х              | Х              | X              | HIGH-Z |

#### NOTES:

- 1. X = Don't Care,  $V_{IH} = HIGH$ ,  $V_{IL} = LOW$ .  $V_{H} = 12.5V Max$ .

- 2. PD: The data at the byte address to be programmed.

#### Table 2. Command Codes

| Command<br>Sequence | First Bus<br>Program Cycle |      | Second Bus<br>Program Cycle |      | Third Bus<br>Program Cycle |      | Fourth Bus<br>Program Cycle |                                          | Fifth Bus<br>Program Cycle |      | Six Bus<br>Program Cycle |      |

|---------------------|----------------------------|------|-----------------------------|------|----------------------------|------|-----------------------------|------------------------------------------|----------------------------|------|--------------------------|------|

|                     | Address                    | Data | Address                     | Data | Address                    | Data | Address                     | Data                                     | Address                    | Data | Address                  | Data |

| Read                | XXXXH                      | F0H  |                             |      |                            |      |                             |                                          |                            |      |                          |      |

| Read                | 5555H                      | AAH  | 2AAAH                       | 55H  | 5555H                      | F0H  | RA                          | RD                                       |                            |      |                          |      |

| Autoselect          | 5555H                      | ААН  | 2AAAH                       | 55H  | 5555H                      | 90H  | 00H                         | 40H                                      |                            |      |                          |      |

|                     |                            |      |                             |      |                            |      | 01H                         | 01H <sup>(1)</sup><br>A1H <sup>(2)</sup> |                            |      |                          |      |

| Byte<br>Program     | 5555H                      | AAH  | 2AAAH                       | 55H  | 5555H                      | A0H  | PA                          | PD(4)                                    |                            |      |                          |      |

| Chip Erase          | 5555H                      | AAH  | 2AAAH                       | 55H  | 5555H                      | 80H  | 5555H                       | AAH                                      | 2AAAH                      | 55H  | 5555H                    | 10H  |

| Sector Erase        | 5555H                      | AAH  | 2AAAH                       | 55H  | 5555H                      | 80H  | 5555H                       | AAH                                      | 2AAAH                      | 55H  | PA(3)                    | 30H  |

#### NOTES:

- Top Boot Sector

- 2. Bottom Boot Sector

- 3. PA: The address of the memory location to be programmed.

- 4. PD: The data at the byte address to be programmed.

#### Chip Erase Cycle

The F29C51001T/F29C51001B features a chiperase operation. The chip erase operation is initiated by using a specific six-bus-cycle sequence: two unlock program cycles, a setup command, two additional unlock program cycles, and the chip erase command (see Table 2).

The chip erase operation is performed sequentially, one sector at a time. When the automated on chip erase algorithm is requested with the chip erase command sequence, the device automatically programs and verifies the entire memory array for an all zero pattern prior to erasure

The automatic erase begins on the rising edge of the last WE or CE pulse in the command sequence and terminates when the data on DQ7 is "1".

#### **Program Cycle Status Detection**

There are two methods for determining the state of the F29C51001T/F29C51001B during a program (erase/program) cycle:  $\overline{DATA}$  Polling (I/O<sub>7</sub>) and Toggle Bit (I/O<sub>6</sub>).

### DATA Polling (I/O<sub>7</sub>)

The F29C51001T/F29C51001B features DATA polling to indicate the end of a program cycle. When the device is in the program cycle, any attempt to read the device will received the complement of the loaded data on I/O<sub>7</sub>. Once the program cycle is completed, I/O<sub>7</sub> will show true data, and the device is then ready for the next cycle.

#### Toggle Bit (I/O<sub>6</sub>)

The F29C51001T/F29C51001B also features another method for determining the end of a program cycle. When the device is in the program cycle, any attempt to read the device will result in  $I/O_6$  toggling between 1 and 0. Once the program is completed, the toggling will stop. The device is then ready for the next operation. Examining the toggle bit may begin at any time during a program cycle.

#### F29C51001T/F29C51001B

#### **Boot Block Protection**

The F29C51001T/F29C51001B features hardware Boot Block Protection. The boot block sector protection is enabled when high voltage (12.5V) is applied to  $\overline{OE}$  and A9 pins with  $\overline{CE}$  pin LOW and  $\overline{WE}$  pin IOW. The sector protection is desabled when high voltage is applied to  $\overline{OE}$ ,  $\overline{CE}$  and A9 pins with  $\overline{WE}$  pin LOW. Other pins can be HIGH or LOW. This is shown in table 1.

#### Autoselect

The F29C51001T/F29C51001B features an Autoselect mode to identify the Boot Block (protected/unprotected), the Device (Top/Bottom), and the manufacturer ID.

To get to the Autoselect mode, a high voltage  $(V_H)$  must be applied to the  $A_9$  pin. Once the  $A_9$  signal is returned to LOW or HIGH, the device will return to the previous mode.

#### **Boot Block Protection Status**

In Autoselect mode, performing a read at address 3CXX2H or address 0CXX2H will indicate if the Top Boot Block sector or the Bottom Boot Block sector is locked out. If the data is 01H, the Top/Bottom Boot Block is protected. If the data is 00H, the Top/Bottom Boot Block is unprotected. (see Table 3.)

#### Device ID

In Autoselect mode, performing a read at address XXXXH will determine whether the device is a Top Boot Block device or a Bottom Boot Block device. If the data is 01H, the device is a Top Boot Block. If the data is A1H, the device is a Bottom Boot Block device (see Table 3).

In addition, the device ID can also be read via the command register when the device is erased or programmed in a system without applying high voltage to the  $A_9$  pin. When  $A_0$  is HIGH, the device ID is presented at the outputs.

#### Manufacturer ID

In Autoselect mode, performing a read at address. XXXX0H will determine the manufacturer ID. 40H is the manufacturer code for SyncMOS Flash.

In addition the manufacturer ID can also be read via the command register when the device is erased or programmed in a system without applying high voltage to the  $A_9$  pin. when  $A_0$  is LOW, the manufacturer ID is presented at the outputs.

#### Hardware Data Protection

$V_{CC}$  Sense Protection: the program operation is inhibited when VCC is less than 2.5V.

*Noise Protection:* a CE or WE pulse of less than 5ns will not initiate a program cycle.

*Program Inhibit Protection:* holding any one of OE LOW, CE HIGH or WE HIGH inhibits a program cycle.

Table 3. Autoselect Decoding

|                       |            |                 | Add             |                                 |                                  |                                         |

|-----------------------|------------|-----------------|-----------------|---------------------------------|----------------------------------|-----------------------------------------|

| Decoding Mode         | Boot Block | A <sub>0</sub>  | A <sub>1</sub>  | A <sub>2</sub> -A <sub>13</sub> | A <sub>14</sub> -A <sub>16</sub> | Data I/O <sub>0</sub> -I/O <sub>7</sub> |

| Boot Block Protection | Тор        | V <sub>IL</sub> | V <sub>IH</sub> | Х                               | V <sub>IH</sub>                  | 01H: protected                          |

|                       | Bottom     | V <sub>IL</sub> | V <sub>IH</sub> | Х                               | V <sub>IL</sub>                  | 00H: unprotected                        |

| Device ID             | Тор        | V <sub>IH</sub> | V <sub>IL</sub> | Х                               | Х                                | 01H                                     |

|                       | Bottom     |                 |                 |                                 |                                  | A1H                                     |

| Manufacture ID        |            | V <sub>IL</sub> | V <sub>IL</sub> | Х                               | Х                                | 40H                                     |

#### NOTE:

<sup>1.</sup>  $X = Don't Care, V_{IH} = HIGH, V_{IL} = LOW.$

#### F29C51001T/F29C51001B

#### Byte Program Algorithm

# Write Program Command Sequence Add/Data 5555H/AAH 2AAAH/55H Four Bus Cycle Sequence 5555H/A0H PA/PD DATA Polling (I/O7) or Toggle Bit (I/O6) No Verify Byte? Yes Programming Completed

## Chip/Sector Erase Algorithm

51001-14

### F29C51001T/F29C51001B

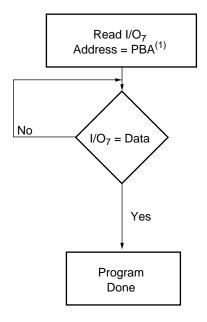

## DATA Polling Algorithm

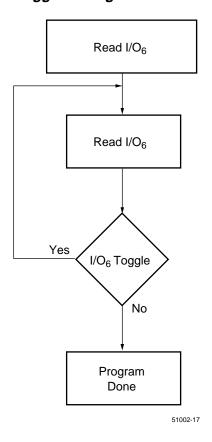

## Toggle Bit Algorithm

#### NOTE:

1. PBA: The byte address to be programmed.

#### F29C51001T/F29C51001B

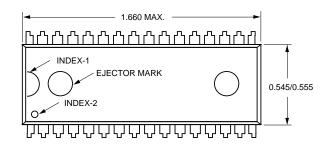

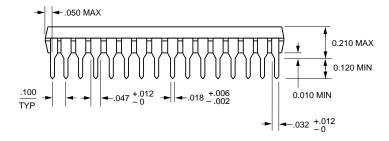

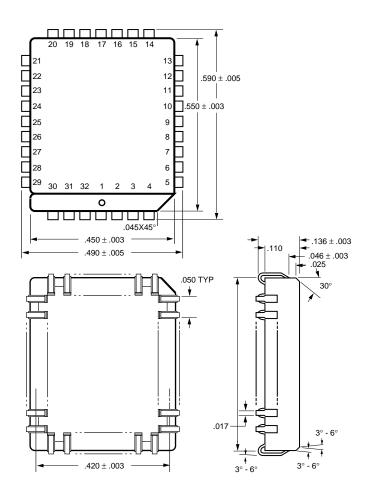

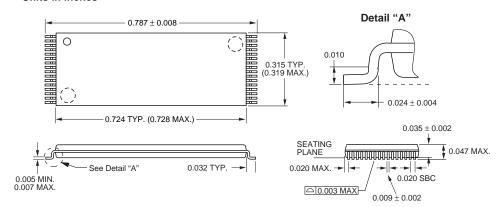

## Package Diagrams

#### 32-pin Plastic DIP

#### 32-pin PLCC

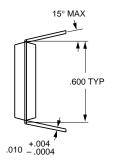

### 32-pin TSOP-I

#### Units in inches

## SyncMOS Technology Inc.

## **Sales Office:**

No. 1, Creation Rd. 1,

Science-Based Industrial Park,

Hsinchu, Taiwan, R.O.C.

Tel: 886-3-5792926

Fax: 886-3-5792953

Note 1: publication date: May 1999. Rev. A

Note 2: all data and specification are subject to change without notice.