. INC.

# PEEL<sup>™</sup>20CG10A-15/PEEL<sup>™</sup> 20CG10AL-15 CMOS Programmable Electrically Erasable Logic Device

#### **Features**

#### ■ Advanced CMOS EEPROM Technology

#### ■ High Performance

- tpD = 15ns

- fmax = 66.7MHz

#### **■** Low Power Consumption

- 115mA at 25MHz

- 75mA at 25MHz (L)

#### **■** EE Reprogrammability

- Low risk reprogrammable inventory

- Superior programming and functional yield

- Erases and programs in seconds

### ■ Development and Programming Support

- Third-party software and programmers

- ICT PEEL Development System with APEEL™ Logic Assembler

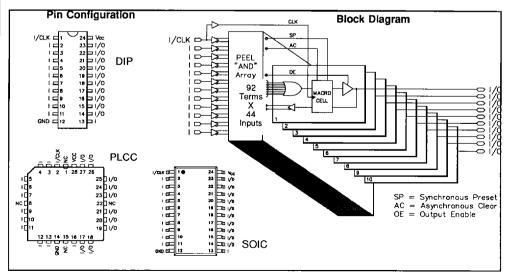

#### ■ Architectural Flexibility

- 92 product term X 44 input AND array

- Up to 22 inputs and 10 outputs

- Independently programmable 12-configuration I/O macrocells

- Synchronous preset, asynchronous clear

- Independently programmable output enables

#### ■ Application Versatility

- Replaces random SSI/MSI logic

- Emulates 24-pin bipolar PAL devices

- Convert 24-pin PAL and EPLD designs with ICT software

- Superset compatible with the CMOS PALC20G10

### **General Description**

The ICT PEEL20CG10A-15 are CMOS Programmable Electrically Erasable Logic Devices that provide a high-performance, low-power, reprogrammable, and architecturally enhanced alternative to conventional programmable logic devices (PLDs). Designed in advanced CMOS EEPROM technology, the PEEL20CG10A rivals speed parameters of comparable bipolar PLDs while dramatically improving power consumption. EE reprogrammability allows for cost effective plastic packaging, low risk inventory, reduced development and retrofit costs, and enhanced testability to ensure 100% field programmability and function.

The PEEL20CG10A's flexible architecture and ICT's JEDEC file translator allows the PEEL20CG10A to replace bipolar 24-pin PAL devices without the need to rework the existing design. Applications for the PEEL20CG10A include: replacement of random SSI/MSI logic circuitry; emulation of 24-pin bipolar PAL devices; and user customized sequential and combinatorial functions such as counters, shift registers, state machines, address decoders, multiplexers, etc. Development and programming support for the PEEL20CG10A is provided by ICT and third-party manufacturers.

NC

## PEEL<sup>™</sup>20CG10A/AL-15

## **Absolute Maximum Ratings**

Exposure to absolute maximum ratings over extended periods of time may affect device reliability. Exceeding absolute maximum ratings may cause permanent damage

| Symbol | Parameter                               | Conditions                   | Rating             | Unit |  |

|--------|-----------------------------------------|------------------------------|--------------------|------|--|

| Vcc    | Supply Voltage                          | Relative to GND              | - 0.5 to + 7.0     | V    |  |

| Vı, Vo | Voltage Applied to Any Pin <sup>6</sup> | Relative to GND <sup>1</sup> | - 0.5 to Vcc + 0.6 | ٧    |  |

| lo     | Output Current                          | Per pin (IoL, Ioн)           | ± 25               | mA   |  |

| TST    | Storage Temperature                     |                              | - 65 to+150        | .c   |  |

| TLT    | Lead Temperature                        | Soldering 10 seconds         | + 300              | .c   |  |

# Operating Ranges<sup>2</sup>

| Symbol | Parameter           | Conditions | Min  | Max  | Unit |

|--------|---------------------|------------|------|------|------|

| Vcc    | Supply Voltage      | Commercial | 4.75 | 5.25 | V    |

|        |                     | Industrial | 4.5  | 5.5  | V    |

| TA     | Ambient Temperature | Commercial | 0    | + 70 | .c   |

|        |                     | Industrial | - 40 | + 85 | .c   |

| TR     | Clock Rise Time     | See note 4 |      | 250  | ns   |

| TF     | Clock Fall Time     | See note 4 |      | 250  | ns   |

| TRVCC  | Vcc Rise Time       | See note 4 |      | 250  | ms   |

## D.C. Electrical Characteristics Over the operating range

| Symbol                       | Parameter                                             | Conditions                                                        | Min       | Max       | Unit |

|------------------------------|-------------------------------------------------------|-------------------------------------------------------------------|-----------|-----------|------|

| Vон                          | Output HIGH Voltage - TTL                             | Vcc = Min, IoH = - 4.0mA                                          | 2.4       |           | ٧    |

| Vонс                         | Output HIGH Voltage-CMOS                              | Vcc = Min, loн = -10μA                                            | Vcc - 0.1 |           | ٧    |

| VoL                          | Output LOW Voltage - TTL                              | Vcc = Min, loL = 16mA                                             |           | 0.5       | ٧    |

| Volc                         | Output LOW Voltage-CMOS                               | Vcc = Min, IoL = 10μA                                             |           | 0.1       | ٧    |

| ViH                          | Input HIGH Level                                      |                                                                   | 2.0       | Vcc + 0.3 | ٧    |

| VIL                          | Input LOW Level                                       |                                                                   | - 0.3     | 0.8       | ٧    |

| lıL                          | Input Leakage Current                                 | Vcc = Max, GND ≤ Vin ≤ Vcc                                        |           | ±10       | μΑ   |

| loz                          | Output Leakage Current                                | I/O = High-Z, GND ≤ Vo≤ Vcc                                       |           | ±10       | μΑ   |

| Isc                          | Output Short Circuit Current                          | V <sub>CC</sub> =5V, V <sub>O</sub> =0.5V <sup>10</sup> , TA=25°C | - 30      | -135      | mΑ   |

| lcc                          | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | I '                                                               |           | 115       | mA   |

|                              |                                                       | L                                                                 | 75        |           |      |

| C <sub>IN</sub> <sup>8</sup> | Input Capacitance                                     | T <sub>A</sub> = 25°C, V <sub>CC</sub> = 5.0V<br>@ f = 1MHz       |           | 6         | pF   |

| Cout 8                       | Output Capacitance                                    |                                                                   |           | 12        | pF   |

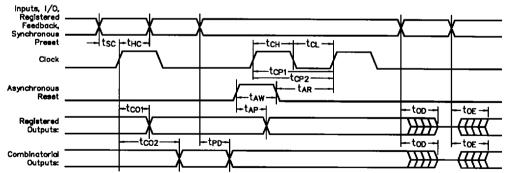

### A.C. Electrical Characteristics Over the Operating Range 9,12

| Symbol            | Parameter                                                                       | 20CG10A-15 |     | Unit |

|-------------------|---------------------------------------------------------------------------------|------------|-----|------|

|                   |                                                                                 | Min        | Max | 1    |

| tpD               | Input <sup>6</sup> or feedback to non-registered output                         | _          | 15  | ns   |

| toE               | Input <sup>6</sup> to output enable <sup>7</sup>                                |            | 15  | ns   |

| top               | Input <sup>6</sup> to output disable <sup>7</sup>                               |            | 15  | ns   |

| tco1              | Clock to output                                                                 |            | 10  | ns   |

| tco2              | Clock to combinatorial output delay via internal registered feedback            |            | 19  | ns   |

| tcF               | Clock to feedback                                                               |            | 6   | ns   |

| tsc               | Input <sup>6</sup> or feedback setup to clock                                   | 10         |     | ns   |

| thc               | Input <sup>6</sup> hold after clock                                             | 0          |     | ns   |

| tcL,tcH           | Clock width - clock low time, clock high time <sup>4</sup>                      | 8          |     | ns   |

| tcP1              | Minimum clock period (register feedback to registered output via internal path) | 20         |     | ns   |

| f <sub>max1</sub> | Max clock freq. Internal Feedback <sup>13</sup>                                 | 66.7       |     | MHz  |

| f <sub>max2</sub> | Max clock freq. (1/tcp1)                                                        | 50         |     | MHz  |

| f <sub>max3</sub> | Max clock freq no (1/tCL + tCH) <sup>13</sup>                                   | 62.5       | ••  | MHz  |

| taw               | Asynchronous Reset pulse width                                                  | 15         |     | ns   |

| tap               | Input <sup>6</sup> to Asynchronous Reset                                        |            | 15  | ns   |

| tar               | Asynchronous Reset recovery time                                                |            | 15  | ns   |

| tRESET            | Power-on reset time for registers in clear state <sup>4</sup>                   |            | 5   | μs   |

## **Switching Waveforms**

- 1. Minimum DC input is 0.5V, however inputs may undershoot to - 2.0V for periods less than 20nS.

- 2.Contact ICT for other operating ranges.

- 3. V<sub>I</sub> and V<sub>O</sub> are not specified for program/verify operation.

- 4. Test points for Clock and Vcc in tR, tr, tcL, tcH, and tRESET are referenced at 10% and 90% levels.

- 5.I/O pins are 0V or 3V.

- 6. "Input" refers to an Input pin signal.

- 7. to E is measured from input transition to  $V_{REF} \pm 0.1V$ , top is measured from input transition to  $V_{OH} = 0.1 V$  or  $V_{OL} + 0.1 V$ ;  $V_{REFF} = V_L$  see test loads at the end of this section.

- 8. Capacitances are tested on a sample basis.

- 9. Test conditions assume: signal transition times of 5ns or less from the 10% and 90% points, timing reference levels of 1.5V (unless otherwise specified).

- 10. Test one output at a time for a duration of less than 1 sec. 11.ICC for a typical application: This parameter is tested with

- the device programmed as a 10-bit Counter.

- 12.PEEL Device test loads are specified at the end of this

- 13.Parameters are not 100% tested. Specifications are based on initial characterization and are tested after any design or process modification which may affect operational frequency.