# **Application Hint 27**

**Slowing Voltage Regulator Turn-On**

by Jerry Kmetz

### **Slow Turn-On Circuits**

The turn-on time interval of a voltage regulator is essentially determined by the bandwidth of the regulator, its maximum output current, and the load capacitance. To some extent the rise time of the applied input voltage (which is normally quite short, tens of milliseconds, or less) also affects the turn-on time. However, the regulator output voltage typically steps abruptly at turn-on. Increasing the turn-on interval via some form of slew-limiting decreases the surge current seen by both the regulator and the system. This application hint addresses designing circuitry to change the step-function to a smoother RC charge waveform.

Various performance features exist between the three circuits that are presented. These are (1) whether stability is impacted, (2) whether start-up output is 0V, and (3) whether the circuit quickly recovers from momentarily interrupted input voltage or shorted output. The following table summarizes the features of each circuit:

| Circuit<br>Number | Stability<br>Impacted? |      | V <sub>IN</sub> Interrupt<br>Recovery? | V <sub>OUT</sub> Short<br>Recovery? |

|-------------------|------------------------|------|----------------------------------------|-------------------------------------|

| 1                 | yes                    | 1.2V | no                                     | no                                  |

| 2                 | no                     | 1.8V | no                                     | yes                                 |

| 3                 | no                     | 0V   | yes                                    | no                                  |

**Slow Turn-On Circuit Performance Features**

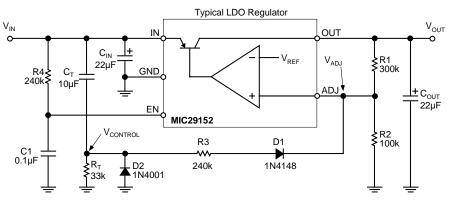

#### 1. The Simplest Approach

Figure 1 illustrates a typical LDO voltage regulator, the MIC29153, with an additional capacitor ( $C_T$ ) in parallel with the series leg (R1) of the feedback voltage divider. Since the voltage ( $V_{ADJ}$ ) will be maintained at  $V_{REF}$  by the regulator loop, the output of this circuit will still rapidly step to  $V_{REF}$  and then rise slowly. Since  $V_{REF}$  is usually only about 1.2V, this eliminates a large part of the surge current.

As  $C_T$  charges, the regulator output (V<sub>OUT</sub>) asymptotically approaches the desired value. If a turn-on time of 300 milliseconds is desired then about three time constants should be allowed for charge time:

then  $3\tau = 0.3s$ , or

$\tau = 0.1s = R1 \times C_T = 300k\Omega \times 0.33\mu F.$

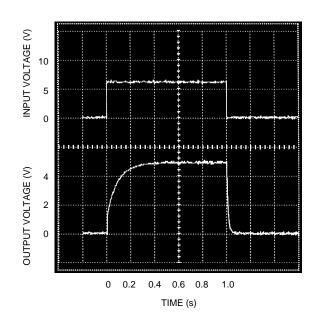

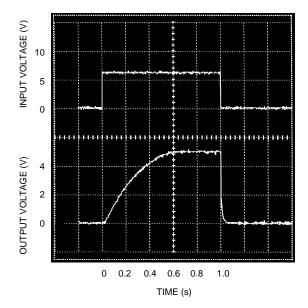

Figure 2 shows the waveforms of the circuit of Figure 1. This circuit has three shortcomings: (1) the approximately 1.2V step at turn-on, (2) the addition of capacitor  $C_T$  places a zero in the closed-loop transfer function (which affects frequency and transient responses and can potentially cause stability problems) and (3) the recovery time associated with a momentarily short-circuited output may be unacceptably long. This is because if the output is shorted  $C_T$  is discharged only by R2; if the short is removed before  $C_T$  is fully discharged the regulator output will not exhibit the desired turn-on behavior.

Figure 2. Turn-On Behavior for Circuit of Figure 1

Figure 1. Simplest Slow Turn-On Circuit

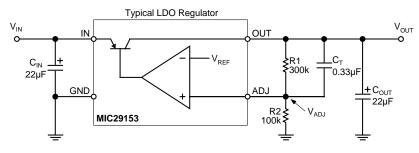

Figure 3. Improved Slow Turn-On Circuit

#### 2. Improved Simple Approach

Figure 3 is an improvement on the circuit of Figure 1 in that it addresses the problems of potential instability and recovery time. Diode D1 is added to the circuit to decouple the (charged) capacitor from the feedback network, thereby eliminating the effect of  $C_T$  on the closed-loop transfer function. Because of the non-linear effect of D1 being in series with  $C_T$ , there is a slightly longer "tail" associated with approaching the final output voltage at turn-on. In the event of a momentarily shorted output, diode D2 provides a low-impedance discharge path for  $C_T$  and thus assures the desired turn-on behavior upon recovery.

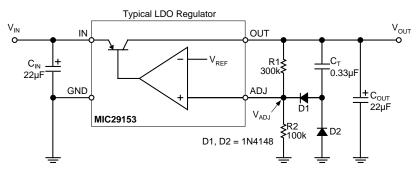

Figure 4 shows the waveforms of the circuit of Figure 3. Note that the initial step-function output is now 0.6V higher than with the circuit of Figure 1. This approximately 1.8V turn-on pedestal may be objectionable, especially in applications where the output voltage is relatively low by design.

Figure 4. Turn-On Behavior of Figure 3

## 3. Eliminating Initial Start-Up Pedestal

The circuits of Figures 1 and 3 depend upon the existence of an output voltage (to create V<sub>ADJ</sub>) and, therefore, produce the initial step-function voltage pedestals of about 1.2V and 1.8V, as can be seen in Figures 2 and 4, respectively. The approach of Figure 5 facilitates placing the output voltage origin at zero volts because V<sub>CONTROL</sub> is derived from the input voltage. No reactive component is added to the feedback circuit. The value of  $R_T$  should be considerably smaller than R3 to assure that the junction of  $R_T$  and  $C_T$  acts like a voltage source driving R3 and so  $R_T$  is the primary timing control. If sufficient current is introduced into the loop summing junction (via R3) to generate  $V_{AD,I} \ge V_{RFF}$ , then  $V_{OUT}$  will be zero volts. As  $R_T$ charges C<sub>T</sub> the voltage V<sub>CONTROL</sub> decays, which would eventually result in V<sub>ADJ</sub> < V<sub>REF</sub>. However, since in normal operation  $V_{ADJ} = V_{REF}$ ,  $V_{OUT}$  will become greater than zero volts. The process continues until V<sub>CONTROL</sub> decays to V<sub>RFF</sub>+0.6V and V<sub>OUT</sub> reaches the desired value. This circuit requires a regulator with an enable function, (e.g., the MIC29152) because a small (< 2V) spike is generated coincident with application of a step-function input voltage. Capacitor C1 and resistor R4 provide a short hold-off timing function that eliminates this spike.

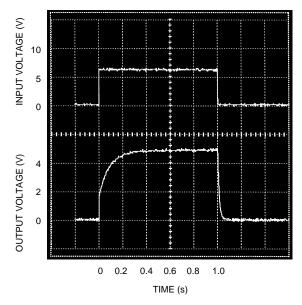

Figure 6 illustrates the timing of this operation. The small initial delay (about 40 milliseconds) is the time interval during which  $V_{AD,I} > V_{REF}$ . Since  $V_{IN}$  is usually fairly consistent in value R3 may be chosen to minimize this delay. Note that if R3 is calculated based on the minimum foreseen  $V_{IN}$  (as described below), then higher values of V<sub>IN</sub> will produce additional delay before the turn-on ramp begins. Conversely, if V<sub>IN (max)</sub> is used for the calculation of R3, then lower values of V<sub>IN</sub> will not produce the desired turn-on characteristic; instead, there will be a small initial step-function prior to the desired turn-on ramp. Recovery from a momentarily shorted output is not addressed by this circuit, but interrupted input voltage is handled properly. Notice that the build-up of regulator output voltage differs from the waveforms of Figures 2 and 4 in that it is more ramp-like. This is because only an initial portion of the RC charge waveform is used; i.e., while  $V_{CONTROL} > V_{RFF}$ +0.6V. The actual time constant used for Figure 5 is 0.33 second, so  $3\tau$  is one second. As shown by Figure 6, this provides about 600 milliseconds of ramp time,

Figure 5. Slow Turn-On Without Pedestal Voltage

Figure 6. Turn-On Behavior of Figure 5

which corresponds to the first 60% of the capacitor RC charge curve. R3 is calculated as follows:

at turn-on time force

$$V_{\mbox{ADJ}}$$

= 1.5V (just slightly higher than  $V_{\mbox{REF}})$  then

$$I_{\text{CONTROL}} = \frac{1.5V}{\left(\frac{\text{R1} \times \text{R2}}{\text{R1} + \text{R2}}\right)}$$

and

$$R3 = \frac{V_{IN min} - 0.6V}{I_{CONTROL}}$$

Since the MIC29152 is a low-dropout regulator, 6V was chosen for  $V_{IN}$ (min). This corresponds to the small (approximately 40 msec) delay before the output begins to rise. With 7V input the initial delay is considerably more noticeable.