# CMX605 Digital Line to POTS Interface

D/605/6 July 2001 Provisional Issue

### **Features**

- Pre-Programmed Tone Generators

- Fully Integrated DTMF Decoder/Encoder

- SPM Generator

- Simple Serial Control Interface

- 3.58MHz Xtal/Clock

- V23/Bell 202 FSK Generator

- Digital Ringing Voltage Generator

# **Applications**

- Digital Line to POTS Interface

- Subscriber Terminal Adapters

- Wireless Local Loop

- Computer Telephony Integration

- Telephone/Radio Patch Systems

- Pair Gain Systems

- Billing/SPM Systems

# 1.1 Brief Description

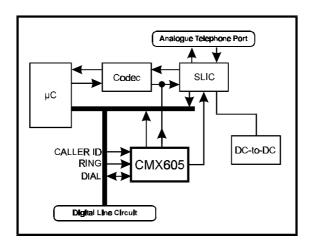

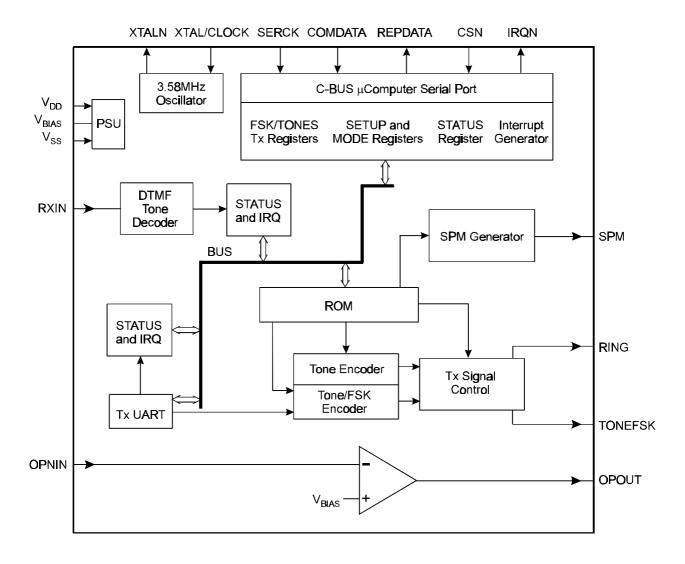

The CMX605 is an integrated telecom tone generator and DTMF encoder/decoder designed for ISDN interfaces, Wireless Local Loop and Analogue to Digital Phone Conversion systems. The tone generator covers an extensive range of pre-programmed tones used in analogue phone systems (POTS). Three outputs are provided: 'Ringing signals', 'In-band tones or FSK data', and '12kHz/16kHz Metering pulses'. Simple software control facilitates the interface to a wide range of commonly used  $\mu$ Cs and SLICs, enabling a comprehensive analogue telephone line presentation.

The DTMF encoder/decoder presents the digital line interface with DTMF dialling information received from the telephone user and generates the appropriate DTMF tones for the POTS interface. DTMF tone pairs can be encoded along with each tone singly or with other dual tone signals, such as those used in CIDCW systems and 'On Hook' signalling systems.

Other tone standards supported are: Fax and Modem 'answer' and 'originate', ITU (CCITT) 'R1' and 'R2' signals, and sufficient tones for simple melody generation. Communication to and from the host  $\mu$ Controller is performed by a 'C-BUS' serial interface, which is compatible with the 'SPI' interface.

# **CONTENTS**

| Section |       | <u>Page</u>                        | <u>3</u> |

|---------|-------|------------------------------------|----------|

| 1.1     | Brief | Description1                       |          |

| 1.2     | Block | c Diagram3                         |          |

| 1.3     | Signa | al List4                           |          |

| 1.4     | Exter | nal Components6                    |          |

| 1.5     | Gene  | ral Description7                   |          |

|         | 1.5.1 | Xtal Osc and Clock Dividers7       |          |

|         | 1.5.2 | Uncommitted Amplifier7             |          |

|         | 1.5.3 | Tone/FSK Encoder and Tone Encoder7 |          |

|         | 1.5.4 | SPM Generator10                    |          |

|         | 1.5.5 | Transmit Operator10                |          |

|         | 1.5.6 | Tx UART                            |          |

|         | 1.5.7 | DTMF Tone Decoder12                |          |

|         | 1.5.8 | 'C-BUS' Interface                  |          |

|         | 1.5.9 | 'C-BUS' Registers14                |          |

| 1.6     | Appli | cation Notes15                     |          |

|         | 1.6.1 | Telecom Tones                      |          |

|         | 1.6.2 | C-BUS Timing19                     |          |

| 1.7     | Perfo | rmance Specification22             |          |

|         | 1.7.1 | Electrical Performance22           |          |

|         | 1.7.2 | Packaging26                        |          |

Digital Line to POTS Interface CMX605

# 1.2 Block Diagram

Figure 1 Block Diagram

# 1.3 Signal List

| CMX605<br>D4/P3 | Signal     |       | Description                                                                                                                                                                                             |

|-----------------|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.         | Name       | Туре  |                                                                                                                                                                                                         |

| 1               | XTALN      | O/P   | The output of the on-chip Xtal oscillator inverter.                                                                                                                                                     |

| 2               | XTAL/CLOCK | I/P   | The input to the oscillator inverter from the Xtal circuit or external clock source.                                                                                                                    |

| 3               | SERCK      | I/P   | The 'C-BUS' serial clock input from the host μC. See section 1.5.8                                                                                                                                      |

| 4               | COMDATA    | I/P   | The 'C-BUS' serial data input from the host $\mu C$ .                                                                                                                                                   |

| 5               | REPDATA    | T/S   | A 3-state 'C-BUS' serial data output to the host $\mu$ C. This output is high impedance when not sending data to the host $\mu$ C.                                                                      |

| 6               | CSN        | I/P   | The 'C-BUS' transfer control input provided by the host μC.                                                                                                                                             |

| 7               | IRQN       | O/P   | A 'wire-ORable' output for connection to a host μC Interrupt Request input. This output is pulled down to VSS when active and is high impedance when inactive. An external pullup resistor is required. |

| 8               | $V_{SS}$   | Power | The negative supply rail (ground).                                                                                                                                                                      |

| 9               | TONEFSK    | O/P   | The sinewave output of the Tones and FSK signal generators.                                                                                                                                             |

| 10              | SPM        | O/P   | The sinewave output of the SPM signal generator.                                                                                                                                                        |

| CMX605<br>D4/P3 | Signal          |       | Description                                                                                                                                                                                                             |

|-----------------|-----------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.         | Name            | Туре  |                                                                                                                                                                                                                         |

| 11              | $V_{BIAS}$      | O/P   | An internally generated bias voltage of $V_{DD}/2$ , except when the device has been reset, $V_{BIAS}$ will discharge to $V_{SS}$ . It should be decoupled to $V_{SS}$ by a capacitor mounted close to the device pins. |

| 12              | RXIN            | I/P   | The input to the DTMF decoder, internally biased at V <sub>DD</sub> /2. It should be ac coupled.                                                                                                                        |

| 13              | OPNIN           | I/P   | The inverting input to the uncommitted amplifier.                                                                                                                                                                       |

| 14              | OPOUT           | O/P   | The output of the uncommitted amplifier.                                                                                                                                                                                |

| 15              | RING            | O/P   | The squarewave output of the Ringing Signal generator.                                                                                                                                                                  |

| 16              | V <sub>DD</sub> | Power | The positive supply rail. Levels and thresholds within the device are proportional to this voltage. It should be decoupled to V <sub>SS</sub> by a capacitor mounted close to the device pins.                          |

# Notes:

I/P = Input O/P = Output T/S = 3-state Output

This device is capable of detecting and decoding small amplitude signals. To achieve this  $V_{DD}$  and  $V_{BIAS}$  decoupling and protecting the receive path from extraneous in-band signals are very important. It is recommended that the printed circuit board is laid out with a ground plane in the CMX605 area to provide a low impedance connection between the  $V_{SS}$  pin and the  $V_{DD}$  and  $V_{BIAS}$  decoupling capacitors.

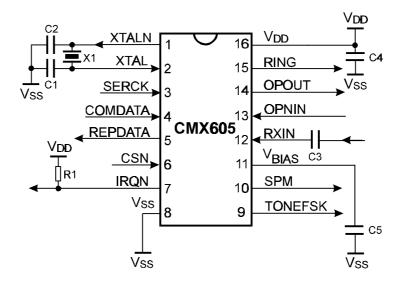

# 1.4 External Components

**Figure 2 Recommended External Components**

| R1 | 100k $\Omega$ | C1, C2 | 18pF  |

|----|---------------|--------|-------|

| X1 | 3.579545 MHz  | C3     | 0.1µF |

|    |               | C4, C5 | 1.0µF |

Resistors ±5%, capacitors ±10% unless otherwise stated.

# 1.5 General Description

The CMX605 is a telecom tone generator and DTMF tone encoder/decoder. It has separate output ports for the three different classes of signals encoded. These include Ringing signal, In-band tones or FSK data at 1200bps and High frequency metering pulses (SPM tones). It has a transmit level attenuator for In-band tones or FSK data and an envelope control for SPM tones. It also has an uncommitted amplifier and uses the industry standard 3.58MHz Xtal for its oscillator. These functions are controlled over a 'C-BUS' serial µC interface, which also carries the transmit FSK data and the DTMF decoded data.

The CMX605 should initially be reset by issuing a 'C-BUS' RESET command. Individual functions may be disabled or enabled by the use of bits 5, 6 and 7 in the SETUP Register. See Section 1.5.9. Approximately 50ms should be allowed for the Tx dc level to settle at V<sub>BIAS</sub> before enabling the Tx functions (set bit 6 of the MODE Register to '1') after the CMX605 has been reset.

### 1.5.1 Xtal Osc and Clock Dividers

Frequency and timing accuracy of the CMX605 is determined by a 3.579545MHz clock present at the XTAL/CLOCK pin. This may be generated by the on-chip oscillator inverter using the external components C1, C2 and X1 of Figure 2, or may be supplied from an external source to the XTAL/CLOCK input. If the clock is supplied from an external source, C1, C2 and X1 should not be fitted.

If the clock is provided by an external source which is not always running, then the CMX605 should be reset when the clock is not available. Resetting the CMX605 will also turn off the on-chip oscillator. Failure to reset the device may cause a rise in the supply current drawn by the CMX605.

### 1.5.2 Uncommitted Amplifier

This amplifier, with suitable external components, can be used either for adjusting the received signal to the correct amplitude for the DTMF decoder or for adjusting the transmit signal level (for the line hybrid).

### 1.5.3 Tone/FSK Encoder and Tone Encoder

When bit 5 of the MODE Register is set to '1' then these blocks generate FSK signals as determined by bit 0 of the SETUP Register and the Tx data bits from the UART block, as shown in the table below:

| SETUP Register | Tone/FSK Generator   | FSK Signal Frequency | FSK Signal Frequency |

|----------------|----------------------|----------------------|----------------------|

| Bit 0          |                      | '0' (Space)          | '1' (Mark)           |

| 0              | V23 1200bps FSK      | 2100Hz               | 1300Hz               |

| 1              | Bell 202 1200bps FSK | 2200Hz               | 1200Hz               |

When bit 5 of the MODE Register is set to '0', these blocks generate single or dual tones from the range shown in the tables on the following pages. Bit 6 of the MODE Register is then used to enable or disable the block's output to the Tx Signal Control, RING and TONEFSK outputs. There are four tone fields addressed by bits 0 and 1 of the MODE Register.

Tone Field 0, MODE Register bit 1 and bit 0 = '0' and '0' respectively.

| TX TO | TX TONES Register Bits 4-7 |    | Frequency | TX TO   | TX TONES Register Bits |    |    | Frequency |         |

|-------|----------------------------|----|-----------|---------|------------------------|----|----|-----------|---------|

| D7    | D6                         | D5 | D4        | (Hz)    | D3                     | D2 | D1 | D0        | (Hz)    |

| 0     | 0                          | 0  | 0         | 0 = OFF | 0                      | 0  | 0  | 0         | 0 = OFF |

| 0     | 0                          | 0  | 1         | 252.4   | 0                      | 0  | 0  | 1         | * 17.1  |

| 0     | 0                          | 1  | 0         | 268.7   | 0                      | 0  | 1  | 0         | * 20.5  |

| 0     | 0                          | 1  | 1         | 285.3   | 0                      | 0  | 1  | 1         | * 24.9  |

| 0     | 1                          | 0  | 0         | 315.5   | 0                      | 1  | 0  | 0         | * 34.1  |

| 0     | 1                          | 0  | 1         | 330.5   | 0                      | 1  | 0  | 1         | * 41.0  |

| 0     | 1                          | 1  | 0         | 375.2   | 0                      | 1  | 1  | 0         | * 51.2  |

| 0     | 1                          | 1  | 1         | 404.3   | 0                      | 1  | 1  | 1         | -       |

| 1     | 0                          | 0  | 0         | 468.0   | 1                      | 0  | 0  | 0         | 262.9   |

| 1     | 0                          | 0  | 1         | 495.8   | 1                      | 0  | 0  | 1         | 293.6   |

| 1     | 0                          | 1  | 0         | 520.6   | 1                      | 0  | 1  | 0         | 348.2   |

| 1     | 0                          | 1  | 1         | 548.0   | 1                      | 0  | 1  | 1         | 392.6   |

| 1     | 1                          | 0  | 0         | 562.8   | 1                      | 1  | 0  | 0         | 1600    |

| 1     | 1                          | 0  | 1         | 578.4   | 1                      | 1  | 0  | 1         | 1633    |

| 1     | 1                          | 1  | 0         | 595.0   | 1                      | 1  | 1  | 0         | 1827    |

| 1     | 1                          | 1  | 1         | 612.5   | 1                      | 1  | 1  | 1         | 587.2   |

NOTE: \* These outputs are routed to the RING digital output instead of the TONEFSK output. Any single tone output level at TONEFSK output is 0dBm.

Tone Field 1, MODE Register bit 1 and bit 0 = '0' and '1' respectively

| TX TOI | TX TONES Register Bits 4-7 |    | Frequency | TX      | TONES R | egister Bit | s 0-3 | Frequency |         |

|--------|----------------------------|----|-----------|---------|---------|-------------|-------|-----------|---------|

| D7     | D6                         | D5 | D4        | (Hz)    | D3      | D2          | D1    | D0        | (Hz)    |

| 0      | 0                          | 0  | 0         | 0 = OFF | 0       | 0           | 0     | 0         | 0 = OFF |

| 0      | 0                          | 0  | 1         | 120     | 0       | 0           | 0     | 1         | 330     |

| 0      | 0                          | 1  | 0         | 150     | 0       | 0           | 1     | 0         | 416     |

| 0      | 0                          | 1  | 1         | 154     | 0       | 0           | 1     | 1         | 420     |

| 0      | 1                          | 0  | 0         | 250     | 0       | 1           | 0     | 0         | 425     |

| 0      | 1                          | 0  | 1         | 300     | 0       | 1           | 0     | 1         | 433     |

| 0      | 1                          | 1  | 0         | 350     | 0       | 1           | 1     | 0         | 440     |

| 0      | 1                          | 1  | 1         | 360     | 0       | 1           | 1     | 1         | 450     |

| 1      | 0                          | 0  | 0         | 367     | 1       | 0           | 0     | 0         | 460     |

| 1      | 0                          | 0  | 1         | 375     | 1       | 0           | 0     | 1         | 480     |

| 1      | 0                          | 1  | 0         | 380     | 1       | 0           | 1     | 0         | 500     |

| 1      | 0                          | 1  | 1         | 383     | 1       | 0           | 1     | 1         | 600     |

| 1      | 1                          | 0  | 0         | 400     | 1       | 1           | 0     | 0         | 620     |

| 1      | 1                          | 0  | 1         | 450     | 1       | 1           | 0     | 1         | 720     |

| 1      | 1                          | 1  | 0         | 475     | 1       | 1           | 1     | 0         | 930     |

| 1      | 1                          | 1  | 1         | 480     | 1       | 1           | 1     | 1         | -       |

Digital Line to POTS Interface CMX605

Tone Field 2, MODE Register bit 1 and bit 0 = '1' and '0' respectively

| TX TONI | ES Regis | ter Bits | 4-7 | Frequency | TX TC | NES Reg | gister Bits | 0-3 | Frequency |

|---------|----------|----------|-----|-----------|-------|---------|-------------|-----|-----------|

| D7      | D6       | D5       | D4  | (Hz)      | D3    | D2      | D1          | D0  | (Hz)      |

| 0       | 0        | 0        | 0   | 0 = OFF   | 0     | 0       | 0           | 0   | 0 = OFF   |

| 0       | 0        | 0        | 1   | 700       | 0     | 0       | 0           | 1   | 700       |

| 0       | 0        | 1        | 0   | 900       | 0     | 0       | 1           | 0   | 900       |

| 0       | 0        | 1        | 1   | 1100      | 0     | 0       | 1           | 1   | 1100      |

| 0       | 1        | 0        | 0   | 1300      | 0     | 1       | 0           | 0   | 1300      |

| 0       | 1        | 0        | 1   | 1500      | 0     | 1       | 0           | 1   | 1500      |

| 0       | 1        | 1        | 0   | 1700      | 0     | 1       | 1           | 0   | 1700      |

| 0       | 1        | 1        | 1   | -         | 0     | 1       | 1           | 1   | -         |

| 1       | 0        | 0        | 0   | 950       | 1     | 0       | 0           | 0   | 2100      |

| 1       | 0        | 0        | 1   | 1400      | 1     | 0       | 0           | 1   | 2225      |

| 1       | 0        | 1        | 0   | 1800      | 1     | 0       | 1           | 0   | -         |

| 1       | 0        | 1        | 1   | 2130      | 1     | 0       | 1           | 1   | 2750      |

| 1       | 1        | 0        | 0   | 697       | 1     | 1       | 0           | 0   | 1209      |

| 1       | 1        | 0        | 1   | 770       | 1     | 1       | 0           | 1   | 1336      |

| 1       | 1        | 1        | 0   | 852       | 1     | 1       | 1           | 0   | 1477      |

| 1       | 1        | 1        | 1   | 941       | 1     | 1       | 1           | 1   | 1633      |

Tone Field 3, MODE Register bit 1 and bit 0 = '1' and '1' respectively

| TX TON | TX TONES Register Bits 4-7 |    | Frequency | TX TO   | TX TONES Register Bits 0-3 |    |    | Frequency |         |

|--------|----------------------------|----|-----------|---------|----------------------------|----|----|-----------|---------|

| D7     | D6                         | D5 | D4        | (Hz)    | D3                         | D2 | D1 | D0        | (Hz)    |

| 0      | 0                          | 0  | 0         | 0 = OFF | 0                          | 0  | 0  | 0         | 0 = OFF |

| 0      | 0                          | 0  | 1         | 540     | 0                          | 0  | 0  | 1         | 540     |

| 0      | 0                          | 1  | 0         | 660     | 0                          | 0  | 1  | 0         | 660     |

| 0      | 0                          | 1  | 1         | 780     | 0                          | 0  | 1  | 1         | 780     |

| 0      | 1                          | 0  | 0         | 900     | 0                          | 1  | 0  | 0         | 900     |

| 0      | 1                          | 0  | 1         | 1020    | 0                          | 1  | 0  | 1         | 1020    |

| 0      | 1                          | 1  | 0         | 1140    | 0                          | 1  | 1  | 0         | 1140    |

| 0      | 1                          | 1  | 1         | -       | 0                          | 1  | 1  | 1         | -       |

| 1      | 0                          | 0  | 0         | 1380    | 1                          | 0  | 0  | 0         | 1380    |

| 1      | 0                          | 0  | 1         | 1500    | 1                          | 0  | 0  | 1         | 1500    |

| 1      | 0                          | 1  | 0         | 1620    | 1                          | 0  | 1  | 0         | 1620    |

| 1      | 0                          | 1  | 1         | 1740    | 1                          | 0  | 1  | 1         | 1740    |

| 1      | 1                          | 0  | 0         | 1860    | 1                          | 1  | 0  | 0         | 1860    |

| 1      | 1                          | 0  | 1         | 1980    | 1                          | 1  | 0  | 1         | 1980    |

| 1      | 1                          | 1  | 0         | -       | 1                          | 1  | 1  | 0         | -       |

| 1      | 1                          | 1  | 1         | -       | 1                          | 1  | 1  | 1         | -       |

### 1.5.4 SPM Generator

This block operates independently and has its own output pin. It can transmit 12kHz or 16kHz and is controlled by bit 4 of the SETUP Register. Bit 7 of the MODE Register is used to enable or disable this block. The signal has a rise and fall time each of about 4.5ms. The SPM signal rises from the bias level to 0dBm in 16 steps of ©2dB magnitude, and falls from 0dBm to bias level in 16 steps of ©2dB magnitude.

### 1.5.5 Transmit Signal Control

This block adjusts the amplitude of the FSK transmit signal output level, the level skew between DTMF tones and the signal routing to the output ports.

Output signal levels are proportional to  $V_{DD}$ . The nominal output signal levels (at 0dB attenuation and  $V_{DD} = 5.0V$ ) are:

| Single Tone              | 0dBm  |

|--------------------------|-------|

| Dual Tone (per tone)     | -3dBm |

| DTMF High Frequency Tone | -3dBm |

| DTMF Low Frequency Tone  | -5dBm |

| FSK Signal               | 0dBm  |

The RING signal is digital: a square wave with amplitude of  $\approx V_{DD}$  peak to peak. When the RING signal is not selected, the RING output pin is connected to  $V_{SS}$ .

The level attenuator provides for level adjustment from 0dB to -14dB in -2dB steps. The typical level is determined by bits 2 to 4 of the MODE Register as shown in the table below:

| MODE  | Register |       | Signal Level Adjustment |

|-------|----------|-------|-------------------------|

| Bit 4 | Bit 3    | Bit 2 | (dB)                    |

| 0     | 0        | 0     | 0                       |

| 0     | 0        | 1     | -2                      |

| 0     | 1        | 0     | -4                      |

| 0     | 1        | 1     | -6                      |

| 1     | 0        | 0     | -8                      |

| 1     | 0        | 1     | -10                     |

| 1     | 1        | 0     | -12                     |

| 1     | 1        | 1     | -14                     |

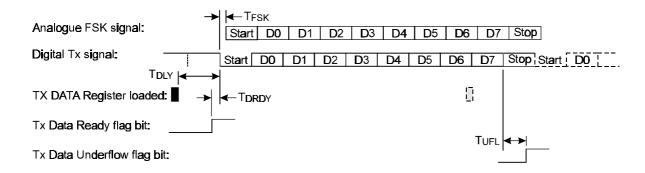

### 1.5.6 Tx UART

This block connects the  $\mu$ C, via the 'C-BUS' interface, to the FSK Encoder.

The block can be programmed to convert transmit data from 8-bit bytes to asynchronous data characters by adding Start and Stop bits. The transmit data is then passed to the FSK Encoder.

Data to be transmitted should be loaded by the  $\mu$ C into the TX DATA Register when the Tx Data Ready bit (bit 6) of the STATUS Register goes high. It will then be treated by the Tx UART block in one of two ways, depending on the setting of bit 1 of the SETUP Register:

If bit 1 of the SETUP Register is '0' (Tx Sync mode) then the 8 bits from the TX DATA Register will be transmitted sequentially at 1200bps, lsb (D0) first.

If bit 1 of the SETUP Register is '1' (Tx Async mode) then bits will be transmitted as asynchronous data characters at 1200 bps according to the following format:

One Start bit (Space)

Eight Data bits (D0-D7) from the TX DATA Register, with the lsb (D0) transmitted first

One Stop bit (Mark)

Failure to load the TX DATA Register with a new value when required will result in bit 7 (Tx Data Underflow) of the STATUS Register being set to '1'. If the 'Tx Async' mode of operation is selected then a continuous Mark ('1') signal will be transmitted until a new value is loaded into TX DATA. If the 'Tx Sync' mode is selected then the byte already in the TX DATA Register will be re-transmitted.

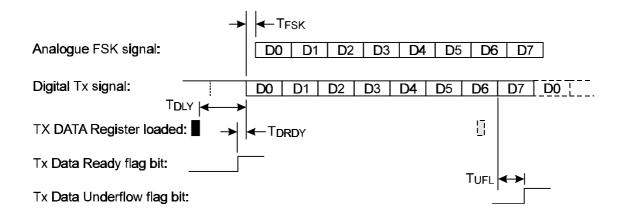

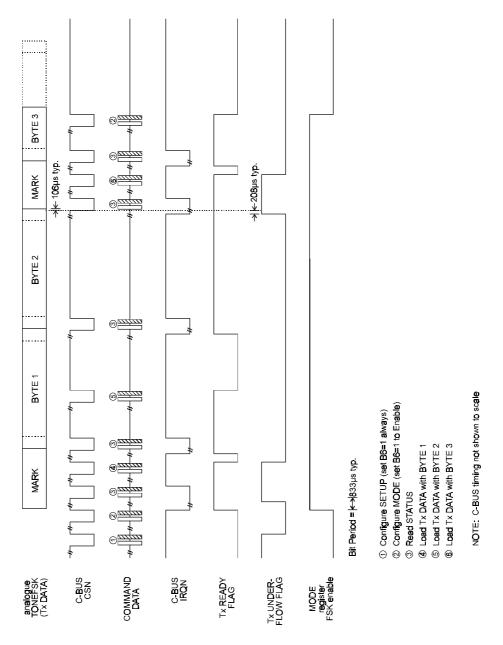

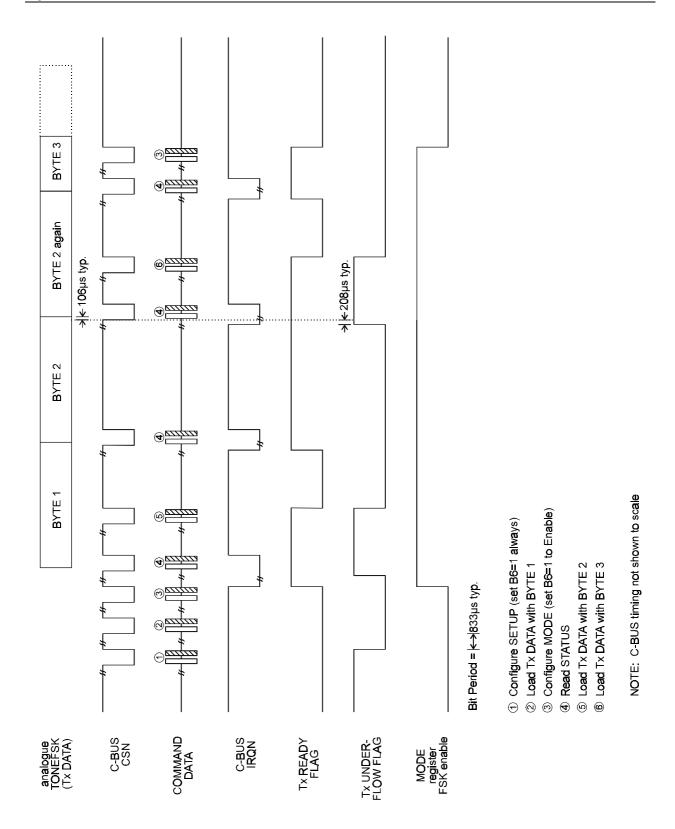

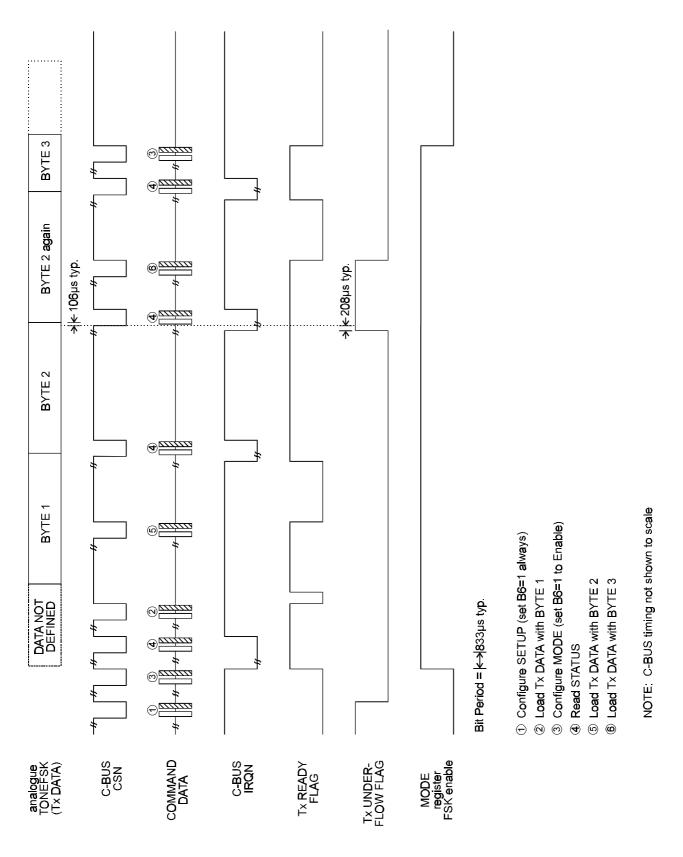

Figure 3a Transmit UART Function (Async)

Figure 3b Transmit UART Function (Sync)

### 1.5.7 DTMF Tone Decoder

This block is enabled or disabled by bit 5 of the SETUP register. If disabled, bit 0 to bit 5 of the STATUS Register are set to '0' and no interrupts are generated. When enabled (set to '1'), a status change of the decoder will generate an interrupt and bit 5 of the STATUS Register will be set to '1'. The validity of the data is indicated by bit 4 of the STATUS Register. The decode truth table is shown below:

| STATUS | Register E | 3its 0 - 3 |       | DTMF Tone       | Pairs           |        |

|--------|------------|------------|-------|-----------------|-----------------|--------|

| Bit 3  | Bit 2      | Bit 1      | Bit 0 | Lower Frequency | Upper Frequency | Keypad |

| (D3)   | (D2)       | (D1)       | (D0)  | (Hz)            | (Hz)            | Legend |

| 0      | 0          | 0          | 0     | 941             | 1633            | D      |

| 0      | 0          | 0          | 1     | 697             | 1209            | 1      |

| 0      | 0          | 1          | 0     | 697             | 1336            | 2      |

| 0      | 0          | 1          | 1     | 697             | 1477            | 3      |

| 0      | 1          | 0          | 0     | 770             | 1209            | 4      |

| 0      | 1          | 0          | 1     | 770             | 1336            | 5      |

| 0      | 1          | 1          | 0     | 770             | 1477            | 6      |

| 0      | 1          | 1          | 1     | 852             | 1209            | 7      |

| 1      | 0          | 0          | 0     | 852             | 1336            | 8      |

| 1      | 0          | 0          | 1     | 852             | 1477            | 9      |

| 1      | 0          | 1          | 0     | 941             | 1336            | 0      |

| 1      | 0          | 1          | 1     | 941             | 1209            | *      |

| 1      | 1          | 0          | 0     | 941             | 1477            | #      |

| 1      | 1          | 0          | 1     | 697             | 1633            | Α      |

| 1      | 1          | 1          | 0     | 770             | 1633            | В      |

| 1      | 1          | 1          | 1     | 852             | 1633            | С      |

A status change of the decoder and the generation of an interrupt will occur both when a tone is first decoded and also when a tone, which was previously present, is no longer decoded. In the latter case, Bit 4 of the STATUS Register will be set to "0" to indicate that no tone was detected.

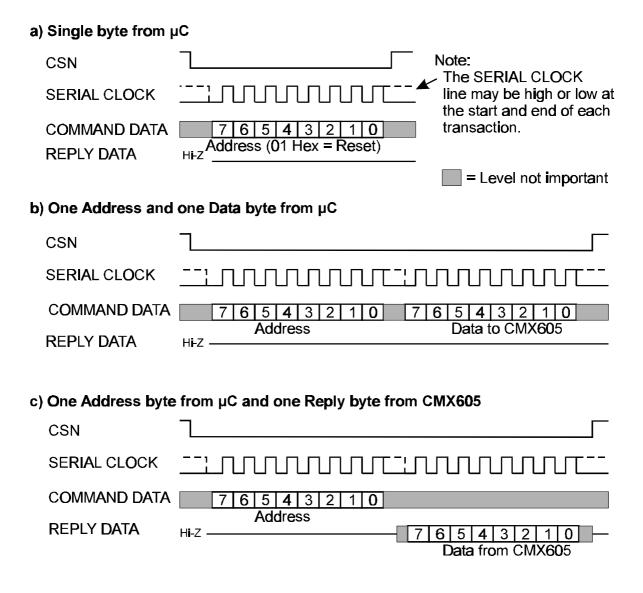

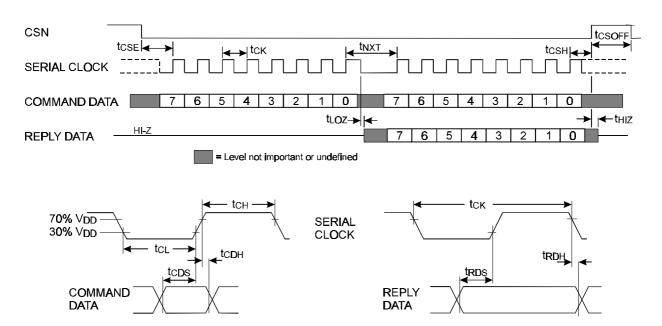

### 1.5.8 'C-BUS' Interface

This block provides for the transfer of data and control or status information between the CMX605's internal registers and the  $\mu$ C over the 'C-BUS' serial bus. Each transaction consists of a single Register Address byte sent from the  $\mu$ C which may be followed by a single data byte sent from the  $\mu$ C to be written into one of the CMX605's Write Only Registers, or a single byte of data read out from one of the CMX605's Read Only Registers, as illustrated in Figure 4.

Data sent from the  $\mu$ C on the Command Data (COMDATA) line is clocked into the CMX605 on the rising edge of the Serial Clock (SERCK) input. Reply Data (REPDATA) sent from the CMX605 to the  $\mu$ C is valid when the Serial Clock is high. The interface is compatible with the most common  $\mu$ C serial interfaces such as SCI, SPI and Microwire, and may also be easily implemented with general purpose  $\mu$ C I/O pins controlled by a simple software routine. See Figure 8 for detailed 'C-BUS' timing requirements.

Figure 4 'C-BUS' Transactions

# 1.5.9 'C-BUS' Registers

# **Write Only Registers**

|       |             | Command Data Byte (Bits 7 - 0)                        |                                         |                                       |                                |                   |                   |                                    |                                            |

|-------|-------------|-------------------------------------------------------|-----------------------------------------|---------------------------------------|--------------------------------|-------------------|-------------------|------------------------------------|--------------------------------------------|

| Addr. | Register    | 7                                                     | 6                                       | 5                                     | 4                              | 3                 | 2                 | 1                                  | 0                                          |

| \$01  | RESET       | N/A                                                   | N/A                                     | N/A                                   | N/A                            | N/A               | N/A               | N/A                                | N/A                                        |

| \$D0  | SETUP       | Uncommitted<br>Amplifier<br>0 = Disable<br>1 = Enable | Tx Enable:<br>0 = Disable<br>1 = Enable | DTMF Rx:<br>0 = Disable<br>1 = Enable | SPM:<br>0 = 12kHz<br>1 = 16kHz | Reserved set to 0 | Reserved set to 0 | FSK mode:<br>0 = Sync<br>1 = Async | FSK<br>mode:<br>0 = V23<br>1 = Bell<br>202 |

| \$D1  | MODE        | SPM O/P:<br>0 = Disable<br>1 = Enable                 | Tone/FSK:<br>0 = Disable<br>1 = Enable  | Tone/FSK:<br>0 = Tone<br>1 = FSK      | Tx Level:<br>(msb)             | Tx Level:         | Tx Level: (Isb)   | Tone<br>Fields:<br>(msb)           | Tone<br>Fields:<br>(Isb)                   |

| \$D3  | TX<br>DATA  | D7                                                    | D6                                      | D5                                    | D4                             | D3                | D2                | D1                                 | D0                                         |

| \$D4  | TX<br>TONES | D7                                                    | D6                                      | D5                                    | D4                             | D3                | D2                | D1                                 | D0                                         |

### **Read Only Registers**

|       |          | Reply Data Byte (Bits 7 - 0)          |                                   |                              |                                                              |                                |                          |                          |                                |

|-------|----------|---------------------------------------|-----------------------------------|------------------------------|--------------------------------------------------------------|--------------------------------|--------------------------|--------------------------|--------------------------------|

| Addr. | Register | 7                                     | 6                                 | 5                            | 4                                                            | 3                              | 2                        | 1                        | 0                              |

| \$DF  | STATUS   | FSK Mode:<br>FSK Tx Data<br>Underflow | FSK Mode:<br>FSK Tx<br>Data Ready | DTMF Rx:<br>Status<br>Change | DTMF Rx:<br>1 = Detected<br>0 = Notone<br>Timer timed<br>out | DTMF:<br>Rx Data<br>(D3) (msb) | DTMF:<br>Rx Data<br>(D2) | DTMF:<br>Rx Data<br>(D1) | DTMF:<br>Rx Data<br>(D0) (lsb) |

### Notes:

- Accessing the RESET Register over the 'C-BUS' clears all of the bits in the SETUP, MODE, TX DATA, TX TONES and STATUS registers. This will initialise the device and put it into zeropower mode. Please allow 50ms for the oscillator, V<sub>BIAS</sub> and internal circuits to stabilize when coming out of zero-power mode.

- Note that this is a single-byte 'C-BUS' transaction consisting solely of the address byte value \$01.

- 2. If any of bits 5, 6 or 7 of the STATUS Register is '1' then the IRQN output will be pulled low.

- Reading the STATUS Register clears the IRQN output and also clears bit 5 of the STATUS Register, if set. Bits 6 and 7 of the STATUS Register are cleared on writing to the TX DATA Register.

# 1.6 Application Notes

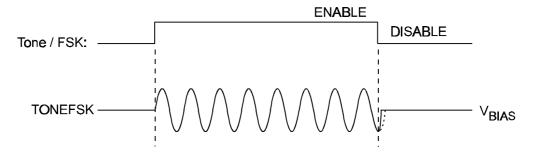

When using the Tone/FSK bit (bit 6) of the MODE Register, each tone starts from  $V_{BIAS}$ , and returns to  $V_{BIAS}$  before ending:

Figure 5 Tone Starting and Stopping

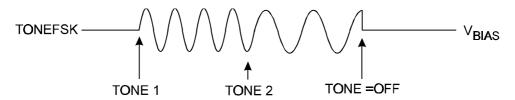

When switching between tones in the same column (bits 4 - 7 or bits 0 - 3) of the TX TONES Register), the transition will be phase continuous. However, switching to the "OFF" state will immediately take the output of that tone generator to  $V_{BIAS}$ .

Figure 6 Tone Changing

TX TONES Register decodes which do not have a frequency allocated are indicated by "-" in the Tone Field tables. These values should not be used.

### 1.6.1 Telecom Tones

The following tables give the hex codes to be programmed into the particular tone field location for various telecommunications systems applications. The tables are not exhaustive, but list the more commonly used tones.

# **Ringing Signals**

| (f ± 2.5%) | Field 0 |

|------------|---------|

| (Hz)       | (Hex)   |

| Off        | \$00    |

| 16.7       | \$01    |

| 20         | \$02    |

| 25         | \$03    |

| 35         | \$04    |

| 40         | \$05    |

| 50         | \$06    |

# On Hook 'CPE Alert Tones

| Single Tone |         |

|-------------|---------|

|             | Field 0 |

| (Hz)        | (Hex)   |

| 375.2       | \$60    |

| 404.3       | \$70    |

| 468         | \$80    |

| 495.8       | \$90    |

| 520.6       | \$A0    |

| 548         | \$B0    |

| 562.8       | \$C0    |

| 578.4       | \$D0    |

| 1633        | \$0D    |

| Dual Tone  |         |

|------------|---------|

|            | Field 0 |

| (Hz)       | (Hex)   |

| 375.2+1827 | \$6E    |

| 404.3+1827 | \$7E    |

| 468+1827   | \$8E    |

| 495.8+1827 | \$9E    |

| 520.6+1827 | \$AE    |

| 548+1827   | \$BE    |

| 562.8+1827 | \$CE    |

| 578.4+1827 | \$DE    |

|            |         |

# NYNEX (MRAA) - AMR Alert Tones (Single Tone)

| Group A           |         |

|-------------------|---------|

| <b>0.00</b> P 7 t | Field 0 |

| (Hz)              | (Hex)   |

| 252.4             | \$10    |

| 268.7             | \$20    |

| 285.3             | \$30    |

| 315.5             | \$40    |

| 330.5             | \$50    |

| 375.2             | \$60    |

| Group B |         |

|---------|---------|

|         | Field 0 |

| (Hz)    | (Hex)   |

| 468     | \$80    |

| 495.8   | \$90    |

| 520.6   | \$A0    |

| 562.8   | \$C0    |

| 595     | \$E0    |

| 612.5   | \$F0    |

# **Single Frequency Call Progress Tones**

|      | Field 1 |

|------|---------|

| (Hz) | (Hex)   |

| Off  | \$00    |

| 120  | \$10    |

| 150  | \$20    |

| 154  | \$30    |

| 250  | \$40    |

| 300  | \$50    |

| 350  | \$60    |

| 400  | \$C0    |

| 425  | \$04    |

| 440  | \$06    |

| 450  | \$07    |

| 480  | \$09    |

| 500  | \$0A    |

| 600  | \$0B    |

| 620  | \$0C    |

# **Dual Frequency Call Progress Tones**

| Additive Mixing |                  |

|-----------------|------------------|

| (Hz)            | Field 1<br>(Hex) |

| Off             | \$00             |

| 350+440         | \$66             |

| 440+480         | \$F6             |

| 480+620         | \$FC             |

| 400+425         | \$C4             |

| 400+450         | \$C7             |

| 425+450         | \$D4             |

| 425+480         | \$F4             |

| 120+620         | \$1C             |

| 150+450         | \$27             |

| Multiplicative<br>Mixing |         |

|--------------------------|---------|

| WilAirig                 | Field 1 |

| (Hz)                     | (Hex)   |

|                          |         |

| 400*16.2                 | \$B2    |

| 400*20                   | \$A3    |

| 400*25                   | \$94    |

| 400*33                   | \$85    |

| 400*40                   | \$76    |

| 400*50                   | \$67    |

| 450*25                   | \$E4    |

| 600*120                  | \$FD    |

|                          |         |

# **Dual Tone Multi Frequency Generation**

|          | Field 2 |

|----------|---------|

| (Hz)     | (Hex)   |

| Off      | \$00    |

| 941+1633 | \$FF    |

| 697+1209 | \$CC    |

| 697+1336 | \$CD    |

| 697+1477 | \$CE    |

| 770+1209 | \$DC    |

| 770+1336 | \$DD    |

| 770+1477 | \$DE    |

| 852+1209 | \$EC    |

| 852+1336 | \$ED    |

| 852+1477 | \$EE    |

| 941+1336 | \$FD    |

| 941+1209 | \$FC    |

| 941+1477 | \$FE    |

| 697+1633 | \$CF    |

| 770+1633 | \$DF    |

| 852+1633 | \$EF    |

# Special Information Tones, Fax and Modem Tones and Customer Premises Alert Tones

|           | Field 2 |

|-----------|---------|

| (Hz)      | (Hex)   |

| Off       | \$00    |

| 950       | \$80    |

| 1100      | \$30    |

| 1300      | \$40    |

| 1400      | \$90    |

| 1800      | \$A0    |

| 2100      | \$08    |

| 2225      | \$09    |

| 2130+2750 | \$BB    |

**CCITT 'R1' Signalling Tones**

|           | Field 2 |

|-----------|---------|

| (Hz)      | (Hex)   |

| 700+900   | \$12    |

| 700+1100  | \$13    |

| 900+1100  | \$23    |

| 700+1300  | \$14    |

| 900+1300  | \$24    |

| 1100+1300 | \$34    |

| 700+1500  | \$15    |

| 900+1500  | \$25    |

| 1100+1500 | \$35    |

| 1300+1500 | \$45    |

| 700+1700  | \$16    |

| 900+1700  | \$26    |

| 1100+1700 | \$36    |

| 1300+1700 | \$46    |

| 1500+1700 | \$56    |

# **CCITT 'R2' Signalling Tones**

| Forward mode |         |

|--------------|---------|

|              | Field 3 |

| (Hz)         | (Hex)   |

| Off          | \$00    |

| 1380+1500    | \$89    |

| 1380+1620    | \$8A    |

| 1500+1620    | \$9A    |

| 1380+1740    | \$8B    |

| 1500+1740    | \$9B    |

| 1620+1740    | \$AB    |

| 1380+1860    | \$8C    |

| 1500+1860    | \$9C    |

| 1620+1860    | \$AC    |

| 1740+1860    | \$BC    |

| 1380+1980    | \$8D    |

| 1500+1980    | \$9D    |

| 1620+1980    | \$AD    |

| 1740+1980    | \$BD    |

| 1860+1980    | \$CD    |

| Backward mode |         |

|---------------|---------|

|               | Field 3 |

| (Hz)          | (Hex)   |

| Off           | \$00    |

| 1140+1020     | \$65    |

| 1140+900      | \$64    |

| 1020+900      | \$54    |

| 1140+780      | \$63    |

| 1020+780      | \$53    |

| 900+780       | \$43    |

| 1140+660      | \$62    |

| 1020+660      | \$52    |

| 900+660       | \$42    |

| 780+660       | \$32    |

| 1140+540      | \$61    |

| 1020+540      | \$51    |

| 900+540       | \$41    |

| 780+540       | \$31    |

| 660+540       | \$21    |

# 1.6.2 C-BUS Timing

The relationship between bytes loaded onto the C-BUS and the transmission of FSK bytes is shown diagrammatically in Figures 7a, 7b and 7c.

There are many ways in which the C-BUS can be used to program a device and three suggestions (one for asynchronous FSK - Figure 7a - and two for synchronous FSK - Figures 7b and 7c) are shown here, together with typical timings. Please note that the C-BUS timing is not shown to the same scale as the FSK output (it has been magnified by at least 20 times to make it visible on the same scale).

Figure 7a ASYNC mode after GENERAL RESET

Digital Line to POTS Interface CMX605

Figure 7b SYNC mode after GENERAL RESET

Digital Line to POTS Interface CMX605

Figure 7c SYNC mode after GENERAL RESET (using alternative order of commands)

# 1.7 Performance Specification

# 1.7.1 Electrical Performance

# 1.7.1.1 Absolute Maximum Ratings

Exceeding these maximum ratings can result in damage to the device.

|                                                                 | Min. | Max.           | Unit |

|-----------------------------------------------------------------|------|----------------|------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> )                     | -0.3 | 7.0            | V    |

| Voltage on any pin to V <sub>SS</sub>                           | -0.3 | $V_{DD} + 0.3$ | V    |

| Current into or out of V <sub>DD</sub> and V <sub>SS</sub> pins | -50  | +50            | mA   |

| Current into or out of any other pin                            | -20  | +20            | mA   |

| D4/P3 Package                                    | Min. | Max. | Unit  |

|--------------------------------------------------|------|------|-------|

| Total Allowable Power Dissipation at Tamb = 25°C |      | 800  | mW    |

| Derating                                         |      | 13   | mW/°C |

| Storage Temperature                              | -55  | +125 | °C    |

| Operating Temperature                            | -40  | +85  | °C    |

# 1.7.1.2 Operating Limits

Correct operation of the device outside these limits is not implied.

|                                             | Notes | Min.     | Max.     | Unit |

|---------------------------------------------|-------|----------|----------|------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> ) |       | 2.7      | 5.5      | V    |

| Operating Temperature                       |       | -40      | +85      | °C   |

| Xtal Frequency                              | 1     | 3.575965 | 3.583125 | MHz  |

**Notes:** 1. A Xtal frequency of 3.579545MHz ±0.1% is required for correct operation.

# 1.7.1.3 Operating Characteristics

For the following conditions unless otherwise specified:

$V_{DD}$  = 2.7V at Tamb = 25°C and  $V_{DD}$  = 3.0V to 5.5V at Tamb = -40 to +85°C,

Xtal Frequency =  $3.579545MHz \pm 0.1\%$

0dBm corresponds to 775mVrms.

| DC Parameters                                       | Notes | Min.          | Тур. | Max. | Unit      |

|-----------------------------------------------------|-------|---------------|------|------|-----------|

| I <sub>DD</sub> Zero-power mode                     | 1     | -             | 1.0  | 10.0 | μA        |

| OpAmp only Enabled ( $V_{DD} = 5.0V$ )              | 1     | -             | 1.0  | -    | mΑ        |

| DTMF Rx only, $V_{DD} = 5.0V$                       | 1     | -             | 2.0  | 3.2  | mΑ        |

| Tx (tones, SPM) only, $V_{DD} = 5.0V$               | 1     | -             | 3.5  | 5.5  | mΑ        |

| All Enabled, $V_{DD} = 5.0V$                        | 1     | -             | 6.6  | 10.0 | mΑ        |

| OpAmp only Enabled ( $V_{DD} = 3.3V$ )              | 1     | -             | 0.75 | -    | mΑ        |

| DTMF Rx only, $V_{DD} = 3.3V$                       | 1     | -             | 1.2  | 2.5  | mΑ        |

| Tx (tones, SPM) only, $V_{DD} = 3.3V$               | 1     | -             | 2.0  | 3.0  | mΑ        |

| All Enabled, $V_{DD} = 3.3V$                        | 1     | -             | 3.5  | 5.5  | mΑ        |

| Logic '1' Input Level                               | 3     | 70%           | -    | -    | $V_{DD}$  |

| Logic '0' Input Level                               | 3     | -             | -    | 30%  | $V_{DD}$  |

| Logic Input Leakage Current (Vin = 0 to $V_{DD}$ ), | 3     | -1.0          | -    | +1.0 | μΑ        |

| (excluding XTAL/CLOCK input)                        |       |               |      |      |           |

| Output Logic '1' Level ( $I_{OH} = 360\mu A$ )      |       | $V_{DD}$ -0.4 | -    | -    | V         |

| Output Logic '0' Level ( $I_{OL} = 360\mu A$ )      |       | -             | -    | 0.4  | V         |

| IRQN O/P 'Off State Current ( $V_{OUT} = V_{DD}$ )  |       | -             | -    | 1.0  | μΑ        |

| FSK Encoder and Tx UART                             | Notes | Min.          | Тур. | Max. | Unit      |

| Level at TONEFSK pin                                | 4     | -1.0          | 0.0  | 1.0  | dBm       |

| Twist (Mark level WRT Space level)                  |       | -2.0          | 0    | +2.0 | dB        |

| Tx 1200bits/sec (V23 mode)                          |       |               |      |      |           |

| Baud Rate (set by UART and Xtal frequency)          |       | 1194          | 1200 | 1206 | Baud      |

| Mark (Logical 1) Frequency                          |       | 1297          | 1300 | 1303 | Hz        |

| Space (Logical 0) Frequency                         |       | 2097          | 2100 | 2103 | Hz        |

| Tx 1200bits/sec (Bell 202 mode)                     |       |               |      |      |           |

| Baud Rate (set by UART and Xtal frequency)          |       | 1194          | 1200 | 1206 | Baud      |

| Mark (Logical 1) Frequency                          |       | 1197          | 1200 | 1203 | Hz        |

| Space (Logical 0) Frequency                         |       | 2197          | 2200 | 2203 | Hz        |

| TONEFSK Signal Level                                | Notes | Min.          | Тур. | Max. | Unit      |

| Level at TONEFSK pin for:                           |       |               |      |      |           |

| Single tone                                         | 4     | -1.0          | 0    | 1.0  | dBm       |

| Dual tone (per tone)                                | 4     | -4.0          | -3.0 | -2.0 | dBm       |

| DTMF High Frequency Group                           | 4     | -4.0          | -3.0 | -2.0 | dBm       |

| DTMF Low Frequency Group                            | 4     | -6.0          | -5.0 | -4.0 | dBm       |

| Output Impedance                                    |       | -             | 10.0 | -    | $k\Omega$ |

| Tone frequency resolution                           |       | -2.0          | -    | 2.0  | Hz        |

| Tone output distortion                              | 5     | -             | 8.0  | -    | %         |

Notes:

- 1. At 25°C, not including any current drawn from the CMX605 pins by external circuitry other than X1, C1 and C2.

- 2. At nominal signal frequencies and without skew.

- 3. Excluding XTAL/CLOCK pin.

- 4. At  $V_{DD}$  = 5.0V, load resistance greater than 40k $\Omega$ , signal levels are proportional to  $V_{DD}$ .

- 5. Frequency above 300Hz.

- 6. SPM has a soft rise and fall time of about 4.5ms. The level changes between V<sub>BIAS</sub> and 0dBm in 2dB steps, 16 steps per rise and fall. When SPM is disabled, an extra 4.5ms falling tail end of signal should be taken into consideration.

| DTMF Decoder                           | Notes    | Min.  | Тур. | Max.  | Unit        |

|----------------------------------------|----------|-------|------|-------|-------------|

| Valid input signal levels              |          |       |      |       |             |

| (each tone of composite signal)        | 4        | -29.0 | _    | -2.0  | dBm         |

| Not decode level                       | ·        | 20.0  |      | 2.0   | <b>42</b>   |

| (either tone of composite signal)      | 4        | -     | _    | -40.0 | dBm         |

| Twist = High Tone/Low Tone             | -        | -9.0  | -    | 10.0  | dB          |

| Frequency Detect Bandwidth             |          | ±1.8  | -    | ±4.5  | %           |

| Input Impedance for RXIN (at 100Hz)    |          | -     | 0.5  | -     | $M\Omega$   |

| Dial Tone Tolerance                    | 7        | -     | -    | 0     | dB          |

| Noise Tolerance                        | 7,8      | -     | -14  | -     | dB          |

| Tone Response time                     | 2        | -     | -    | 40.0  | ms          |

| Tone De-response time                  | 2        | -     | -    | 45.0  | ms          |

| Tone burst detected                    | 2        | 40.0  | -    | -     | ms          |

| Tone burst ignored                     | 2        | -     | 20.0 | -     | ms          |

| Pause length detected                  | 2        | 40.0  | -    | -     | ms          |

| Pause length ignored                   | 2        | -     | -    | 20.0  | ms          |

|                                        |          |       |      |       |             |

| SPM Signal Level                       | Notes    | Min.  | Тур. | Max.  | Unit        |

| Level at SPM pin                       | 4, 6     | -1.5  | 0    | 1.0   | dBm         |

| Level at 31 W pin                      | 4, 6, 10 | -1.0  | 0    | 0.5   | dB          |

| Tone frequency accuracy                | 4, 0, 10 | -14.0 | -    | 14.0  | Hz          |

| Tone output distortion                 | 5        | -     | 1.2  | -     | %           |

| Output Impedance                       | -        | -     | 10.0 | -     | kΩ          |

| 2.1                                    |          |       |      |       |             |

| Haramanitta d Amanifican               | Notes    | Min   | T    | May   | l lm:4      |

| Uncommitted Amplifier                  | Notes    | Min.  | Тур. | Max.  | Unit        |

| Open Loop Gain (I/P = 1mVrms at 100Hz) |          | -     | 60.0 | -     | dB          |

| Unity Gain Bandwidth                   |          | -     | 5.0  | -     | MHz         |

| Input Impedance (at 100Hz)             |          | 10.0  | -    | -     | $M\Omega$   |

| Output Impedance (Open Loop)           |          | -     | 10.0 | -     | kΩ          |

| Power-Up Timing                        | Notes    | Min.  | Тур. | Max.  | Unit        |

| Device reset to reliable signal at     |          | -     | 50   | _     | ms          |

| OPOUT, RING, SPM or TONEFSK            |          |       | 00   |       |             |

| output pins                            |          |       |      |       |             |

|                                        |          |       |      |       |             |

| XTAL/CLOCK Input                       | Notes    | Min.  | Тур. | Max.  | Unit        |

| 'High' Pulse Width                     | 9        | 100   | -    | -     | ns          |

| 'Low' Pulse Width                      | 9        | 100   | -    | -     | ns          |

| Input Impedance (at 100Hz)             |          | -     | 1.0  | -     | $M\Omega$   |

| Gain (I/P = 1mVrms at 100Hz)           |          | 20.0  | -    | -     | dB          |

| . ,                                    |          |       |      |       | <del></del> |

Notes:

- 7. Referenced to DTMF tone of lower amplitude.

- 8. Bandwidth limited: 0 to 3.4kHz Gaussian Noise.

- 9. Timing for an external input to the XTAL/CLOCK pin.

- 10. Over the range  $V_{DD} = 3.3V$  to 5.5V at Tamb = 25°C.

|                    |                                       | Notes | Min. | Тур. | Max. | Unit |

|--------------------|---------------------------------------|-------|------|------|------|------|

| <u>'C-BUS' 1</u>   | Timings (See Figure 8)                |       |      |      |      |      |

| $t_{CSE}$          | CSN-Enable to Clock-High time         |       | 100  | -    | -    | ns   |

| $t_{CSH}$          | Last Clock-High to CSN-High time      |       | 100  | -    | -    | ns   |

| $t_{LOZ}$          | Clock-Low to Reply Output enable time |       | 0.0  | -    | -    | ns   |

| $t_{HIZ}$          | CSN-High to Reply Output 3-state time |       | -    | -    | 1.0  | μs   |

| t <sub>CSOFF</sub> | CSN-High Time between transactions    |       | 1.0  | -    | -    | μs   |

| $t_{NXT}$          | Inter-Byte Time                       |       | 500  | -    | -    | ns   |

| $t_{CK}$           | Clock-Cycle time                      |       | 500  | -    | -    | ns   |

| $t_{CH}$           | Serial Clock-High time                |       | 200  | -    | -    | ns   |

| $t_{CL}$           | Serial Clock-Low time                 |       | 200  | -    | -    | ns   |

| $t_{CDS}$          | Command Data Set-Up time              |       | 75   | -    | -    | ns   |

| $t_{CDH}$          | Command Data Hold time                |       | 25   | -    | -    | ns   |

| $t_{RDS}$          | Reply Data Set-Up time                |       | 75   | -    | -    | ns   |

| t <sub>RDH</sub>   | Reply Data Hold time                  |       | 0    | -    | -    | ns   |

Note: These timings are for the latest version of the 'C-BUS' as embodied in the CMX605, and allow faster transfers than the original 'C-BUS' timings given in CML Publication D/800/Sys/3 July 1994.

|            |                                      | Notes | Min. | Typ. | Max. | Unit |

|------------|--------------------------------------|-------|------|------|------|------|

| Typical U  | JART Timings (See Figures 3a and 3b) |       |      |      |      |      |

| $T_{FSK}$  | (delay through the modulator)        | -     | -    | 106  | -    | μs   |

| $T_DLY$    | (1 bit period)                       | -     | -    | 833  | -    | μs   |

| $T_{DRDY}$ | (1/4 bit-period)                     | -     | -    | 208  | -    | μs   |

| $T_{UFL}$  | (3/4 bit-period)                     | -     | -    | 625  | -    | μs   |

Figure 8 'C-BUS' Timing

Digital Line to POTS Interface CMX605

### 1.7.2 Packaging

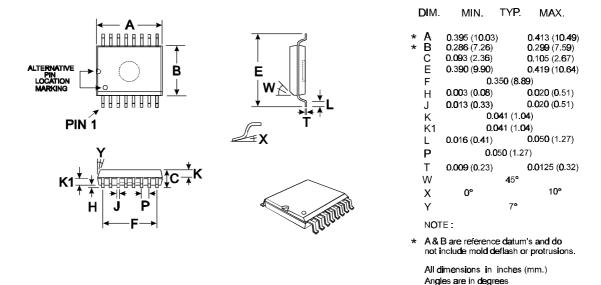

Figure 9 16-pin SOIC (D4) Mechanical Outline: Order as part no. CMX605D4

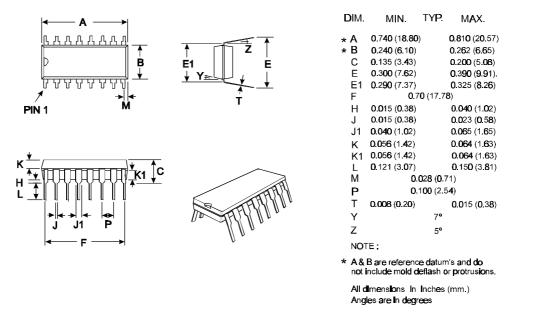

Figure 10 16-pin DIL (P3) Mechanical Outline: Order as part no. CMX605P3

Handling precautions: This product includes input protection, however, precautions should be taken to prevent device damage from electro-static discharge. CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and this product specification. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with this product specification. Specific testing of all circuit parameters is not necessarily performed.

Oval Park - LANGFORD MALDON - ESSEX CM9 6WG - ENGLAND Telephone: +44 (0)1621 875500

Telefax: +44 (0)1621 875600

e-mail: sales@cmlmicro.co.uk

http://www.cmlmicro.co.uk

### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd) have undergone name changes and, whilst maintaining their separate new names (CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

# **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

Company contact information is as below:

COMMUNICATION SEMICONDUCTORS

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050,

0800 638 5577

Fax: +1 336 744 5054

us.sales@cmlmicro.com

www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307

Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com