CML Microcircuits

D/649/2 May 2003

# Features

- Multiple Codec Modes, 16 to 128 kbps

- Full duplex ADM and CVSD

- Full duplex PCM: µ-law, A-law, Linear

- Configurable ADM time constants

- Dual channel transcoder/decoder mode

- High Performance Digital Architecture

- Low Power: 2.5mA at 3.0V typ.

- 2.7V 5.5V Supply

- Data Clock Recovery

- Programmable Voice Activity Detector (VAD)

- Adjust threshold level and attack/decay time

- Use to powersave on low signal level

- Silence/blank low level signals

- Programmable Digital Scrambler

- Flexible Interfaces

- 8-bit and 16-bit burst data with sync strobe

- 1 bit serial data with clock

- Host serial control/data interface

- Internal and External Sample Clocking

- Programmable Filters

- Encoder mic input ADC anti-alias

- Decoder audio out DAC anti-imaging

- Low Noise Differential Mic Input Amp

- Programmable Analog Interface Gain

- Microphone in

- Decoder audio out

- Sidetone path

# **Applications**

- Low Cost Digital Cordless Headset

- Personal Area Network (PAN) Voice Link

- Digital Cordless Telephone

- Wireless Digital PBX

- Full Duplex Digital Radio Systems

- Time Division Duplex (TDD) Systems

- Portable Digital Voice Communicator

- Digital Voice Delay

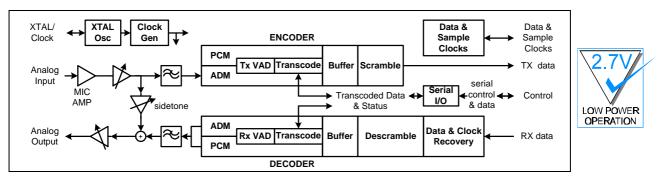

### 1. Brief Description

The CMX649 Adaptive Delta Modulation (ADM) Voice Codec provides full duplex ADM, companded ( $\mu$ /A-law) PCM and linear PCM codec and transcoder functions for cost effective, low power, wireless voice applications. Selectable modes and algorithms support many applications. Robust ADM coding (e.g. CVSD) reduces host protocol and software burdens, eliminating forward error correction, framing protocols and algorithm processing. Dual transcode/decode mode supports multichannel applications.

Integrated filter responses adjust independent of 16kbps to 128kbps codec data rates. Codec sample clocks are externally applied or internally generated. High performance analog interfaces and sidetone include digital gain controls. Encoder and decoder voice activity detectors support powersaving.

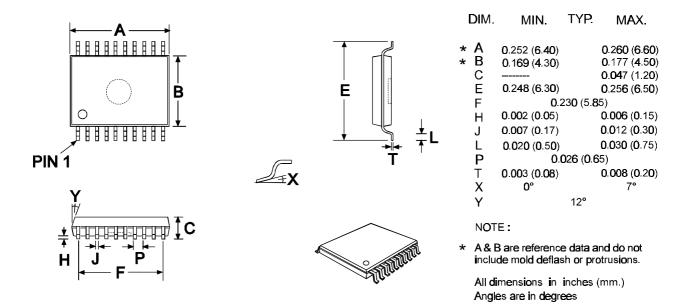

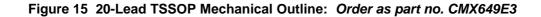

The CMX649 ADM Voice Codec supports 2.7V to 5.5V operation and is available in 20-pin SOIC (D3) and TSSOP packages (E3) packages.

CMX649

**ADM Codec**

Provisional Issue

### CONTENTS

| <u>Section</u> | Pag                                        | e |

|----------------|--------------------------------------------|---|

| 1.             | Brief Description1                         |   |

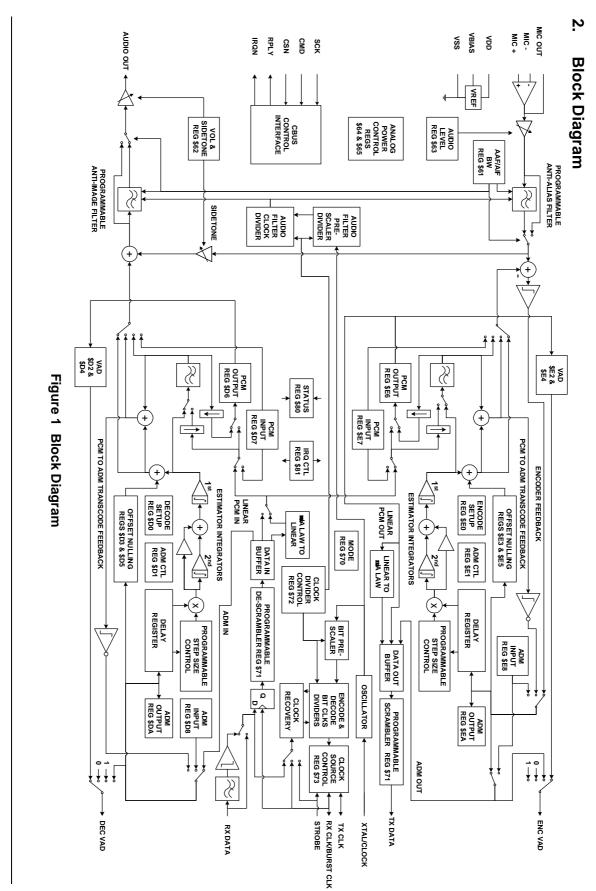

| 2.             | Block Diagram3                             |   |

| 3.             | Signal List4                               |   |

| 4.             | External Components5                       |   |

| 5.             | General Description                        |   |

| 6.             | 5.2.2       Read Only Register Description |   |

|                | 5.1C-BUS Operation                         |   |

| 7.             | Performance Specification                  |   |

ω

© 2003 CML Microsystems Plc

D/649/2

CMX649

ADM Codec

#### 3. Signal List

| SOIC (D3)<br>Package | TSSOP (E3)<br>Package | Signal                     |                                | Description                                                                                                                                                                        |

|----------------------|-----------------------|----------------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.              | Pin No.               | Name                       | Туре                           |                                                                                                                                                                                    |

| 1                    | 1                     | STRB                       | Digital Input                  | Strobe signal for 8/16 buffered serial I/O.                                                                                                                                        |

| 2                    | 2                     | ENC VAD                    | Digital Output                 | Encoder voice activity detector output.                                                                                                                                            |

| 3                    | 3                     | $V_{DD}$                   | Power                          | Positive supply rail.                                                                                                                                                              |

| 4                    | 4                     | MIC OUT                    | Analog Output                  | Analog output signal from microphone amplifier.                                                                                                                                    |

| 5                    | 5                     | MIC +                      | Analog Input                   | Analog non-inverting input to microphone amplifier.                                                                                                                                |

| 6                    | 6                     | MIC -                      | Analog Input                   | Analog inverting input to microphone amplifier.                                                                                                                                    |

| 7                    | 7                     | V <sub>BIAS</sub><br>AUDIO | Analog Output<br>Analog Output | $V_{DD}/2$ – Not suitable for external<br>applications without buffering. Pin<br>should be decoupled to $V_{SS}$ with a<br>capacitor (>1µF).<br>Analog Output signal from decoder. |

| 0                    | 0                     | OUT                        | Analog Output                  | Analog Ouput signal nom decoder.                                                                                                                                                   |

| 9                    | 9                     | $V_{SS}$                   | Power                          | Negative supply rail (Ground).                                                                                                                                                     |

| 10                   | 10                    | DEC VAD                    | Digital Output                 | Decoder voice activity detector output.                                                                                                                                            |

| 11                   | 11                    | RX DATA                    | Digital Input                  | Received signal serial data input.                                                                                                                                                 |

| 12                   | 12                    | RX CLK                     | Digital I/O                    | Decoder data clock.                                                                                                                                                                |

| 13                   | 13                    | XTAL/CLK                   | Analog Input                   | 4 – 16 MHz crystal oscillator input.                                                                                                                                               |

| 14                   | 14                    | IRQN                       | Digital Output                 | )                                                                                                                                                                                  |

| 15                   | 15                    | RPLY                       | Digital Output                 | )                                                                                                                                                                                  |

| 16                   | 16                    | CMD                        | Digital Input                  | ) C-BUS control signals.                                                                                                                                                           |

| 17                   | 17                    | SCLK                       | Digital Input                  | )                                                                                                                                                                                  |

| 18                   | 18                    | CSN                        | Digital Input                  | )                                                                                                                                                                                  |

| 19                   | 19                    | TX CLK                     | Digital I/O                    | Clock signal for encoded data out.                                                                                                                                                 |

| 20                   | 20                    | TX DATA                    | Digital Output                 | Encoded data output.                                                                                                                                                               |

Notes: I/O NC

Input/Output No Connection =

=

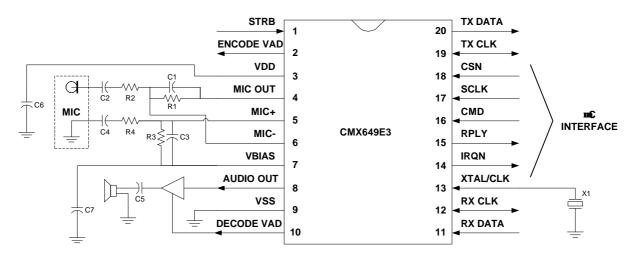

## 4. External Components

#### Figure 2 Recommended External Components

| R1, R2 | Note 1 | $100 k\Omega$ | ±10% | ( | C5 | Note 2 | 33.0μF   | ±20% |

|--------|--------|---------------|------|---|----|--------|----------|------|

| R3, R4 | Note 1 | $100 k\Omega$ | ±10% | ( | C6 | Note 3 | 1.0μF    | ±20% |

| C1, C3 | Note 1 | 100 pF        | ±20% | ( | C7 | Note 4 | 1.0μF    | ±20% |

| C2, C4 | Note 1 | 0.01µF        | ±20% |   | X1 | Note 5 | 4.096MHz |      |

#### Notes:

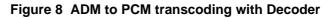

- 1. C1 C4 and R1 R4 set the microphone amplifier gain and frequency response. The values shown set the gain to unity and the low and high –3 dB frequency rolloff points to approximately 150Hz and 15kHz respectively.

- 2. DC blocking capacitor for driving a speaker from an external speaker amplifier. The value shown is based on a  $32\Omega$  impedance speaker where the highpass rolloff frequency is set to approximately 150Hz.

- 3.  $V_{DD}$  decoupling capacitor.

- 4. Bias decoupling capacitor.

- 5. A 4.096MHz Xtal/Clock input will yield exactly 16kbps/32kbps/64kbps internally generated data clock rates.

- 6. To achieve good noise performance, V<sub>DD</sub> and V<sub>BIAS</sub> decoupling and protection of the signal path from extraneous in-band signals are very important. It is recommended that the printed circuit board is laid out with a ground plane in the CMX649 area to provide a low impedance connection between the V<sub>SS</sub> pin and the V<sub>DD</sub> and V<sub>BIAS</sub> decoupling capacitors.

### 5. General Description

The CMX649 encodes and decodes analog audio signals to/from ADM, Linear PCM,  $\mu$ -law PCM or A-law PCM. It has programmable clock dividers that enable it to use a range of 4-16 MHz crystal clocks and to sample the data over a large range of data rates. Programmable current sources for on-chip op-amps enable the overall power consumption to be optimised for any given supply voltage and clocking scheme, thus achieving extremely low working power levels.

Anti-Alias Image filters and gain controls are fully programmable. All the time constants and other parameters of the ADM can be programmed for optimum performance.

The CMX649 also includes a Microphone Amplifier, Data Clock Recovery, Data Scrambler/De-Scrambler and Voice Activity Detector (VAD) circuits.

All of these parameters are controlled via C-BUS.

#### 5.1 Block Descriptions

The CMX649 contains a full duplex speech codec supporting common Adaptive Delta Modulation (ADM) and non-linear PCM coding algorithms. In addition, it supports linear PCM coding for DSP interface applications. This codec offers simple interface and application, yet is configurable to support a wide variety of speech quantisation systems.

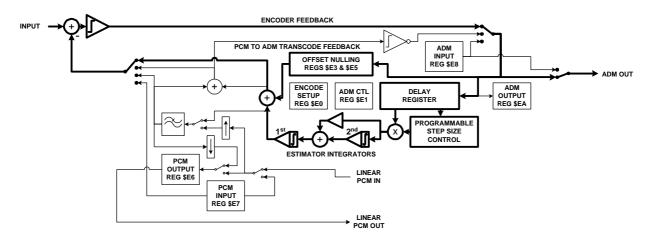

#### 5.1.1 ADM Coding Engine

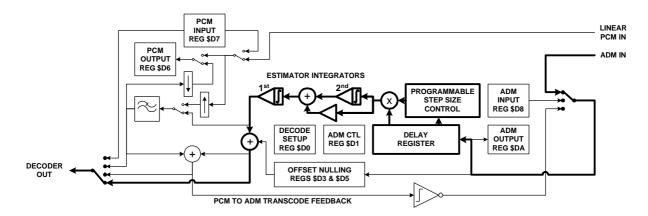

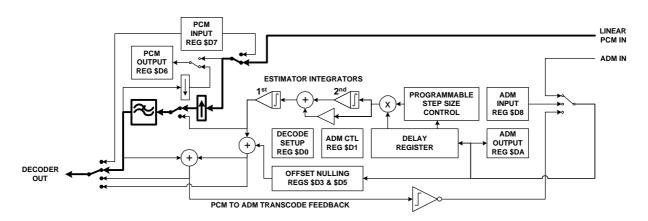

ADM is a differential waveform coding technique predominantly applied to speech. Figure 3 illustrates the ADM encoder employed. The device is for speech quantising applications and is based on popular Continuously Variable Slope Delta (CVSD) encoder approaches, with optional modifications and improvements configurable through the ENCODE and DECODE ADM CONTROL Registers (\$E1 and \$D1). Optional second order integration in the feedback loop provides improved speech quality at a given bit rate or similar quality at a lower bit rate. Toll quality is achieved at bit rates much lower than for PCM. The decoder is embedded in the encoder, as is the case with most differential encoders. Note the symmetry between the encoder and decoder of Figures 3 and 4 respectively. The signal flows for ADM are shown in bold.

Figure 3 ADM Encoding

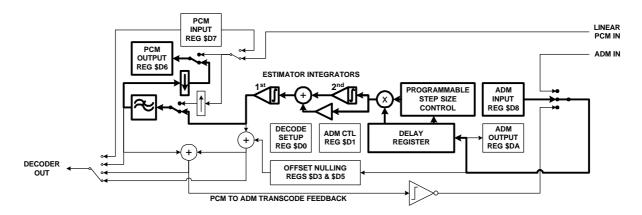

#### Figure 4 ADM Decoding

The estimator integrators (principal and second) as well as the step size decay (companding integrator) have programmable time constants. Additionally, the minimum and maximum step height and the depth of the delay register are programmable via preset values in the DECODE and ENCODE ADM CONTROL Registers (\$D1 and \$E1) to support a wide variety of different ADM algorithms including CVSD of Bluetooth<sup>™</sup> version 1.1. The switches in Figures 3 and 4 are controlled by the ENCODER and DECODER MODE and SETUP Registers (\$E0 and \$D0). Various signal flows are possible to allow standard ADM and PCM encoding and decoding as well as transcoding either direction between ADM and PCM (e.g. Figures 7 and 8). Additionally, several summing options are possible. In the decoder a PCM and ADM input stream may be summed – note that this requires at least one of the streams to be input via C-BUS. In the encoder a PCM input stream may be summed with the ADM estimate causing the encoded ADM bit stream to represent the sum of the analog input and linear PCM stream input over C-BUS.

#### 5.1.2 PCM Encoding and Decoding

Figure 5 PCM Encoding

The output of the first or principal estimator integrator in Figures 3 and 4 is linear PCM. By decimating and filtering this signal it is possible to obtain a linear PCM representation, as shown in Figures 5 and 6. Employing either 8:1 or 4:1 decimation filters provides about 30dB attenuation of out of band quantisation noise prior to decimation. The ADM coding engine, which suppresses out of band noise by roughly 20dB, provides (in conjunction with the decimating filter) an overall out of band suppression of approximately 50dB. Using second order ADM at 64kbps with the 8:1 decimation filter provides better than toll quality linear speech samples. Accordingly, 8k samples/sec linear PCM encoder performance can be enhanced when the ADM codec second order integrator is enabled and the ADM codec is operated at the maximum rate. Decoding PCM simply requires interpolation and filtering to compensate for sin(x)/x roll-off of zero holding the PCM samples. The interpolation ratio can be programmed to 4 or 8.

<sup>© 2003</sup> CML Microsystems Plc

Figure 6 PCM Decoding

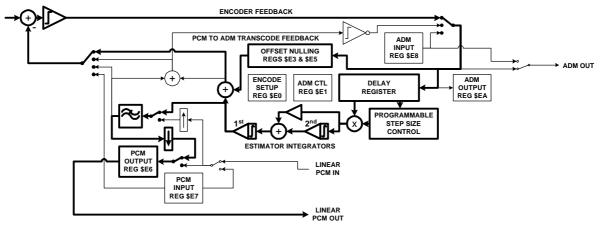

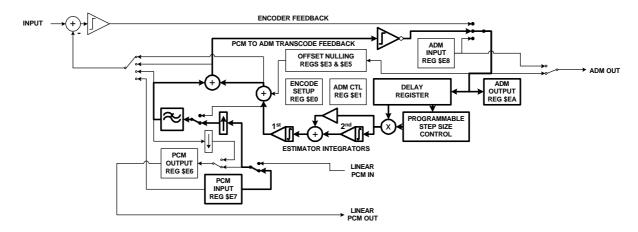

#### 5.1.3 Transcoding with the Encoder and Decoder

Figure 7 PCM to ADM transcoding with Encoder

(note that the decoder also can be configured to do this function and in this example all data is read and written via C-BUS registers \$EA (\$DA) and \$E7 (\$D7) respectively (for decoder))

(note that the encoder can also be configured to do this function and in this example all data is read and written via C-BUS registers \$D6 (\$E6) and \$D8 (\$E8) respectively (for encoder))

<sup>© 2003</sup> CML Microsystems Plc

#### 5.1.4 Non-Linear Instantaneous Companding

When using the device over its standard PCM codec style interface, instantaneous companding can be enabled to cut in half the PCM word size. Either µ-law or A-law type companding algorithms are provided and use 16-chord piecewise linear approximations. Essentially the companded 8-bit PCM word is a simple floating-point representation with a sign bit, a 3-bit exponent and a 4-bit mantissa. This approach yields toll quality speech at reduced data rates.

#### 5.1.5 Digitally Controlled Amplifiers

There are three Digitally Controlled Amplifiers (DCA) on-chip, which are used to set the signal levels for transmit-audio-in, side-tone-audio, and receive-audio-out (volume control). The transmit-audio DCA is adjustable in 0.5dB steps over a +7.5dB to -7.5dB range. The side-tone DCA is adjustable in 6.0dB steps over a 0dB to -21.0dB range. Side-tone audio is added to the audio output signal via an operational amplifier configured as a summing amplifier. This feeds the receive-audio DCA, which is adjustable in 1.5dB steps over a +12.0dB to -33.0dB range.

#### 5.1.6 Microphone Amplifier

The input amplifier is a high gain low-noise operational amplifier capable of interfacing with a variety of different microphones. Figure 9 is a simplified schematic showing the external components required for typical application with an electret condenser microphone. Typical values for R1, R3, C1 and C3 should be set according to microphone sensitivity requirements, those shown are for unity gain. Note also that the microphone biasing resistors (R5 and R6) are microphone specification dependent.

#### Figure 9 Electret Microphone - Input Amplifier Schematic

| R1, R3 | 100k $\Omega$ | ±10% | R5 | $100 k\Omega$ | ±10% |

|--------|---------------|------|----|---------------|------|

| R2, R4 | 100k $\Omega$ | ±10% | R6 | $100 k\Omega$ | ±10% |

| C1, C3 | 100 pF        | ±20% | C6 | 1.0μF         | ±20% |

| C2, C4 | 0.01µF        | ±20% | C7 | 1.0µF         | ±20% |

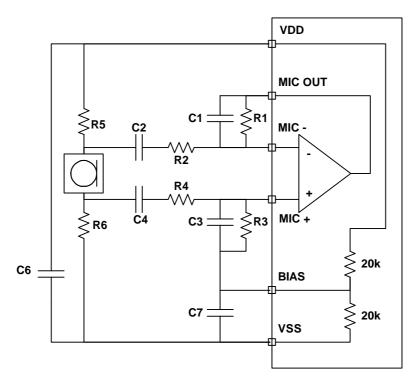

#### 5.1.7 Programmable Anti-alias/image SC Filters

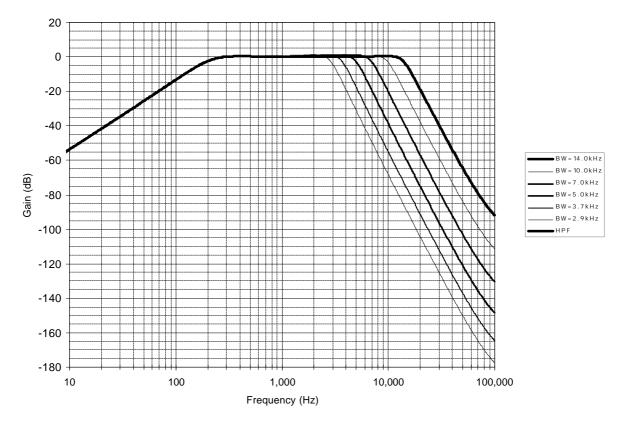

The anti-aliasing (AAF) and anti-imaging (AIF) switched capacitor (SC) filters have a programmable cutoff frequency to accommodate different input signal bandwidths. Typically, the audio filter bandwidth should be programmed to be 1/10<sup>th</sup> of the ADM bit rate (or lower) for "toll" (or better) quality audio reconstruction. For "communications" quality, the audio bandwidth may approach 1/6<sup>th</sup> of the ADM bit rate for ADM rates below 20kbps. The anti-alias/image SC filter bandwidth is programmed directly via C-BUS commands to the AAF/AIF BANDWIDTH Register (\$61). Additionally, the switched capacitor clock frequency can be altered via C-BUS commands to the CLK DIVIDER CONTROL Register (\$72). Typically, the CLK DIVIDER CONTROL Register should be programmed to provide a 256kHz SC filter clock. Altering the SC filter clock from the recommended 256kHz frequency proportionally scales the frequency axis in the plot below:

Figure 10a Typical Anti-Alias/Image Filter Frequency Response

© 2003 CML Microsystems Plc

Figure 10b Typical Anti-Image Filter Frequency Response

#### 5.1.8 Data Clock Recovery

Data from the RX DATA pin is driven into a comparator to remove amplitude variations. The output of the comparator is a logic signal that can be inverted by setting the appropriate control bit in the SCRAMBLER CONTROL Register (\$71). Using the output of the comparator, the clock recovery block can be enabled to generate a phase-locked clock equal to the CVSD data rate, which is used to clock data from the RX DATA pin into the decoder. The recovered clock frequency is controlled by the CLK DIVIDER CONTROL Register (\$72). If the clock recovery block is bypassed, data must then be applied which is synchronised to the clock on the RX CLK pin (either internally generated or externally applied).

External ADM rate bit clocks can be used for both the encoder and decoder paths and do not require use of the clock recovery PLL. Externally applied clocks act directly as the ADM sample clocks and should be generated with little jitter for best performance. Please note that the maximum usable frequency of externally applied bit clocks is 1/60<sup>th</sup> of the frequency of the output of the internal bit clock prescaler.

The clock recovery circuit is normally applied to the decoder. However, it is possible to use the recovered clock for the encoder section as well. This supports systems where the base unit is using an internal clock or local external clock for transmit and clock recovery for the decoder clock. The remote unit can then be configured to use the recovered clock for both encode and decode. Internal data clocks for the encoder and decoder can also be selected for data input and output control.

#### 5.1.9 Data Scrambler/De-scrambler

The scrambler receives digital data from the encoder. It is implemented with a 10-bit programmable linear feedback shift register (LFSR) allowing a choice of various maximal length scrambling codes. The scrambler, also known as a randomizer, provides not only a level of communication security, but may also help reduce the occurrence of abnormally long strings of 1s or 0s.

<sup>© 2003</sup> CML Microsystems Plc

The de-scrambler receives the scrambled data from the data slicer and de-scrambles it to the original data as long as the selected LFSR maximal length sequence is the same as that in the transmitting scrambler. The de-scrambler block has the same configuration as the scrambler and is self-synchronizing. Both the scrambler and de-scrambler can be bypassed.

Nine example maximal length codes are represented below through their polynomial coefficients which can be directly programmed in Bits 9-0 of the SCRAMBLER CONTROL Register (\$71):

| Length | Polynomial coefficients in hex format |

|--------|---------------------------------------|

| 2      | 0x003                                 |

| 3      | 0x006                                 |

| 4      | 0x00C                                 |

| 5      | 0x014                                 |

| 6      | 0x030                                 |

| 7      | 0x060                                 |

| 8      | 0x08E                                 |

| 9      | 0x110                                 |

| 10     | 0x240                                 |

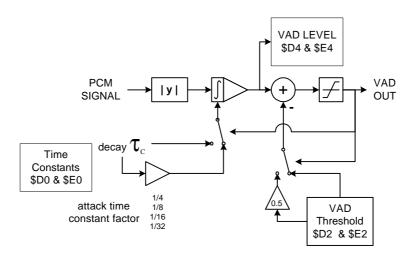

#### 5.1.10 Voice Activity Detector (VAD)

The VAD function is implemented with an energy detector circuit. This circuit consists of an absolute value function, an integrator and a threshold detector. The threshold detector level and the integrator time constants (i.e. attack and decay time control) are user programmable via the DECODE and ENCODE VAD THRESHOLD Registers (\$D2 and \$E2) and the DECODER and ENCODER MODE AND SETUP Registers (\$D0 and \$E0). Referring to Figure 11, the input to the VAD comes from the PCM signal. The signal is rectified and averaged with a lossy integrator. The output of the integrator is compared to the VAD threshold to derive the logic signal VAD\_OUT. If VAD\_OUT is a logic one, signal energy greater than the threshold is present. If VAD\_OUT is a logic zero, signal energy is below the threshold. Attack and decay times for the decoder VAD and encoder VAD can be independently controlled via the DECODER and ENCODER MODE AND SETUP Registers (\$D0 and \$E0). Typical attack and decay times used for detecting voice activity are 5ms and 150ms, respectively. The energy levels may be read from DECODE and ENCODE VAD LEVEL OUTPUT Registers (\$D4 and \$E4) for the decoder and encoder and used to adaptively set the detector threshold value by observing the energy level of background noise.

Figure 11 VAD Block Diagram

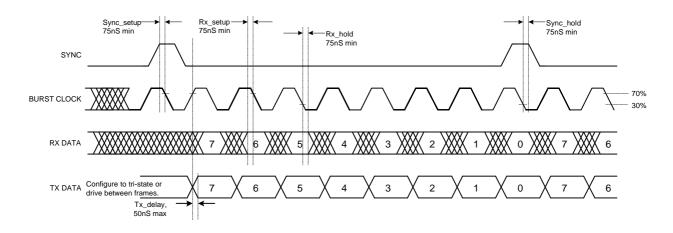

### 5.2 C-BUS Description

#### Address/Commands

Instructions and data are transferred, via C-BUS, in accordance with the timing information given in Figure 12.

Instruction and data transactions to and from the CMX649 consist of an Address/Command (A/C) byte followed by either:

- (i) a further instruction or data (1 or 2 bytes) or

- (ii) a status or Rx data reply (1 or 2 bytes)

| REGISTER<br>NAME              | HEX<br>ADDRESS/<br>COMMAN<br>D | BIT 7<br>(D7) | BIT 6<br>(D6)            | BIT 5<br>(D5)       | BIT 4<br>(D4)            | BIT3<br>(D3)                    | BIT 2<br>(D2) | BIT 1<br>(D1)              | BIT 0<br>(D0)        |

|-------------------------------|--------------------------------|---------------|--------------------------|---------------------|--------------------------|---------------------------------|---------------|----------------------------|----------------------|

| GENERAL<br>RESET              | \$01                           | Х             | Х                        | Х                   | х                        | х                               | х             | х                          | х                    |

| AAF/AIF                       | \$61                           |               | Anti-Ali                 | as Filter           |                          |                                 | Anti-Ima      | ge Filter                  |                      |

| BANDWIDTH                     |                                | By-Pass       |                          | Band-Width          | 1                        | By-Pass                         |               | Band-Width                 | ı                    |

| VOLUME/SIDE-<br>TONE LEVEL    | \$62                           |               |                          | Volume              |                          |                                 | Side          | -Tone                      | ON/OFF               |

| AUDIO INPUT<br>LEVEL CTRL     | \$63                           |               |                          | Input Level         | l                        |                                 | 0             | 0                          | 0                    |

| POWER<br>CONTROL 1            | \$64                           | 0             | Anti-<br>Alias<br>Filter | 0                   | Anti-<br>Image<br>Filter | Enc DAC Current Dec DAC Current |               |                            | C Current            |

| POWER<br>CONTROL 2            | \$65                           | Mic Amp       | Current                  | Audio Current Volum |                          | Volume                          | Current       | Xtal<br>Current            | Analog<br>Enable     |

| CODEC MODE<br>CONTROL         | \$70                           | 0             | 0                        | 0                   | 0                        | 0                               | (             | Codec Mode                 | s                    |

| SCRAMBLER                     | \$71                           | SCRAMBLER DI  |                          |                     |                          | -SCRAMBLER Polynomial           |               |                            | omial                |

| CONTROL (1)                   |                                | EN            | 0                        | INVERT              | EN                       | 0                               | INVERT        | Т9                         | T8                   |

|                               |                                |               |                          |                     | Poly                     | nomial                          |               |                            |                      |

| (2)                           |                                | T7            | T6                       | T5                  | T4                       | Т3                              | T2            | T1                         | T0                   |

| CLK DIVIDER<br>CONTROL (1)    | \$72                           | PREN          | DCKEN                    | ECKEN               | Filter P                 | re-Scaler                       |               | Filter Divide              | r                    |

| (2)                           |                                | Bit Clock     | Pre-Scaler               | Decod               | er Bit Clock             | Divider                         | Encode        | er Bit Clock               | Divider              |

| CLK SOURCE<br>CONTROL (1)     | \$73                           | 0             | 0                        |                     | etect Input<br>lect      | 0                               | 0             | 0                          | 0                    |

| (2)                           |                                | PLL EN        | Rx Bit<br>Clk<br>Select  | Tx Bit Clock Select |                          | Filter By- Slicer               |               | Iter and<br>Power<br>htrol | Data<br>Filter<br>BW |

| CODEC<br>INTERRUPT<br>CONTROL | \$81                           |               | Encode                   | Enable              |                          |                                 | Decode        | Enable                     |                      |

#### Write Only C-BUS Registers

© 2003 CML Microsystems Plc

| REGISTER<br>NAME                  | HEX<br>ADDRESS/<br>COMMAN<br>D | BIT 7<br>(D7)                                         | BIT 6<br>(D6)              | BIT 5<br>(D5) | BIT 4<br>(D4)  | BIT3<br>(D3)              | BIT 2<br>(D2)                            | BIT 1<br>(D1) | BIT 0<br>(D0)              |

|-----------------------------------|--------------------------------|-------------------------------------------------------|----------------------------|---------------|----------------|---------------------------|------------------------------------------|---------------|----------------------------|

| DECODER<br>MODE AND<br>SETUP (1)  | \$D0                           | DEC BY<br>4/8                                         | Select I                   | PCM IN        | Select         | ADM IN                    | Decoder Output<br>Select                 |               | 0                          |

| (2)                               |                                | VAD De                                                | ecay Time C                | Constant      |                | ack Time<br>stant         | Select VA<br>Sou                         |               | 0                          |

| DECODE ADM<br>CONTROL (1)         | \$D1                           | Syllat                                                | oic Time Co                | nstant        | Dynamic        | Range for S<br>Integrator | Step Size                                | Compar        | nding Rule                 |

| (2)                               |                                |                                                       | mator Integ<br>pal Time Co |               |                | Estimator<br>onstant      | Zero loca<br>2 <sup>nd</sup> C<br>Integr | rder          | Dec Zero                   |

| DECODE VAD<br>THRESHOLD<br>(1)    | \$D2                           |                                                       | Vo                         | pice Activity | Detector Th    | reshold Set               | ting Bits 15                             | - 8           |                            |

| (2)                               |                                |                                                       | V                          | oice Activit  | y Detector T   | hreshold Se               | tting Bits 7 ·                           | - 0           |                            |

| DECODE OFF-<br>SET LEVEL (1)      | \$D3                           |                                                       |                            | 0             | ffset Input L  | evel Bits 15              | - 8                                      |               |                            |

| (2)                               |                                |                                                       |                            | C             | Offset Input L | evel Bits 7 -             | - 0                                      |               |                            |

| DECODE<br>LINEAR PCM<br>INPUT (1) | \$D7                           | Direct Write to DAC Input Bits 15 - 8                 |                            |               |                |                           |                                          |               |                            |

| (2)                               |                                |                                                       |                            | Direc         | t Write to DA  | AC Input Bits             | s 7 – 0                                  |               |                            |

| DECODE ADM<br>INPUT               | \$D8                           |                                                       |                            |               | Decode A       | ADM Input                 |                                          |               |                            |

| ENCODER<br>MODE AND<br>SETUP (1)  | \$E0                           | DEC BY<br>4/8                                         | Select I                   | PCM IN        | Select         | ADM IN                    | Local D<br>Output                        |               | Idle<br>Channel<br>Enhance |

| (2)                               |                                | VAD De                                                | ecay Time C                | Constant      |                | ack Time<br>stant         | Select VA<br>Sou                         |               | ADM<br>Output<br>Select    |

| ENCODE ADM<br>CONTROL (1)         | \$E1                           | Syllab                                                | oic Time Co                | nstant        | Dynamic        | Range for S<br>Integrator | Step Size                                | Compar        | nding Rule                 |

| (2)                               |                                |                                                       | mator Integ<br>pal Time Co |               |                | Estimator<br>onstant      | Zero loca<br>2 <sup>nd</sup> C<br>Integr | rder          | Dec Zero                   |

| ENCODE VAD<br>THRESHOLD<br>(1)    | \$E2                           | Voice Activity Detector Threshold Setting Bits 15 - 8 |                            |               |                |                           |                                          |               |                            |

| (2)                               |                                |                                                       | V                          | oice Activity | y Detector T   | hreshold Se               | tting Bits 7 ·                           | - 0           |                            |

| ENCODE OFF-<br>SET LEVEL (1)      | \$E3                           | Offset Input Level Bits 15 - 8                        |                            |               |                |                           |                                          |               |                            |

| (2)                               |                                |                                                       |                            | С             | Offset Input L | evel Bits 7 -             | - 0                                      |               |                            |

$\ensuremath{\textcircled{}^{\odot}}$  2003 CML Microsystems Plc

| REGISTER<br>NAME        | HEX<br>ADDRESS/<br>COMMAN<br>D | BIT 7<br>(D7)                         | BIT 6<br>(D6)    | BIT 5<br>(D5) | BIT 4<br>(D4) | BIT3<br>(D3) | BIT 2<br>(D2) | BIT 1<br>(D1) | BIT 0<br>(D0) |

|-------------------------|--------------------------------|---------------------------------------|------------------|---------------|---------------|--------------|---------------|---------------|---------------|

| ENCODE DAC<br>INPUT (1) | \$E7                           | Direct Write to DAC Input Bits 15 - 8 |                  |               |               |              |               |               |               |

| (2)                     |                                | Direct Write to DAC Input Bits 7 – 0  |                  |               |               |              |               |               |               |

| ENCODE ADM<br>INPUT     | \$E8                           |                                       | Encode ADM Input |               |               |              |               |               |               |

#### Read Only C-BUS Registers

| REGISTER<br>NAME                     | HEX<br>ADDRESS/<br>COMMAN<br>D | BIT 7<br>(D7)                                    | BIT 6<br>(D6) | BIT 5<br>(D5) | BIT 4<br>(D4) | BIT3<br>(D3)   | BIT 2<br>(D2)  | BIT 1<br>(D1)                                   | BIT 0<br>(D0) |  |  |  |  |

|--------------------------------------|--------------------------------|--------------------------------------------------|---------------|---------------|---------------|----------------|----------------|-------------------------------------------------|---------------|--|--|--|--|

| CODEC<br>STATUS<br>(READ)            | \$80                           |                                                  | Encode Pro    | ocess Status  |               | D              | ecode Proc     | essor Statu                                     | S             |  |  |  |  |

| DECODE VAD<br>LEVEL<br>OUTPUT (1)    | \$D4                           |                                                  |               | Voice Activ   | ity Detector  | Level Outpu    | ıt Bits 15 - 8 | 3                                               |               |  |  |  |  |

| (2)                                  |                                |                                                  |               | Voice Activ   | vity Detector | Level Outp     | ut Bits 7 - 0  |                                                 |               |  |  |  |  |

| DECODE<br>OFFSET LEVEL<br>OUTPUT (1) | \$D5                           | Offset Level Output Bits 15 - 8                  |               |               |               |                |                |                                                 |               |  |  |  |  |

| (2)                                  |                                |                                                  |               | Of            | fset Level C  | Output Bits 7  | - 0            |                                                 |               |  |  |  |  |

| DECODE<br>LINEAR PCM<br>OUTPUT (1)   | \$D6                           |                                                  |               | Linear        | PCM Outpu     | ut Signal Bits | s 15 - 8       |                                                 |               |  |  |  |  |

| (2)                                  |                                |                                                  |               | Linea         | PCM Outp      | ut Signal Bit  | s 7 - 0        |                                                 |               |  |  |  |  |

| DECODE ADM<br>OUTPUT                 | \$DA                           |                                                  |               |               | Decode A      | DM Output      |                |                                                 |               |  |  |  |  |

| ENCODE VAD<br>LEVEL<br>OUTPUT (1)    | \$E4                           | Voice Activity Detector Level Output Bits 15 - 8 |               |               |               |                |                |                                                 |               |  |  |  |  |

| (2)                                  |                                |                                                  |               | Voice Activ   | vity Detector | Level Outp     | ut Bits 7 - 0  | Voice Activity Detector Level Output Bits 7 - 0 |               |  |  |  |  |

| REGISTER<br>NAME                     | HEX<br>ADDRESS/<br>COMMAN<br>D | BIT 7<br>(D7)                       | BIT 6<br>(D6)                        | BIT 5<br>(D5) | BIT 4<br>(D4) | BIT3<br>(D3) | BIT 2<br>(D2) | BIT 1<br>(D1) | BIT 0<br>(D0) |

|--------------------------------------|--------------------------------|-------------------------------------|--------------------------------------|---------------|---------------|--------------|---------------|---------------|---------------|

| ENCODE<br>OFFSET LEVEL<br>OUTPUT (1) | \$E5                           | Offset Level Output Bits 15 - 8     |                                      |               |               |              |               |               |               |

| (2)                                  |                                | Offset Level Output Bits 7 - 0      |                                      |               |               |              |               |               |               |

| ENCODE<br>LINEAR PCM<br>OUTPUT (1)   | \$E6                           |                                     | Linear PCM Output Signal Bits 15 - 8 |               |               |              |               |               |               |

| (2)                                  |                                | Linear PCM Output Signal Bits 7 - 0 |                                      |               |               |              |               |               |               |

| ENCODE ADM<br>OUTPUT                 | \$EA                           | Encode ADM Output                   |                                      |               |               |              |               |               |               |

#### 5.2.1 Write Only Register Description

#### GENERAL RESET (\$01)

The reset command has no data attached to it. Application of the GENERAL RESET sets all write only register bits to 0.

#### AAF/AIF BANDWIDTH Register (\$61)

AAF Bypass When this bit is set to logic 1 the anti-alias filter is bypassed. (Bit 7) AAF Bondwidth The 2dB cutoff frequency of the anti-alias filter is controlled by bits 4.

AAF BandwidthThe -3dB cutoff frequency of the anti-alias filter is controlled by bits 4 - 6. The filter(Bits 6 - 4)shape is not altered other than to move the cutoff frequency.

| Bit 6 | Bit 5 | Bit 4 | -3dB Frequency |

|-------|-------|-------|----------------|

| 0     | 0     | 0     | 2.9kHz         |

| 0     | 0     | 1     | 3.7kHz         |

| 0     | 1     | 0     | 5.0kHz         |

| 0     | 1     | 1     | 7.0kHz         |

| 1     | 0     | 0     | 10.0kHz        |

| 1     | 0     | 1     | 14.0kHz        |

AIF Bypass When this bit is set to a logic 1 the anti-image filter is bypassed.

(Bit 3)

AIF Bandwidth (Bits 2 – 0) The –3dB cutoff frequency of the anti-image filter is controlled by bits 0-2. The filter shape is not altered other than to move the cutoff frequency.

<sup>© 2003</sup> CML Microsystems Plc

| Bit 2 | Bit 1 | Bit 0 | -3dB Frequency |

|-------|-------|-------|----------------|

| 0     | 0     | 0     | 2.9kHz         |

| 0     | 0     | 1     | 3.7kHz         |

| 0     | 1     | 0     | 5.0kHz         |

| 0     | 1     | 1     | 7.0kHz         |

| 1     | 0     | 0     | 10.0kHz        |

| 1     | 0     | 1     | 14.0kHz        |

#### **VOLUME/SIDETONE LEVEL Register (\$62)**

Volume Level<br/>(Bits 7 - 3)The five most significant bits in this register are used to set the gain of the volume<br/>control according to the table below:

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Increment Per Step = 1.5dB<br>Steps |

|-------|-------|-------|-------|-------|-------------------------------------|

| 0     | 0     | 0     | 0     | 0     | Off                                 |

| 0     | 0     | 0     | 0     | 1     | -33.0dB                             |

| 0     | 0     | 0     | 1     | 0     | -31.5dB                             |

| 0     | 0     | 0     | 1     | 1     | -30.0dB                             |

| 0     | 0     | 1     | 0     | 0     | -28.5dB                             |

| 0     | 0     | 1     | 0     | 1     | -27.0dB                             |

| 0     | 0     | 1     | 1     | 0     | -25.5dB                             |

| 0     | 0     | 1     | 1     | 1     | -24.0dB                             |

| 0     | 1     | 0     | 0     | 0     | -22.5dB                             |

| 0     | 1     | 0     | 0     | 1     | -21.0dB                             |

| 0     | 1     | 0     | 1     | 0     | -19.5dB                             |

| 0     | 1     | 0     | 1     | 1     | -18.0dB                             |

| 0     | 1     | 1     | 0     | 0     | -16.5dB                             |

| 0     | 1     | 1     | 0     | 1     | -15.0dB                             |

| 0     | 1     | 1     | 1     | 0     | -13.5dB                             |

| 0     | 1     | 1     | 1     | 1     | -12.0dB                             |

| 1     | 0     | 0     | 0     | 0     | -10.5dB                             |

| 1     | 0     | 0     | 0     | 1     | -9.0dB                              |

| 1     | 0     | 0     | 1     | 0     | -7.5dB                              |

| 1     | 0     | 0     | 1     | 1     | -6.0dB                              |

| 1     | 0     | 1     | 0     | 0     | -4.5dB                              |

| 1     | 0     | 1     | 0     | 1     | -3.0dB                              |

| 1     | 0     | 1     | 1     | 0     | -1.5dB                              |

| 1     | 0     | 1     | 1     | 1     | 0.0dB                               |

| 1     | 1     | 0     | 0     | 0     | 1.5dB                               |

| 1     | 1     | 0     | 0     | 1     | 3.0dB                               |

| 1     | 1     | 0     | 1     | 0     | 4.5dB                               |

| 1     | 1     | 0     | 1     | 1     | 6.0dB                               |

| 1     | 1     | 1     | 0     | 0     | 7.5dB                               |

| 1     | 1     | 1     | 0     | 1     | 9.0dB                               |

| 1     | 1     | 1     | 1     | 0     | 10.5dB                              |

| 1     | 1     | 1     | 1     | 1     | 12.0dB                              |

#### © 2003 CML Microsystems Plc

Sidetone Level<br/>(Bits 2 - 1)These bits control the gain of the sidetone signal coming from the AAF output to be<br/>summed in with the decode signal at the input to the AIF.

| Bit 2 | Bit 1 | Gain Setting |

|-------|-------|--------------|

| 0     | 0     | 0dB          |

| 0     | 1     | -9dB         |

| 1     | 0     | -15dB        |

| 1     | 1     | -21dB        |

Sidetone Enable<br/>(Bit 0)When this bit is a logic 1 the sidetone path is enabled with the gain setting controlled<br/>as shown above. When this bit is logic 0 the sidetone path is disabled.

#### AUDIO INPUT LEVEL CONTROL Register (\$63)

Audio InputThese bits are used to set the gain of the Digitally Controlled Amplifier (DCA) at the<br/>output of the microphone amplifier.

Level Control (Bits 7 – 3)

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Audio Input Gain |

|-------|-------|-------|-------|-------|------------------|

| 0     | 0     | 0     | 0     | 0     | Off              |

| 0     | 0     | 0     | 0     | 1     | -7.5dB           |

| 0     | 0     | 0     | 1     | 0     | -7.0dB           |

| 0     | 0     | 0     | 1     | 1     | -6.5dB           |

| 0     | 0     | 1     | 0     | 0     | -6.0dB           |

| 0     | 0     | 1     | 0     | 1     | -5.5dB           |

| 0     | 0     | 1     | 1     | 0     | -5.0dB           |

| 0     | 0     | 1     | 1     | 1     | -4.5dB           |

| 0     | 1     | 0     | 0     | 0     | -4.0dB           |

| 0     | 1     | 0     | 0     | 1     | -3.5dB           |

| 0     | 1     | 0     | 1     | 0     | -3.0dB           |

| 0     | 1     | 0     | 1     | 1     | -2.5dB           |

| 0     | 1     | 1     | 0     | 0     | -2.0dB           |

| 0     | 1     | 1     | 0     | 1     | -1.5dB           |

| 0     | 1     | 1     | 1     | 0     | -1.0dB           |

| 0     | 1     | 1     | 1     | 1     | -0.5dB           |

| 1     | 0     | 0     | 0     | 0     | 0.0dB            |

| 1     | 0     | 0     | 0     | 1     | 0.5dB            |

| 1     | 0     | 0     | 1     | 0     | 1.0dB            |

| 1     | 0     | 0     | 1     | 1     | 1.5dB            |

| 1     | 0     | 1     | 0     | 0     | 2.0dB            |

| 1     | 0     | 1     | 0     | 1     | 2.5dB            |

| 1     | 0     | 1     | 1     | 0     | 3.0dB            |

| 1     | 0     | 1     | 1     | 1     | 3.5dB            |

| 1     | 1     | 0     | 0     | 0     | 4.0dB            |

| 1     | 1     | 0     | 0     | 1     | 4.5dB            |

| 1     | 1     | 0     | 1     | 0     | 5.0dB            |

| 1     | 1     | 0     | 1     | 1     | 5.5dB            |

| 1     | 1     | 1     | 0     | 0     | 6.0dB            |

| 1     | 1     | 1     | 0     | 1     | 6.5dB            |

| 1     | 1     | 1     | 1     | 0     | 7.0dB            |

| 1     | 1     | 1     | 1     | 1     | 7.5dB            |

Reserved (Bits 2– 0) These bits are reserved and should be set to a logic 0.

$\ensuremath{\textcircled{}^{\odot}}$  2003 CML Microsystems Plc

#### **POWER CONTROL 1 Register (\$64)**

**AAF Power** This bit is reserved and should be set to a logic 0 Control (Bit 7)

**AAF Power** Control

This bit is dedicated to power/current control for the AAF. Note: It is necessary to keep the power level set to one of the "ON" settings when the AAF is bypassed.

(Bit 6)

| Bit 7 | Bit 6 | Power Level Setting |

|-------|-------|---------------------|

| 0     | 0     | Power down (Off).   |

| 0     | 1     | Normal operation.   |

This bit is reserved and should be set to a logic 0.

**AIF Power** Control (Bit 5)

**AIF Power** Control (Bit 4)

This bit is dedicated to power/current control for the AIF and the Sidetone DCA. Note: It is necessary to keep the power level set to one of the "ON" settings when the AIF is bypassed.

| Bit 5 | Bit 4 | Power Level Setting |

|-------|-------|---------------------|

| 0     | 0     | Power down (Off).   |

| 0     | 1     | Normal operation.   |

**Encode DAC** These bits are dedicated to power/current control for the Encode DAC. **Power Control**

(Bits 3 – 2)

| Bit 3 | Bit 2 | Power Level Setting                                   |

|-------|-------|-------------------------------------------------------|

| 0     | 0     | Power down (Off).                                     |

| 0     | 1     | Lowest power (for bit rates less than 32kbps).        |

| 1     | 0     | Low power (for bit rates between 32kbps and 64kbps).  |

| 1     | 1     | Normal operation (for bit rates greater than 64kbps). |

Decode DAC These bits are dedicated to power/current control for the Decode DAC. **Power Control**

(Bits 1 - 0)

| Bit 1 | Bit 0 | Power Level Setting                                   |

|-------|-------|-------------------------------------------------------|

| 0     | 0     | Power down (Off).                                     |

| 0     | 1     | Lowest power (for bit rates less than 32kbps).        |

| 1     | 0     | Low power (for bit rates between 32kbps and 64kbps).  |

| 1     | 1     | Normal operation (for bit rates greater than 64kbps). |

#### **POWER CONTROL 2 Register (\$65)**

MIC AMP These bits are dedicated to power/current control for the Microphone Amplifier. **Power Control**

(Bits 7 – 6)

| Bit 7 | Bit 6 | Power Level Setting                                   |

|-------|-------|-------------------------------------------------------|

| 0     | 0     | Power down (Off).                                     |

| 0     | 1     | Lowest power (for audio bandwidths less than 3.3kHz). |

| 1     | 0     | Low power (for bit rates between 3.3kHz and 10kHz).   |

| 1     | 1     | Normal operation (for audio bandwidths greater than   |

|       |       | 10kHz).                                               |

**AUDIO DCA Power Control**  These bits are dedicated to power/current control for the Audio Input Digitally Controlled Amplfier.

(Bits 5 - 4)

| Bit 5 | Bit 4 | Power Level Setting                                         |

|-------|-------|-------------------------------------------------------------|

| 0     | 0     | Power down (Off).                                           |

| 0     | 1     | Lowest power (for audio bandwidths less than 3.3kHz).       |

| 1     | 0     | Low power (for audio bandwidths between 3.3kHz and 10kHz).  |

| 1     | 1     | Normal operation (for audio bandwidths greater than 10kHz). |

**VOLUME DCA** These bits are dedicated to power/current control for the Volume Digitally Controlled **Power Control** Amplifier.

(Bits 3 - 2)

| Bit 3 | Bit 2 | Power Level Setting                                   |

|-------|-------|-------------------------------------------------------|

| 0     | 0     | Power down (Off).                                     |

| 0     | 1     | Lowest power (for bit rates less than 32kbps).        |

| 1     | 0     | Low power (for bit rates between 32kbps and 64kbps).  |

| 1     | 1     | Normal operation (for bit rates greater than 64kbps). |

**XTAL Power** When this bit is a logic 1 the one-pin crystal oscillator circuit is powered down. Save

(Bit 1)

ANALOG Enable When this bit is set to a logic 1 all of the analog circuitry (register \$64 and bits 7-2 of register \$65) is enabled. When this bit is set to a logic 0 all of the analog circuitry is (Bit 0) powered down (on-chip bandgap reference is powered down). This is equivalent to setting all of the bits of register \$64 and bits 7-2 of register \$65 to a logic 0. So to enable the AAF pabk, register \$64 bit 6 and register \$65 bit 0 must both be set to logic 1. Note that these bits control power to their respective blocks and that a signal path may still exist even if the block is power send.

#### CODEC MODE CONTROL Register (\$70)

**Reserved** These bits are reserved and should be set to a logic 0. (Bits 7 – 3)

#### CODEC MODE (Bits 2 – 0)

| Bit 2 | Bit 1 | Bit 0 | CODEC Mode                    |

|-------|-------|-------|-------------------------------|

| 0     | 0     | 0     | ADM mode without buffered I/O |

| 0     | 0     | 1     | ADM mode with buffered I/O    |

| 0     | 1     | 0     | Linear PCM with buffered I/O  |

| 0     | 1     | 1     | μ-law PCM with buffered I/O   |

| 1     | 0     | 0     | A-law PCM with buffered I/O   |

#### SCRAMBLER CONTROL Register (\$71)

| Scrambler<br>Enable<br>(Bit 15)           | Setting this bit to a logic 1 enables the scrambler.                                                                                                                   |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved<br>(Bit 14)                      | Reserved for future use. Set to '0'.                                                                                                                                   |

| Scrambler<br>Output Invert<br>(Bit 13)    | Setting this bit to a logic 1 inverts the scrambler output polarity.                                                                                                   |

| De-Scrambler<br>Enable<br>(Bit 12)        | Setting this bit to a logic 1 enables the de-scrambler.                                                                                                                |

| Reserved<br>(Bit 11)                      | Reserved for future use. Set to '0'.                                                                                                                                   |

| De-Scrambler<br>Input Invert.<br>(Bit 10) | Setting this bit to a logic 1 inverts the de-scrambler input polarity.                                                                                                 |

| LFSR Tap<br>Select<br>(Bits 9 – 0)        | These bits directly program the polynomial for the scrambler and de-scrambler:<br>PR = $B9X^9 + B8X^8 + B7X^7 + B6X^6 + B5X^5 + B4X^4 + B3X^3 + B2X^2 + B1X^1 + B0X^0$ |

$\ensuremath{\textcircled{}^{\odot}}$  2003 CML Microsystems Plc

#### CLK DIVIDER CONTROL Register (\$72)

| Pre-Scaler<br>Enable<br>(Bit 15)              | Setting this bit to a logic 1 enables the pre-scaler divider.               |

|-----------------------------------------------|-----------------------------------------------------------------------------|

| Decode Bit<br>Clock Enable<br>(Bit 14)        | Setting this bit to a logic 1 enables the decode bit clock.                 |

| Encode Bit<br>Clock Enable<br>(Bit 13)        | Setting this bit to a logic 1 enables the encode bit clock.                 |

| Filter Clock Pre-<br>Scaler<br>(Bits 12 – 11) | These bits control the internal switched capacitor filter clock pre-scaler. |

| Bit 12 | Bit 11 | Divider Ratio |

|--------|--------|---------------|

| 0      | 0      | 1             |

| 0      | 1      | 2             |

| 1      | 0      | 3             |

| 1      | 1      | 4             |

Filter ClockThese bits control the internal switched capacitor filter clock divider.Divider(Bits 10 - 8)

| Bit 10 | Bit 9 | Bit 8 | Divider Ratio |

|--------|-------|-------|---------------|

| 0      | 0     | 0     | 2.000         |

| 0      | 0     | 1     | 8.000         |

| 0      | 1     | 0     | 15.500        |

| 0      | 1     | 1     | 15.750        |

| 1      | 0     | 0     | 16.000        |

| 1      | 0     | 1     | 22.000        |

| 1      | 1     | 0     | 31.250        |

| 1      | 1     | 1     | 46.750        |

These bits control the bit clock pre-scaler.

Bit Clock Pre-Scaler (Bits 7 – 6)

| Bit 7 | Bit 6 | Divider Ratio |

|-------|-------|---------------|

| 0     | 0     | 1             |

| 0     | 1     | 2             |

| 1     | 0     | 3             |

| 1     | 1     | 4             |

#### Decode Bit Clock Divider (Bits 5 – 3)

These bits control the decode bit clock divider.

Bit 5 Bit 4 Bit 3 **Divider Ratio** 1.000 0 0 0 0 0 1 2.000 0 1 0 2.250 0 1 2.625 1 0 3.000 0 1 1 0 1 3.125 1 0 3.375 1 1 1 1 3.500

Encode Bit Clock Divider (Bits 2 – 0) These bits control the encode bit clock divider.

| Bit 2 | Bit 1 | Bit 0 | Divider Ratio |

|-------|-------|-------|---------------|

| 0     | 0     | 0     | 1.000         |

| 0     | 0     | 1     | 2.000         |

| 0     | 1     | 0     | 2.250         |

| 0     | 1     | 1     | 2.625         |

| 1     | 0     | 0     | 3.000         |

| 1     | 0     | 1     | 3.125         |

| 1     | 1     | 0     | 3.375         |

| 1     | 1     | 1     | 3.500         |

The audio filter clock divider should be programmed to set the audio filter clock as near as possible to 256kHz, via selection of the XTAL frequency and the Filter Prescaler and Filter Divider settings.

The encoder and decoder ADM bit rate clocks should be programmed to the desired ADM bit rate or PCM sample rate, multiplied by the interpolation/decimation setting of the PCM filter. The PCM filter can be programmed to run at either 4x or 8x the PCM sample rate depending on the corresponding setting in the encode/decode processors.

The encoder and decoder ADM bit rate clocks are further divided by a constant factor of 64 (unless the PLL is enabled in which case the average is near 64 but can pull off slightly depending on the reference source).

#### CLK SOURCE CONTROL Register (\$73)

| Reserved<br>(Bits 15-14)<br>Phase Detect   | These bits are reserved and should be set to a logic 0.                                                                                                                                                                                                                                                                                                                                                              |                          |         |                                                     |        |  |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------|-----------------------------------------------------|--------|--|

| Input Select<br>(Bit 13)                   |                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |         | l input clock<br>l input strobe.                    |        |  |

| (Bit 12)                                   |                                                                                                                                                                                                                                                                                                                                                                                                                      | L locks to<br>L locks to |         | ges.<br>I clock or strobe edges according to Bit 13 | value. |  |

| Reserved<br>(Bits 11-8)                    | These                                                                                                                                                                                                                                                                                                                                                                                                                | bits are r               | eserved | and should be set to a logic 0.                     |        |  |

| PLL Enable<br>(Bit 7)                      | Setting this bit to a logic 1 enables the phase locked loop in the clock recover circuit. When the PLL is enabled the decoder ADM bit clock adjusts its phase in increments of 1/32 of the programmed period to minimise noise due to timing jitter. Setting this bit to a logic 0 free-wheels the post divide by 64 decode clock divider and thus produces a bit clock which is synchronised to the XTAL/CLK input. |                          |         |                                                     |        |  |

| Decode Bit<br>Clock Select<br>(Bit 6)      | Setting this bit to a logic 1 selects the bit clock generated by the clock recovery circuit. Setting this bit to a logic 0 selects a bit clock externally applied to the RX CLK pin.                                                                                                                                                                                                                                 |                          |         |                                                     |        |  |

| Encode Bit<br>Clock Select<br>(Bits 5 – 4) | These bits allow for the selection of three different sources for the encode bit clock.                                                                                                                                                                                                                                                                                                                              |                          |         |                                                     |        |  |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit 5                    | Bit 4   | Encode Bit Clock                                    | ]      |  |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                      | Х                        | 0       | External Tx Clock Pin.                              |        |  |

|                                            |                                                                                                                                                                                                                                                                                                                                                                                                                      | ~                        |         | Let an all a O a second a large de second           | 1      |  |

| Х | 0 | External Tx Clock Pin.             |

|---|---|------------------------------------|

| 0 | 1 | Internally Generated encode clock. |

| 1 | 1 | Internally Generated from decode   |

|   |   | clock.                             |

Note that a system clock or crystal is always required on the XTAL/CLK pin, in order to generate the various internal timing signals, even when Rx and Tx Clocks are recovered from the RX DATA pin.

Setting this bit to a logic 1 bypasses the data filter and inputs the RX DATA signal **Data Filter** directly into the data slicer. **Bypass** (Bit 3) **Data Filter and** These bits are dedicated to power/current control for the data filter and slicer. **Slicer Power** Control (Bits 2 – 1) Bit 2 Bit 1 **Power Level Setting** Power down (Off). 0 0 Lowest power (for bit rates less than 32kbps). 1 0 0 Low power (for bit rates between 32kbps and 1

64kbps).

When the Data Filter and Slicer are powered off, the RX DATA input pin signal must conform to logic level amplitudes. When operating the device in buffered I/O modes, the Data Filter and Slicer should be powered off.

Normal operation (for bit rates greater than

© 2003 CML Microsystems Plc

1

1

Data FilterSetting this bit to a logic 1 forces the data filter to narrow bandwidth mode.BandwidthGit 0)

#### CODEC INTERRUPT CONTROL Register (\$81)

#### Encoder Control (Bits 7 – 4)

| Bit 7 | Bit | Bit 5 | Bit 4 | Encoder Setting                                    |

|-------|-----|-------|-------|----------------------------------------------------|

|       | 6   |       |       |                                                    |

| 0     | Х   | Х     | Х     | Encoder is disabled and reset.                     |

| 1     | 0   | 0     | 0     | Encoder is enabled to run without generating IRQs. |

| 1     | 1   | Х     | Х     | Encoder is enabled and will generate IRQs to       |

|       |     |       |       | indicate VAD status changes.                       |

| 1     | Х   | 1     | Х     | Encoder is enabled and will generate periodic      |

|       |     |       |       | IRQs to indicate whether PCM data is available or  |

|       |     |       |       | needed when transcoding.                           |

| 1     | Х   | Х     | 1     | Encoder is enabled and will generate periodic      |

|       |     |       |       | IRQs to indicate whether ADM data is available or  |

|       |     |       |       | needed when transcoding.                           |

#### Decoder Control (Bits 3 – 0)

| Bit 3 | Bit 2 | Bit 1 | Bit 0 | Decoder Setting                                                                                                                    |

|-------|-------|-------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Х     | Х     | Х     | Decoder is disabled and reset.                                                                                                     |

| 1     | 0     | 0     | 0     | Decoder is enabled to run without generating IRQs.                                                                                 |

| 1     | 1     | Х     | Х     | Decoder is enabled and will generate IRQs to indicate VAD status changes.                                                          |

| 1     | X     | 1     | Х     | Decoder is enabled and will generate periodic<br>IRQs to indicate whether the PCM data is needed<br>or available when transcoding. |

| 1     | Х     | Х     | 1     | Decoder is enabled and will generate periodic<br>IRQs to indicate whether the ADM data is needed<br>or available when transcoding. |

### DECODER MODE AND SETUP Register (\$D0)

Decimation Rate (by 4/8) (Bit 15) The decoder PCM filter functions as an interpolator for the DAC when PCM words are being received by the decoder and as a decimator when the decoder is receiving delta modulation. In the case where delta modulation is received, transcoded PCM values are available in the DECODE LINEAR PCM OUTPUT Register (\$D6) at the decimation rate. When PCM is received the device can be set to transcode to an ADM stream available in the DECODE ADM OUTPUT Register (\$DA) at the interpolated rate. A logic 1 sets the interpolation (decimation) rate to 4 (1/4<sup>th</sup> the bit rate). A logic 0 sets the interpolation (decimation) rate to 8 (1/8<sup>th</sup> the bit rate).

**PCM** Input

(Bits 14 - 13)

Select

| Bit 14 | Bit 13 | Selected PCM Input                            |

|--------|--------|-----------------------------------------------|

| 0      | Х      | PCM filter decimates ADM estimator output.    |

|        |        | PCM words available in register \$D6.         |

| 1      | 0      | PCM filter interpolates linear PCM input from |

|        |        | burst mode interface (RX DATA pin).           |

|        |        | This selection must be made in conjunction    |

|        |        | with the CODEC MODE CONTROL Register          |

|        |        | (\$70). Note that the burst interface expands |

|        |        | μLaw or Alaw signals to linear PCM prior to   |

|        |        | the PCM filter.                               |

| 1      | 1      | PCM filter interpolates linear PCM input from |

|        |        | C-BUS interface via the DECODE LINEAR         |

|        |        | PCM INPUT Register(\$D7).                     |

Allows selection of the input to the PCM rate converting filter.

If PCM filter interpolates, the decoder can digitally transcode a PCM signal to ADM. If PCM filter decimates, the decoder can digitally transcode an ADM signal to PCM.

ADM Input Select (Bits 12 – 11)

| Bit 12 | Bit 11 | Selected ADM Input                                                                                                                                                                                                                                                                                                     |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0      | ADM decoder input from the RX DATA pin.                                                                                                                                                                                                                                                                                |

|        |        | (Normal mode operation).                                                                                                                                                                                                                                                                                               |

| 0      | 1      | ADM decoder gets input from C-BUS via the DECODE ADM INPUT Register (\$D8). This could be used to force in an idle pattern or to                                                                                                                                                                                       |

|        |        | play out an arbitrary stored signal.<br>(Alternate ADM input operation).                                                                                                                                                                                                                                               |

| 1      | X      | ADM input from digital feedback. When ADM<br>input comes from digital feedback it will<br>transcode from PCM to ADM. PCM filter<br>must be set to interpolate. In this mode the<br>analog interface can be powered down since<br>all signal processing is done digitally.<br>(PCM to ADM transcoding input operation). |

| Decoder Output |               | Bit 10  | Bit 9   | Selected Decoder Output                     |

|----------------|---------------|---------|---------|---------------------------------------------|

| Select         |               | 0       | 0       | ADM estimator output drives decoder output. |

| (Bits 10 – 9)  |               | 0       | 1       | ADM estimator output summed with PCM        |

|                |               |         |         | interpolation filter output drives decoder  |

|                |               |         |         | output. The ADM and PCM signals can be      |

|                |               |         |         | input from any combination of RX DATA pin   |

|                |               |         |         | and C-BUS input registers.                  |

|                |               | 1       | 0       | Direct PCM test mode.                       |

|                |               | 1       | 1       | Interpolated PCM output.                    |

| Reserved       | This bit is r | eserved | and sho | uld be set to a logic 0.                    |

(Bit 8)

| Decoder VAD<br>Decay Time    | Allows selection of the Voice Activity Detector decay time constant. |           |           |            |                                |

|------------------------------|----------------------------------------------------------------------|-----------|-----------|------------|--------------------------------|

| Constant                     |                                                                      | Bit 7     | Bit 6     | Bit 5      | Decay Time Constant (ms),      |

| (Bits 7 – 5)                 |                                                                      |           |           |            | Bit Rate in kbps               |

| . ,                          | -                                                                    | 0         | 0         | 0          | 128/(Bit Rate)                 |

|                              | -                                                                    | 0         | 0         | 1          | 256/(Bit Rate)                 |

|                              | -                                                                    | 0         | 1         | 0          | 512/(Bit Rate)                 |

|                              |                                                                      | 0         | 1         | 1          | 1024/(Bit Rate)                |

|                              | -                                                                    | 1         | 0         | 0          | 2048/(Bit Rate)                |